本文将分享存内浮点计算前沿论文——ISSCC 2024《34.8 A 22nm 16Mb Floating-Point ReRAM Compute-in-Memory Macro with 31.2TFLOPS/W for AI Edge Devices》。下面将从文章基本信息、创新点解析、芯片测试与对比及未来展望四个部分展开介绍。

- 基本信息介绍

1、研究背景及面临的挑战

AI边缘设备是专为在本地处理数据而设计的智能设备,能够在靠近数据源的地方执行计算任务,从而降低延迟并提高响应速度。这些设备利用深度学习和机器学习算法,将数据处理能力从云端转移到设备本地,工作原理包括传感器数据采集、模型推理和反馈控制。AI边缘设备的常见应用场景包括智能家居(如语音助手和安全监控)、工业自动化(实时监控和预测维护)、智能交通(自动驾驶车辆的实时决策)等,这表明AI边缘设备在减少数据传输需求和提升隐私保护方面的潜力。AI边缘设备通常采用专用的硬件加速器作为核心处理器,如FPGA、GPU或定制的加速器架构,以达到高性能和低功耗的实际需求。通过研究更高效的AI边缘处理器,社会能够获得更为智能的解决方案,加速推动各行业的数字化转型。

当前AI边缘处理器仍然存在许多问题。AI 边缘设备需要高精度计算才能在实际应用中进行准确推理,同时又保持高能效和低待机功率,以最大限度地延长电池寿命。因此AI边缘处理器往往采用片上非易失性存储器,以便在断电期间存储权重数据。其次,存储器的带宽和延迟影响了数据传输速率,限制了处理器在大规模数据处理时的效率。此外,面对不断增加的AI模型复杂性,如何有效管理和更新模型以适应新的应用场景也是一个关键挑战。

2、本文工作介绍

面向上述问题,本文提出了以下创新点:

- 提出了KWPA混合计算架构方案,针对ReRAM计算中权重处理做出相应优化,以提高计算精度和速度。

- 考虑到输入数据的位宽问题,文章通过多位输入压缩(RS-MIC)方案对输入数据进行无损压缩,提升数据传输的带宽并降低延迟。

- 开发了一种双符号位(HF-DSB)权重编码方案,使得处理器能够根据应用需求自动调整模型参数,从而提升适应性和灵活性。

3、研究团队

本篇论文的作者来自存储器设计实验室,该实验室属于国立清华大学并由张孟凡教授指导研究。实验室的研究方向包括先进存储器设计、涵盖非易失性、低电压、忆阻器等多个方向。国立清华大学成立于1911年,起初是清华学校的一部分,之后在台湾发展成为一所综合性的研究型大学。该校在工程、自然科学和计算机科学领域有良好声望,与多个国际高校和研究机构保持紧密的合作关系。

- 创新点解析

- 核级权重预对齐方案(KWPA)

KWPA方案旨在解决在非易失性AI边缘处理器中,权重预对准期间因数据截断而造成的精度损失。KWPA通过引入动态调整机制和高精度计算,确保在数据处理的每个阶段尽量保证权重有效精度,从而保持整体推理效率。

图1 KWPA的浮点数处理流程

KWPA的预处理流程可以分为几个关键步骤,如图1所示:

1)权重提取动态调整:从训练好的AI模型中提取出权重后的量化过程中,KWPA使用动态调整算法实时监测权重的分布情况,调整量化参数,确保在量化时尽量减少重要信息的丢失。

2)量化权重存储:KWPA采用分段量化的方法,将权重分为多个区间,并根据每个区间实现相应的量化,以减少截断误差。量化后的权重被存储在非易失性存储器中。

3)输入数据预对准:前两步已经将整个神经网络存储在片上,所以权重可以离线预加载。KWPA通过将每个核的最大指数指定为核共享指数(EK),在离线时预对齐所有的浮点数权重。然后,KWPA基于指数差对每个权重的符号和尾数进行对齐从而生成权重PA-MK,由此避免了浮点数的数据截断问题。

4)MAC过程:在推理阶段,KWPA将量化后的权重加载到计算单元中。通过读取ReRAM阵列的一行来检索EK,并将其存储在指数处理电路的寄存器中。在MAC操作过程中,输入预对齐电路以16位浮点数格式提取输入,并将输入组的最大指数指定为输入共享指数(EIN),以生成P位的PA-MIN。PA-MIN被发送到ReRAM阵列,与PA-MK进行MAC操作。得到的MAC值经过指数处理,重新转换为32位浮点数的输出格式。

在电路实现上,KWPA的核心部分是分段量化单元,负责将权重分为多个区间并进行相应的量化处理。通过硬件实现的分段量化,可以减少量化过程中的计算复杂度和时间消耗。论文中针对量化部分设计了存储接口,使得量化后的权重能够快速写入和读取非易失性存储器。这一接口支持多种存储格式,以适应不同的应用需求。KWPA方案通过精确的动态调整和高效的计算流程,成功地减少了因权重预对准导致的精度损失,提升了非易失性AI边缘处理器的推理性能。这一方案在设计上不仅考虑了计算效率,还注重了能效,适用于边缘计算场景。

- 重新安排的多位输入压缩方案(RS-MIC)

RS-MIC专为优化基于ReRAM的乘加(MAC)操作而设计,如图2所示。该方案的主要目的是减少ReRAM中执行MAC操作所需的计算周期数,从而实现更快的处理速度和更高的能效。

图2 RS-MIC的示意图

RS-MIC的核心思想在于通过输入数据的重调度和压缩,减少ReRAM阵列中的活动周期。具体来说,通过将多比特的输入数据分为多组的2b数据并根据其二进制值(如'11', '10', '01', '00')进行分类,同时将非零值重新编码为更少的比特,这一过程显著降低了操作的复杂度。例如,二进制值'11','10' 和 '01' 被压缩为单比特'1',而'00'则被完全忽略,不参与后续的MAC操作。这样的处理方式使得原本需要多周期完成的操作能够在单一周期内完成,显著提升了效率。

在具体实施方面,RS-MIC技术首先将权重分割并存储在ReRAM的相邻行中,允许系统在每个MAC操作周期中并行访问多个权重,实现高效的数据处理。输入数据的重调度和压缩进一步减少了传输和处理的复杂性,使得压缩后的输入可以同时对多个权重行进行操作。这种并行计算能力大幅提升了处理速度。最终,通过特定的累加器将所有并行处理的结果按照其原始位置和重要性进行合并和累加,以得到最终的MAC结果。

RS-MIC方案的优势显而易见。它不仅大幅提高了计算速度,通过将多周期操作压缩到单个周期内完成,还显著减少了计算延迟,这对于要求实时性的应用尤为重要。同时,通过并行处理和减少计算周期数,不仅提高了处理速度,也优化了能源消耗,增强了系统的能效比。此外,这种方法的灵活性使其可以适配多种不同位宽的权重和输入数据,以满足更多的应用场景和需求。

- HRS 支持的双符号位权重编码方案(HF-DSB)

HRS支持的双符号位权重编码方案(HF-DSB)是一项创新的技术,专为优化阻变随机存取存储器(ReRAM)中的乘加运算(MAC)而设计,如图3所示。该方案通过减少在ReRAM阵列中访问低阻态(LRS)单元的数量来降低电流消耗,从而不仅提高了能效和系统性能,还保持了权重值的不变性,确保了计算操作的准确性。

图3 HF-DSB的概念与操作

HF-DSB方案的核心在于对传统二进制补码格式中的权重值进行特定的转换,目的是减少活跃的LRS单元数量。这种转换通过计算X[N]×2N+1,其中 N是发生转换的列位置。此过程涉及将特定的权重位从幅度位转化为符号位,并赋予其负的位置值。例如,在处理 X0= -1的情况时,其二进制补码 "11111111" 通过选定第2位以添加转换项 1×22+1(00001000),被转换为 "00000111" = "11111111" +"00001000",从而将多个LRS状态的位转换为HRS状态。而在 X1 = -103的例子中,由于转换位(第2位)的值为0,权重保持不变,显示为原补码 "10011001"。

在ReRAM实施中,HF-DSB格式的权重及其相应的FLAG_DSB被编程到阵列中。FLAG_DSB是一个关键的标志位,用于在MAC操作期间指示是否应用了HF-DSB转换。在MAC操作开始前,FLAG_DSB从ReRAM阵列中检索并存储在寄存器中,确保在MAC操作期间能够根据权重的位置值和符号正确处理输入数据和权重,从而生成准确的乘加运算值(pMACVMIC)。

- 芯片测试与对比

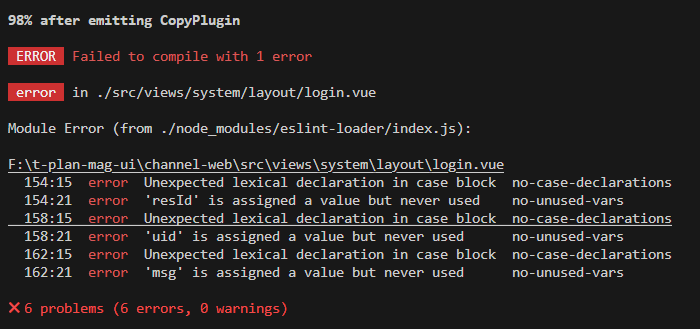

图4 Shmoo图以及对比分析

本文所提出的用于浮点运算的基于ReRAM的存算一体芯片在22nm CMOS工艺下制备而成,其总面积为8.2mm2,存储容量为16Mb且支持0.7-0.8V的供电电压。该芯片的输入精度为FP16或BF16,权重精度为FP16或BF16,输出精度为FP32。在供电电压为0.8V、输入精度为BF16时,芯片的吞吐量为0.86 TFLOPS,能效为31.2 TFLOPS/W;在供电电压为0.8V、输入精度为FP16时,芯片的吞吐量为0.78 TFLOPS,能效为28.7 TFLOPS/W。图4显示了芯片的Shmoo测试,结果显示芯片具有较好的稳定性且在0.8V供电电压下具有5ns的低延时,由此也验证了作者提出的RS-MIC解决方案是可行的。

此外,作者在BF16精度下使用CIFAR - 100数据集训练的ResNet20模型模拟了芯片的性能。如图5所示,与逐层权重预对齐相比,K - WPA将权重预对齐过程中的截断数据量减少了1.96 ~ 2.47倍;RS - MIC相比于传统的数字比特串行多比特输入和传统的零跳比特串行多比特输入,MAC操作循环次数分别减少了4.73和1.78倍;采用HF - DSB权重表示,ReRAM阵列的平均能耗降低了1.31×。当综合考虑这三个方案时,它们共同将CIM核的能效提高了1.82×。如图4所示,与以往采用INT8输入、INT8权重和INT24输出的工作相比,本文实现了FoM的1.86×改进。

图5 所提出方案的模拟结果

从本文的芯片测试结果可以看出,K-WPA方案保持了一定的精度同时减少了数据量的存储,RS-MIC方案减少了MAC操作的延时与能量消耗,HF-DSB方案减少了ReRAM单元的低组态状态以此降低了ReRAM阵列的电流消耗,以上三个方案的共同协作为非易失性的AI边缘处理器提供了新的解决方案。

四、未来展望

未来,存储技术的发展前景广阔,将迎来一系列突破性进展。首先,在存储器架构优化方面,通过进一步优化ReRAM阵列结构,可以显著提升并行计算能力。研究新型存储单元设计将大幅提高存储密度和计算效率,满足日益增长的计算需求。其次,精度与效率的平衡也是未来研究的重点领域之一。开发更先进的量化技术,将在保持高精度的同时显著减少数据传输,;研究动态精度调整机制,使计算精度能够根据具体任务需求灵活调整;探索新的权重编码方案进一步优化存储空间的利用和计算效率。最后,异构集成是存储技术发展的另一重要方向。通过研究ReRAM与其他存内计算技术(如SRAM、MRAM等)的异构集成,可以充分发挥不同存储技术的优势,形成更强大的计算系统。例如,SRAM的高速读写特性可以与ReRAM的高存储密度特性相结合,形成一种兼具速度和容量的混合存储架构。

总之,通过在存储器架构优化、精度与效率平衡以及异构集成等方面的深入研究和探索,未来的计算系统将变得更加高效、灵活和强大。这些进展不仅将推动人工智能和大数据处理的发展,还将为广泛的应用场景提供坚实的技术基础。未来的存储技术将继续突破现有瓶颈,开创计算与存储一体化的新纪元,为信息技术的持续创新提供强有力的支持。