目录

一、信号特征

二、组合逻辑电路和时序逻辑电路

1、组合逻辑电路

2、时序逻辑线路

三、信号转换

1、数字集成电路的分类

2、常用电平接口技术

四、可编程逻辑器件

flechazo![]() https://www.zhihu.com/people/jiu_sheng

https://www.zhihu.com/people/jiu_sheng

小柴冲刺嵌入式系统设计师系列总目录![]() https://blog.csdn.net/qianshang52013/article/details/139975720?spm=1001.2014.3001.5501

https://blog.csdn.net/qianshang52013/article/details/139975720?spm=1001.2014.3001.5501

一、信号特征

根据电路是否具有存储功能,将逻辑电路划分为两种类型:

-

组合逻辑电路

-

不含存储功能,它的输出值仅取决于当前的输入值

-

时序逻辑电路

-

含存储功能,它的输出值不仅取决于当前输入状态,还取决于存储单元中的值

二、组合逻辑电路和时序逻辑电路

1、组合逻辑电路

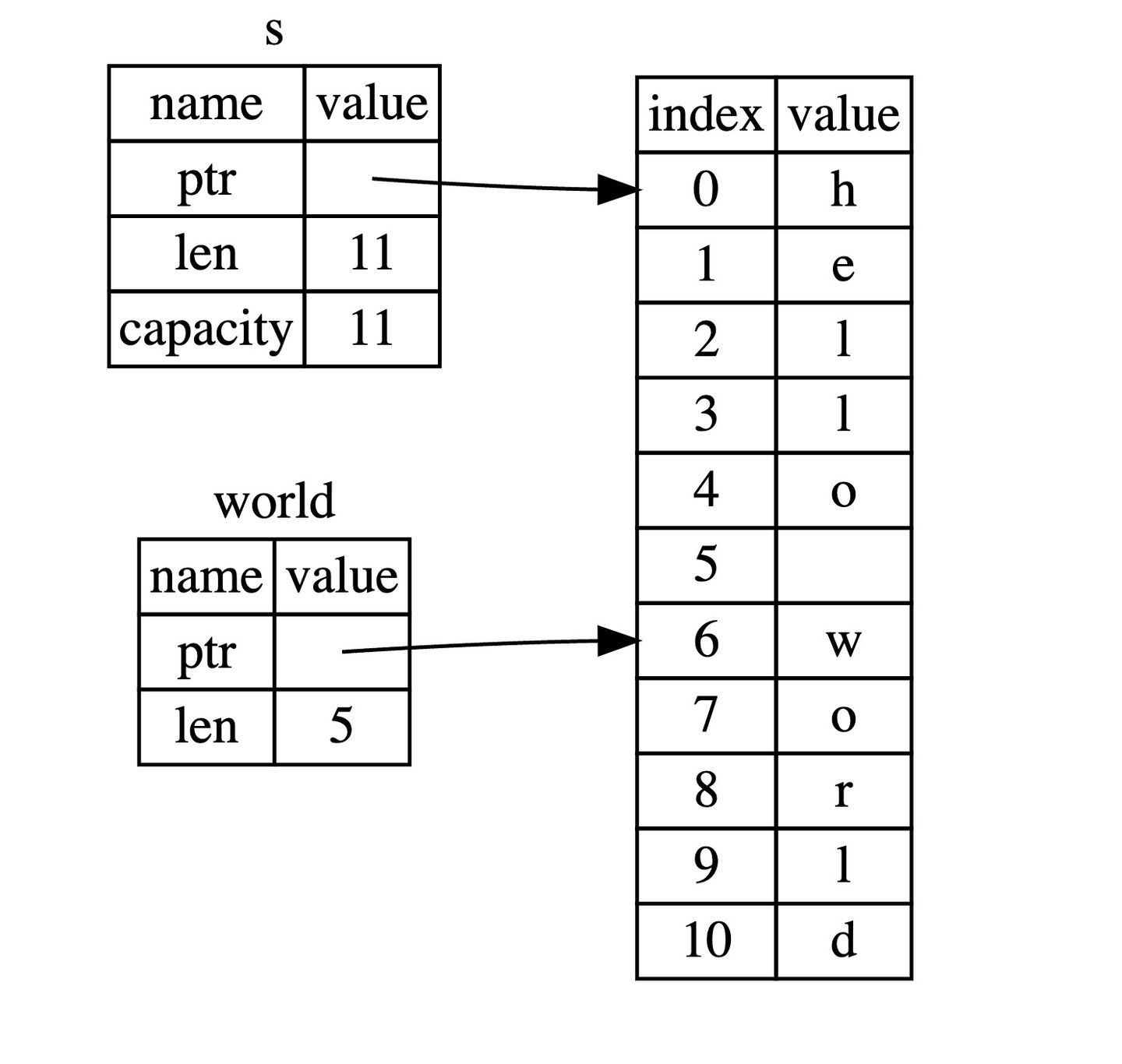

组合逻辑电路一般由门电路组成,不含记忆元器件,输入与输出之间无反馈。

常用的组合逻辑电路有:

-

译码器

-

多路选择器

真值表

通常真值表能够完全描述任何一种组合逻辑函数。

布尔代数

布尔代数中有三种典型的操作符:

-

OR 或 + |

-

AND 与 * &

-

NOT 非 — !

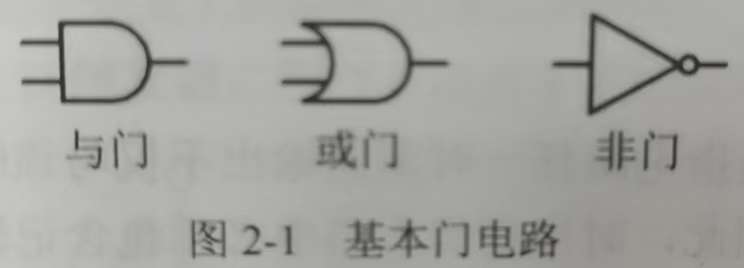

门电路

添加图片注释,不超过 140 字(可选)

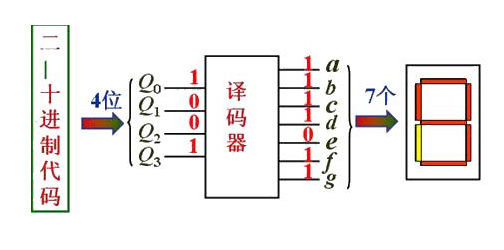

译码器

译码器(Decoder)又称解码器是一种电子设备或电路,它用于将输入的数字信号、编码或模式转换为特定的输出信号、解码或信息。相对的是编码器。

添加图片注释,不超过 140 字(可选)

数据选择器和数据分配器

数据选择器又称多路开关,它是以与或门,与或非门为主的电路。

-

它可以在选择信号的作用下,从多个输入通道中选择某一个通道的数据作为输出。

-

可以实现任意组合逻辑函数,四选一的数据选择器可以实现三个变量的组合逻辑函数,2n个数据输入的多路选择器可以实现n+1个变量的组合逻辑函数

数据分配器又称多路分配器,它有一个输入端和多个输出端,其逻辑功能是将一个输入端的信号送至多个输出端的某一个,简称DMUX,作用与MUX正好相反。

-

数据分配器的核心部分实际上是一个带有是能端的全译码器,可以把数据分配器理解为是输出受X控制的译码器

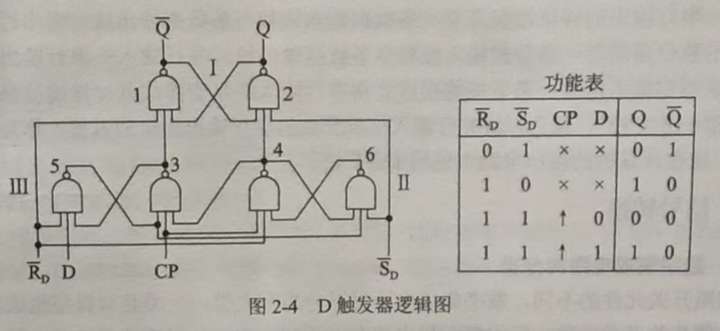

2、时序逻辑线路

所谓时序逻辑电路,是指电路任一时刻的输出不仅与该时刻的输入有关,而且还与该时刻电路的状态有关。因此,时序逻辑电路中必须含有记忆元器件。触发器是构成时序电路的基础。常用的有寄存器和计数器等。

时钟信号

时钟频率(clock frequency,CF)是时钟周期的倒数。通过高低电平的边沿触发。上升沿/下降沿

同步是时钟控制系统中的主要制约条件。

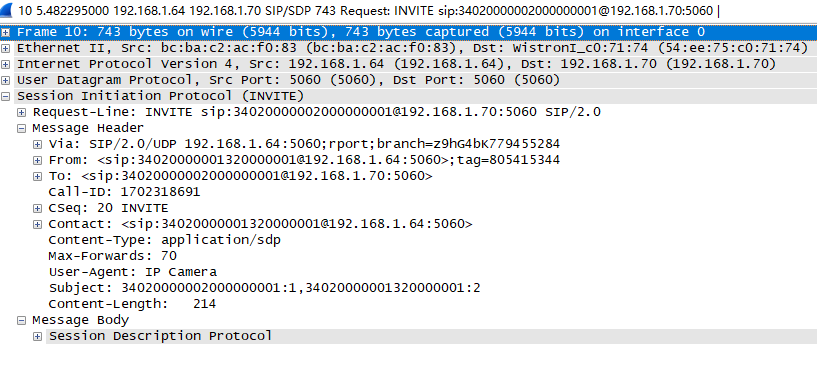

触发器

按照时钟控制方式分类

-

电位触发

-

边沿触发

-

主从触发

按功能分类

-

RS型

-

D型

-

JK型

添加图片注释,不超过 140 字(可选)

边沿触发器在CP=1期间来到的数据,必须延迟到该CP过后的下一个CP边沿来到时才会被接收,因此又称延迟型触发器,在CP正跳变(对正边沿触发器)意外期间出现在D端的数据和不干扰不会被接收,因此有很强的数据抗干扰能力。

至于电位触发器,只要E为约定电平,数据到之后就立即接收。

触发器开关的特性。描述触发器的参数有很多

-

描述传输延迟的参数

-

描述各输入波形宽度要求的参数

-

描述各输入波形之间时间配合要求的参数

如果在使用中不满足要求,电路就不能正常工作。

寄存器与移位器

寄存器主要用来接受信息、寄存信息、传送信息

通常采用并行输入-并行输出的方式

寄存器中除具有若干触发器以外,还有门电路构成的控制电路,来保证信息的正确接受、发送和清除。

在时钟信号控制下,将所有寄存的信息向左或向右移位的寄存器曾为以为寄存器

三、信号转换

1、数字集成电路的分类

按照开关元件的不同,数字集成电路可以分为两大类:

-

双极型集成电路

-

采用晶体管作为开关元件,管内参与导电的有电子和空穴两种极性的载流子。

-

金属氧化物半导体(Metal-oxide Semiconductor)MOS集成电路

-

采用绝缘栅场效应晶体管做开关元器件,管子内部只有一种载流子,电子或空穴参与导电,因此又称单极型集成电路。

晶体管-晶体逻辑电路(Transistor-Transistor Logic, TTL)是目前双极型数字集成电路中用得最多的一种。

它具有比较快的开关速度、比较强的抗干扰能力以及足够强大的输出幅度,并且带负载能力较强,所以得到了广泛的应用

双极型数字集成电路

-

TTL

-

二极管-三极管逻辑(Diode-Transistor Logic,DTL)

-

高阈值逻辑(High Threshold Logic,HTL)

-

发射极耦合逻辑(Emitter Coupled Logic,ECL)

-

优点:工作在非饱和状态,有较高的工作速度,输出阻抗低,带负载能力强,电路内部开关噪声低,使用方便灵活

-

缺点:噪声容限低,电路功耗大,输出电平的稳定性较差

-

主要用于高速、超高速数字系统中。

-

集成注入逻辑(Integrated Injection Logic,IL)

MOS管

-

PMOS

-

问世较早,速度低,很少使用。

-

NMOS

-

集成电路速度稍高,且直流电源电压较低,在工艺上可以制造出开启电压较低的器件

-

CMOS

-

静态功率极低,工作速度较高,抗干扰能力强,使用广泛。

2、常用电平接口技术

ECL的特点是速度快,但抗干扰性能差,功耗也高。

TTL的应用广泛,成本低廉,有多种类型可供选择。

CMOS功耗最低,抗干扰性能优良,不仅适用于中、小规模集成电路,而且在大规模集成组件中应用也很普遍。

电平转换

-

TTL与ECL

-

TTL->ECL

-

ECL->TTL

-

TTL与CMOS

-

TTL->CMOS

-

CMOS->TTL

四、可编程逻辑器件

现场可编程门阵列Field Programmable Gate Array, FPGA

早期的可编程逻辑器件只有可编程只读存储器PROM、紫外线可擦除只读存储器EPROM、电可擦除只读存储器EEPROM

其后出现了一类结构上稍微复杂的可编程芯片,可编程器件PLD,它能够完成各种数字逻辑功能。典型的PLD由一个与门和一个或门阵列组成。

这一阶段的产品主要有可编程阵列逻辑 Programmable Array Logic ,PAL和通用逻辑阵列Generic Array Logic,GAL

![[vulnhub] Prime 1](https://i-blog.csdnimg.cn/direct/b8e8cc8f549847fb9d9b18af89423380.png)