本文主要记录DDR4与DDR3有较大差异的点。

2.DDR4管脚

| 信号 | 类型 | 描述 |

| C0,C1,C2 | input | chip IDchip ID仅用于通过TSV(硅通孔)选择3DS堆叠组件的2层、4层、8层高堆栈中的每一片,chip ID被视为命令代码的一部分。 |

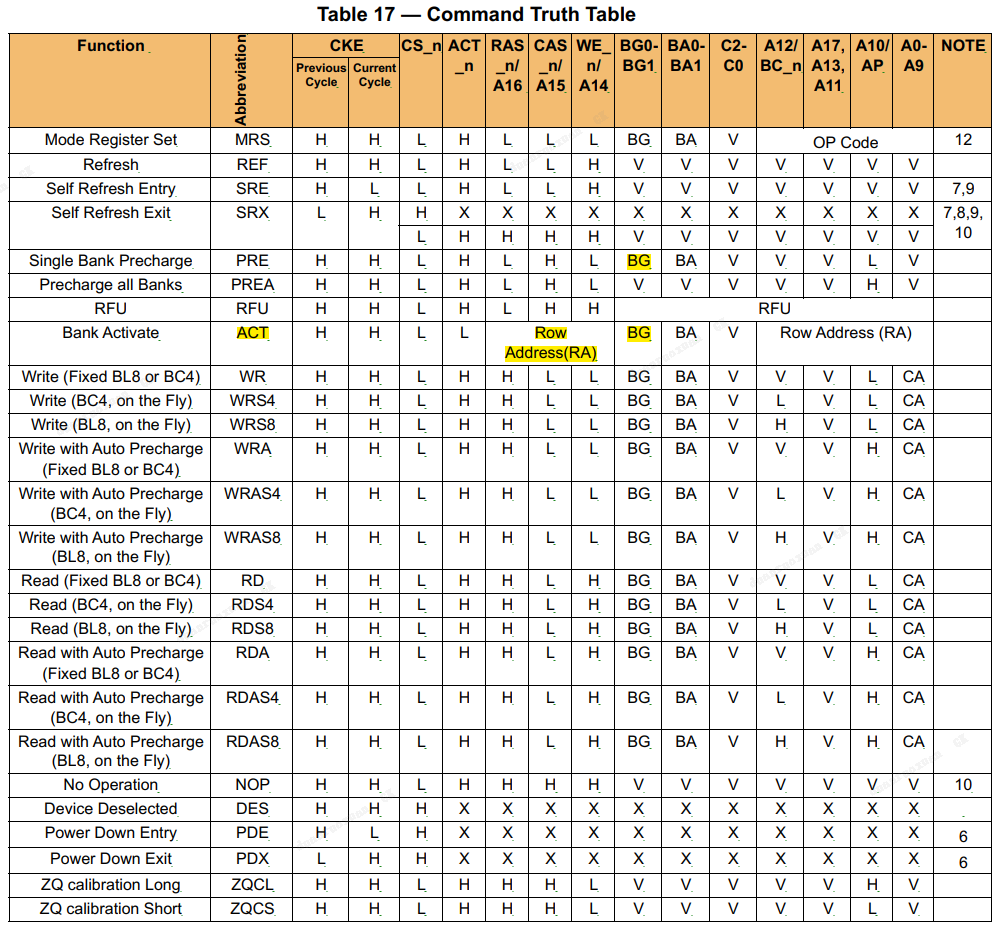

| ACT_n | input | 激活命令输入:低有效。ACT_n定义与CS_n一起输入的激活命令。RAS_n/A16、CAS_n/A15和WE_n/A14的输入将被视为行地址A16、A15和A14。 |

| RAS_n/A16. CAS_n/ | input | 命令输入:RAS_n/A16、CAS_n/A15和WE_n/A14(与CS_n一起)定义输入的命令。这些引脚具有多重功能。例如,当ACT_n为低电平时,它们用于寻址(如A16、A15和A14),但当ACT_n为高电平时,它们作为读取、写入和其他命令的命令引脚,这些命令在命令真值表中定义。 |

| DM_n/DBI_n/ | inout | 输入数据掩码和数据总线取反:DM_n是用于写入数据的输入掩码信号。当在写入访问期间DM_n与输入数据同时采样为低电平时,输入数据将被屏蔽。DM_n在DQS的两个边沿上采样。通过在MR5中的模式寄存器A10、A11、A12设置,DM与DBI功能复用。对于x8设备,DM或TDQS功能通过MR1中的模式寄存器A11设置启用。DBI_n是一个输入/输出信号,用于标识存储/输出的是原始数据还是取反后的数据。如果DBI_n为低电平,数据将在DDR4 SDRAM内部取反后存储/输出;如果DBI_n为高电平,数据将不会取反。TDQS仅支持x8配置。 |

| BG0 - BG1 | input | 存储体组输入:BG0 - BG1定义激活、读取、写入或预充电命令将应用于哪个bank group。BG0还决定在MRS(模式寄存器设置)周期中访问哪个模式寄存器。x4/x8配置具有BG0和BG1,而x16配置仅有BG0。 |

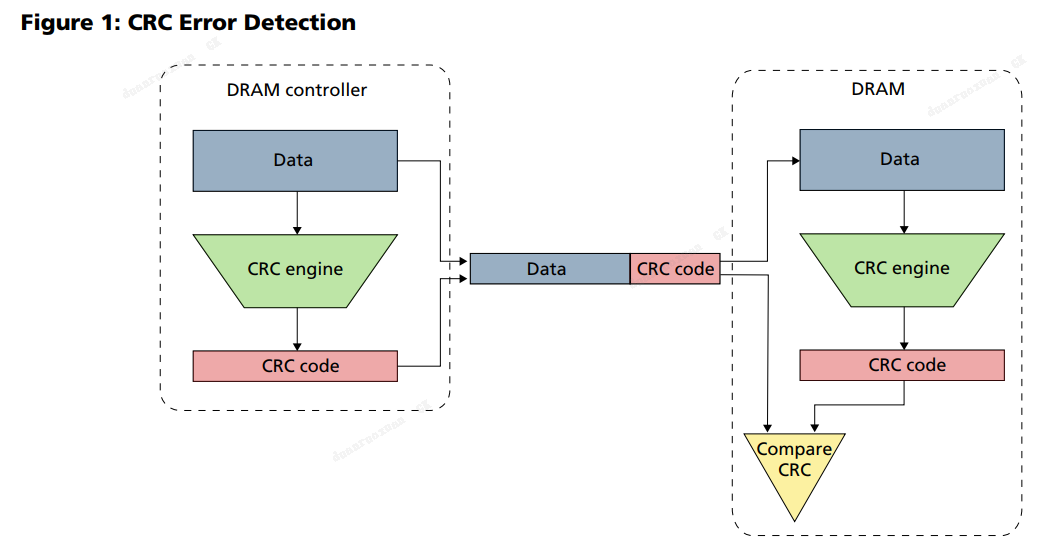

| DQ | inout | 数据输入/输出:双向数据总线。如果通过模式寄存器启用了CRC,则在数据突发结束时将添加CRC码。在测试模式下,通过模式寄存器设置MR4 A4=高电平时,DQ0~DQ3中的任何一个DQ可能会指示内部Vref电平。在此模式下,RTT值应设置为高阻抗(Hi-Z)。有关使用哪个DQ的详细信息,请参阅供应商提供的具体数据手册。 |

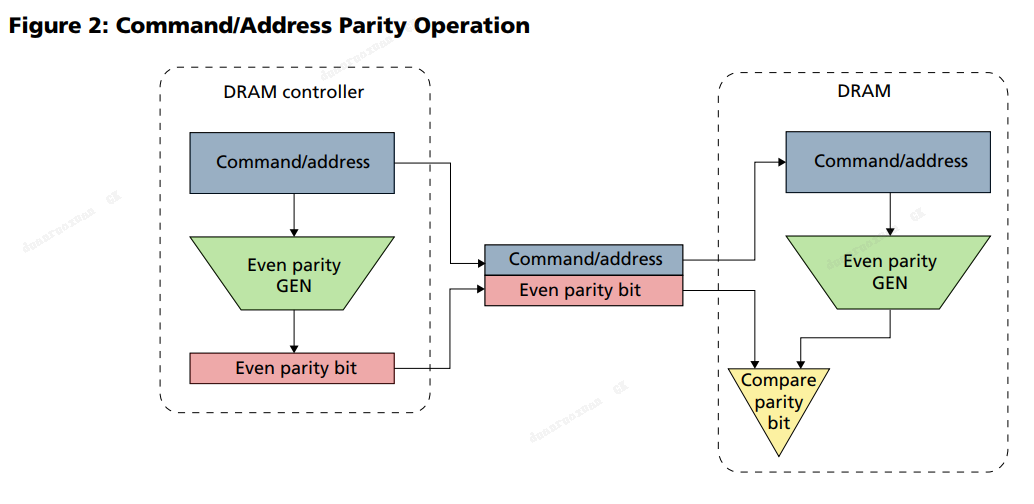

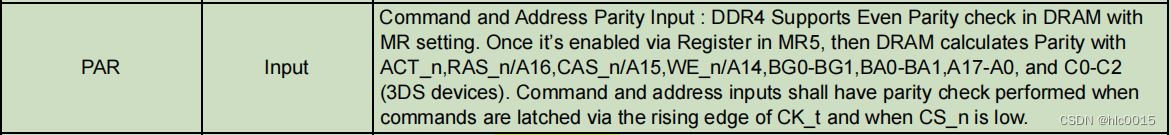

| PAR | input | 命令和地址奇偶校验输入:DDR4支持在DRAM中进行偶数奇偶校验,通过模式寄存器设置进行配置。一旦通过MR5中的寄存器启用,DRAM将使用ACT_n、RAS_n/A16、CAS_n/A15、WE_n/A14、BG0-BG1、BA0-BA1、A17-A0以及C0-C2(3DS设备)计算奇偶校验。当命令通过CK_t的上升沿锁存并且CS_n为低电平时,命令和地址输入将进行奇偶校验。 |

| alert | inout | alert:该引脚具有多种功能,如CRC错误标志和命令与地址奇偶校验错误标志作为输出信号。如果发生CRC错误,Alert_n会在一个时间间隔内变为低电平,然后恢复为高电平。如果发生命令地址奇偶校验错误,Alert_n会在较长时间内保持低电平,直到DRAM内部的恢复事务完成。在连接测试模式下,该引脚作为输入信号使用。是否使用此信号取决于系统要求。如果未连接此信号,ALERT_n引脚必须在电路板上接到VDD。 |

| TEN | input | 连接测试模式启用:对于x16设备是必需的,对于x4/x8且密度等于或大于8Gb的设备是可选输入。此引脚为高电平时,将启用连接测试模式操作,并与其他引脚一起工作。它是一个CMOS电平信号,高电平和低电平分别为VDD的80%和20%。是否使用此信号取决于系统需求。此引脚可能通过一个弱下拉电阻被DRAM内部拉低至VSS。 |

| NC | 目前没用 |

3.功能描述

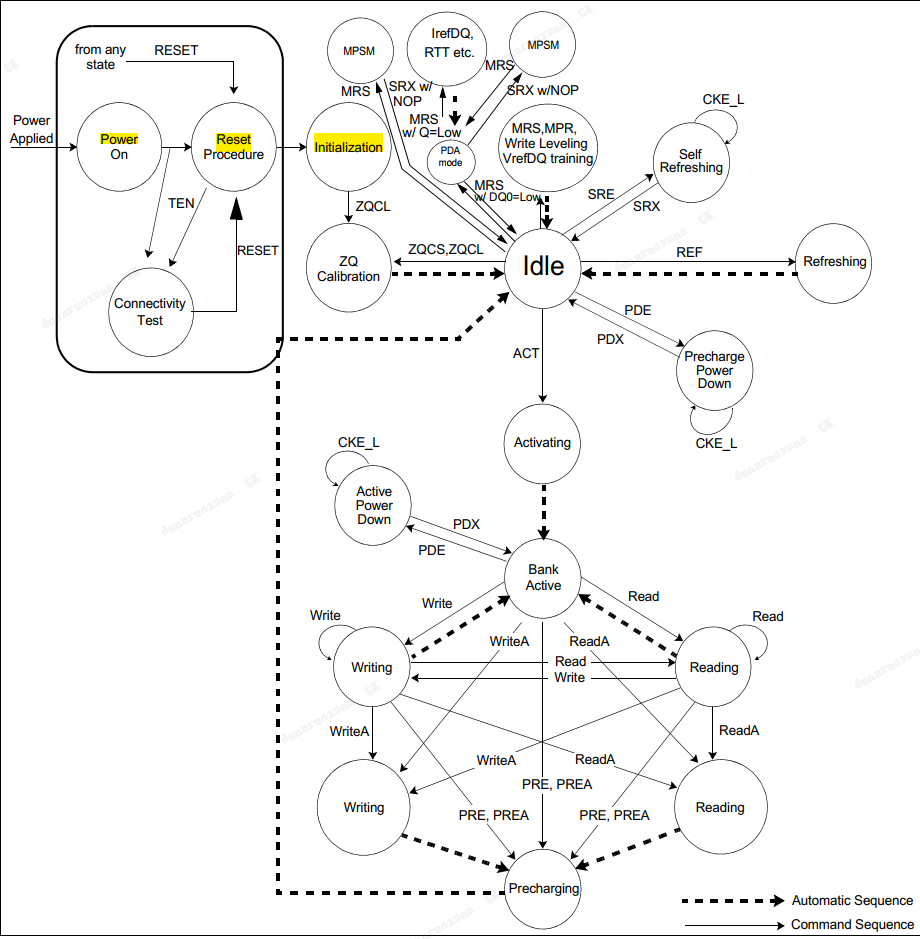

3.1简化状态图

3.2基本功能

DDR3与DDR4的差异在于有bank group。

8个bank分为两个group。

3.3 复位和初始化程序

为了确保DDR4 SDRAM在上电和复位初始化过程中正常工作,需要为以下模式寄存器(MR)设置定义默认值,以防止DRAM功能异常。

- Gear Down Mode (MR3 A[3]): 0 = 1/2速率

- Per DRAM Addressability (MR3 A[4]): 0 = 禁用

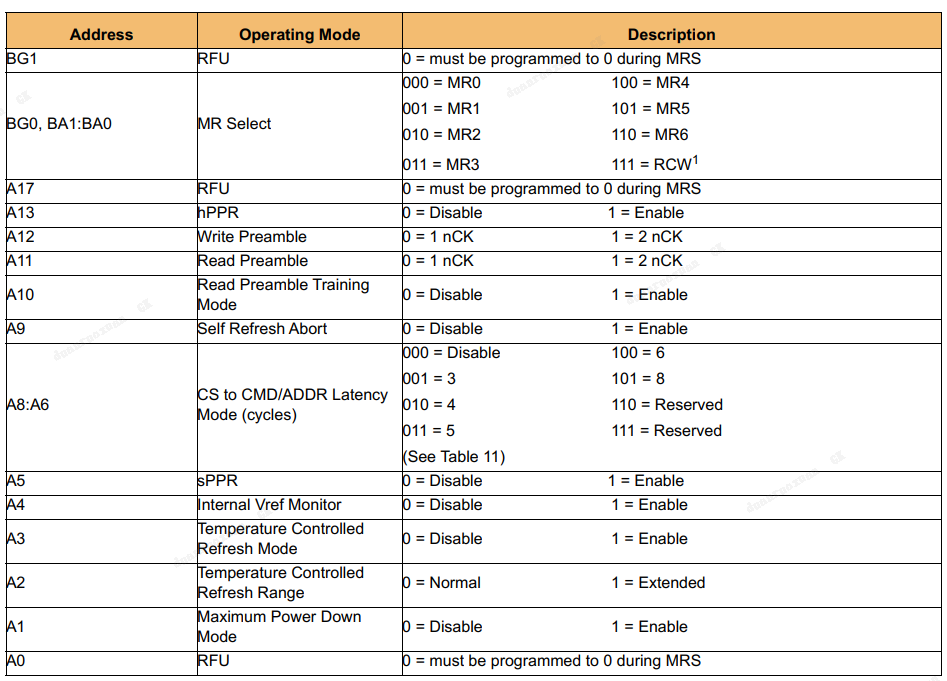

- Max Power Saving Mode (MR4 A[1]): 0 = 禁用

- CS to Command/Address Latency (MR4 A[8:6]): 000 = 禁用

- CA Parity Latency Mode (MR5 A[2:0]): 000 = 禁用

- Hard Post Package Repair Mode (MR4 A[13]): 0 = 禁用

- Soft Post Package Repair Mode (MR4 A[5]): 0 = 禁用

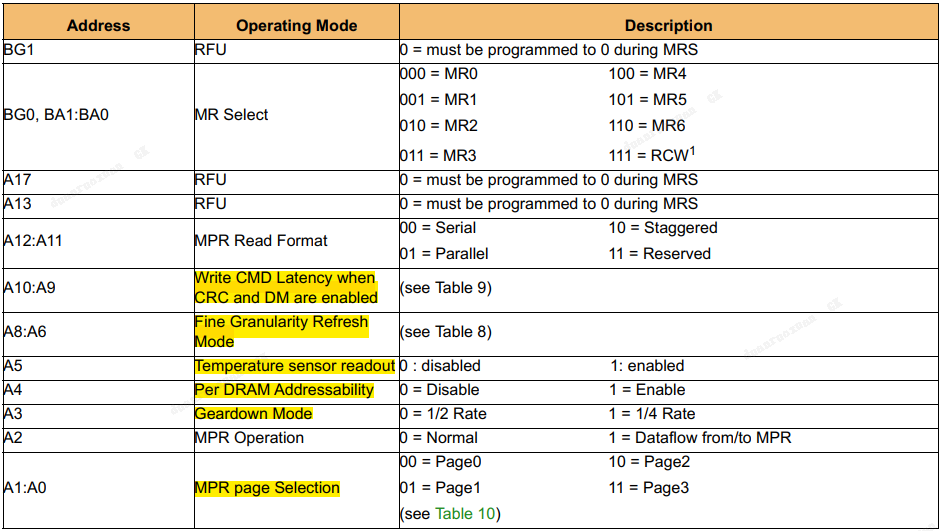

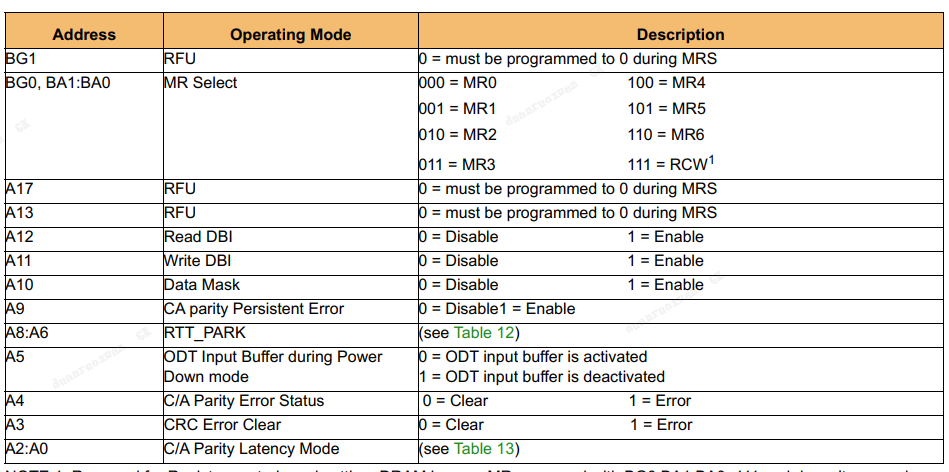

3.5 Mode Register

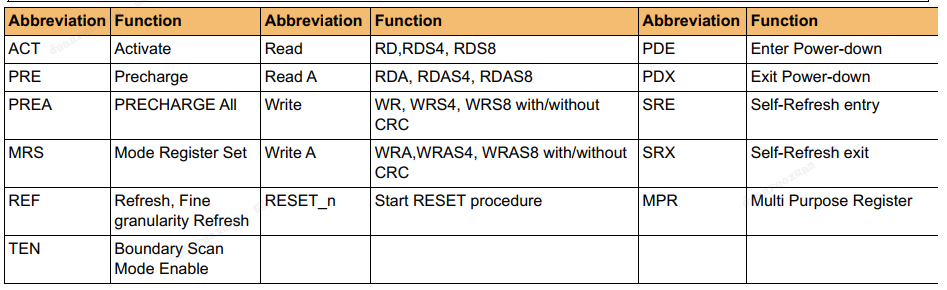

MR0

**注释1**:保留用于寄存器控制字设置。DRAM会忽略BG0、BA1和BA0=111的MRS命令,并且不会做出响应。当输入RFU(保留)模式寄存器代码设置时,DRAM的操作是未定义的。

MR1

与DDR3一样。

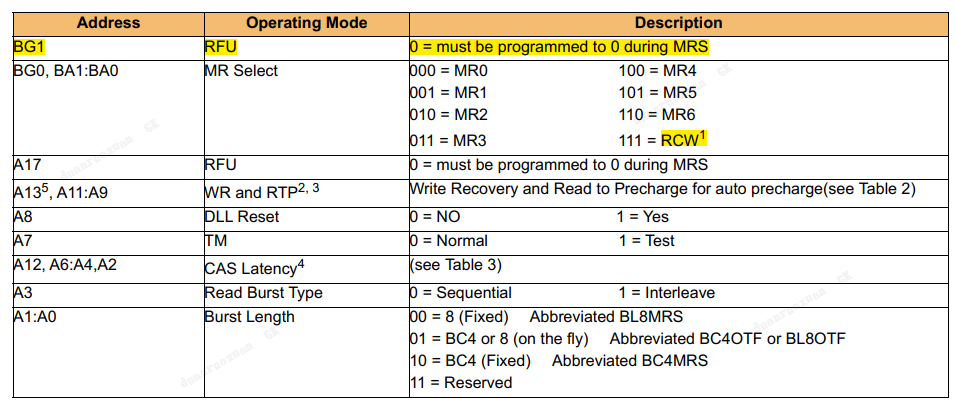

MR2

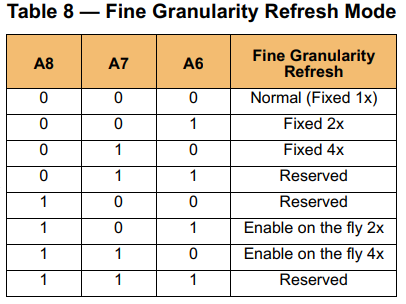

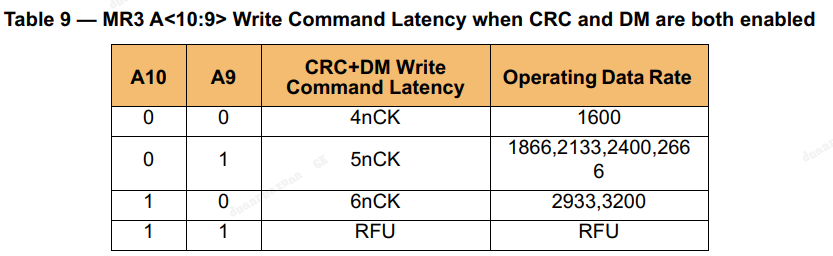

MR3

MR4

MR5

MR6

DDR命令描述与操作

4.1命令真值表

4.1CKE真值表

4.3BL

4.3.1启用CRC的BL8突发顺序

当在BL8(固定)模式下启用写CRC时,DDR4 SDRAM支持固定写突发排序 [A2:A1:A0=0:0:0]。

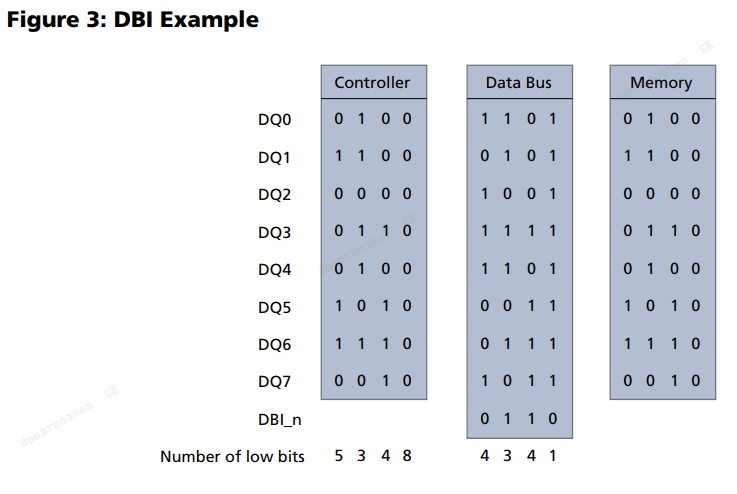

4.11 Data Mask(DM), Data Bus Inversion (DBI) and TDQS

DDR4 SDRAM支持在x8和x16 DRAM配置中使用数据掩码(DM)功能和数据总线反转(DBI)功能。x4 DDR4 SDRAM不支持DM和DBI功能。x8 DDR4 SDRAM支持TDQS功能,而x4和x16 DDR4 SDRAM不支持TDQS功能。

DM、DBI和TDQS功能通过一个标记为DM_n/DBI_n/TDQS_t的专用引脚支持。该引脚是DRAM的双向引脚。DM_n/DBI_n引脚在DDR4中支持VDDQ参考终端。TDQS功能不会驱动引脚上的实际电平。

DM、DBI和TDQS功能可以通过DRAM模式寄存器(MR)进行编程。MR位位置为MR1中的A11位和MR5中的A12

位。

- 写操作:可以启用DM或DBI功能,但不能同时启用两个功能。当DM和DBI功能都被禁用时,DRAM会关闭其输入接收器,并且不期望任何有效的逻辑电平。

- 读操作:仅应用DBI功能。当DBI功能被禁用时,DRAM会关闭其输出驱动器,并且不会驱动任何有效的逻辑电平。

- TDQS功能:当TDQS功能启用时,不支持DM和DBI功能。当TDQS功能被禁用时,DM和DBI功能可以按照下表30所述进行支持。当TDQS功能启用时,TDQS_t/TDQS_c引脚应用与DQS_t/DQS_c引脚相同的终端电阻功能。

启用DPI减少低电平数以实现低功耗。

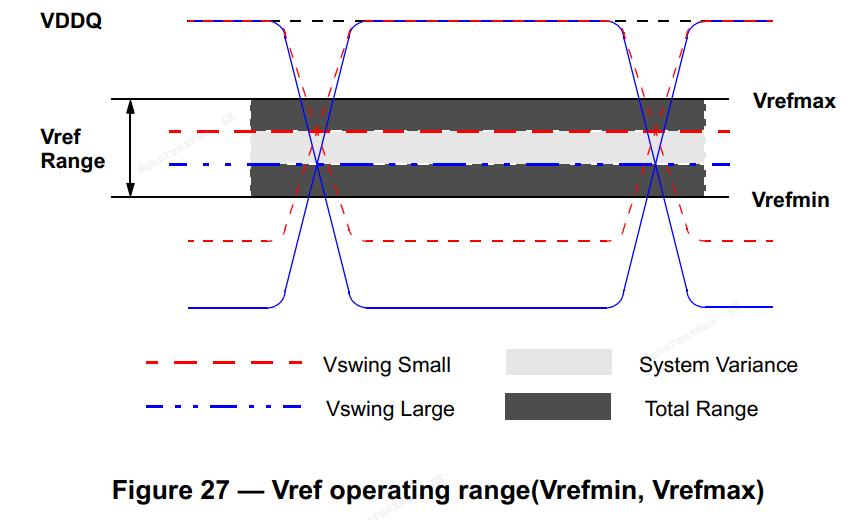

4.13 DQ Vref Training

用于眼图的训练(眼高,眼宽),VrefDQ电压值校正。

DRAM 内部 DQ Vref 规范参数包括工作电压范围、步长、Vref 步进时间、Vref 完整步进时间和 Vref 有效电平。

电压工作范围规定了 DDR4 DRAM 设备所需的最小 Vref 设置范围。最小范围由 Vrefmax 和 Vrefmin 定义,如下方的图 27 所示。

Vref 步长定义为相邻步之间的步长。Vref 步长范围为 0.5% VDDQ 到 0.8% VDDQ。然而,对于特定设计,DRAM 的 Vref 步长是该范围内的一个固定值。

Vref 设置容差是 Vref 电压相对于理想设定值的偏差,考虑了多次步进过程中累积的误差。Vref 设置容差不确定性有两个范围,其不确定性的范围取决于步数 n。

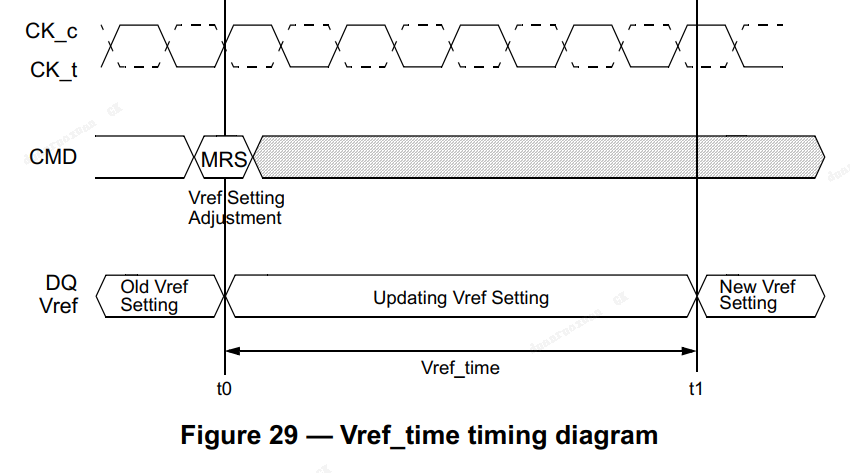

Vref_time 是包括 Vref 电压从 Vrefmin 到 Vrefmax 或从 Vrefmax 到 Vrefmin 变化的时间。

- t0 参考的是 MRS 命令时钟。

- t1 参考的是 Vref_val_tol。

VrefDQ 校准模式通过 MRS 命令进入,方法是将 MR6 A[7] 设置为 1(设置为 0 时禁用 VrefDQ 校准模式),并将 MR6 A[6] 设置为 0 或 1 以选择所需的范围,MR6 A[5:0] 设置为 "无关"(进入训练模式时,MR6 A[7]=1 时的 VrefDQ 训练值 (MR6 A[5:0]) 是否被 DRAM 捕获,取决于供应商,且没有默认初始设置)。随后的 MRS 命令用于在 MR6 A[5:0] 设置所需的 VrefDQ 值。

一旦进入 VrefDQ 校准模式,在满足 tVREFDQE 之后,可以发出合法的 VrefDQ 校准模式命令。合法的 VrefDQ 校准模式命令包括 ACT、WR、WRA、RD、RDA、PRE、DES、MRS 设置 VrefDQ 值以及退出 VrefDQ 校准模式的 MRS 命令。

进入 VrefDQ 校准模式后,在初始化后第一次执行 VrefDQ 校准之前,可以发出“虚拟”写命令。在写命令之间可以有空闲周期,只要满足其他 DRAM 时序要求即可。一个可能的命令序列示例为:WR1, DES, DES, DES, WR2, DES, DES, DES, WR3, DES, DES, DES, WR4, DES, DES……DES, DES, WR50, DES, DES, DES。

设置 VrefDQ 值时,需要将 MR6 [7] 设置为 1,MR6 [6] 保持初始范围选择不变,MR6 A[5:0] 设置为所需的 VrefDQ 值;如果 MR6 [7] 设置为 0,则 MR6 [6:0] 不会被写入。在每个 MR6 命令之后,必须满足 Vref_time,才能使内部 VrefDQ 值有效。

如果在使用 VrefDQ 校准的同时启用了 PDA 模式,那么 PDA 模式的要求仍然有效,即在 PDA 模式启用期间只能使用 MRS 命令。因此,上述合法的 VrefDQ 校准模式命令中,只有 MRS 命令可以使用,即 MRS 用于设置 VrefDQ 值,MRS 用于退出 VrefDQ 校准模式。

在退出 VrefDQ 校准模式之前,最后一次写入 MR6 的 A[6:0] 设置将成为内部 VrefDQ 设置的范围和值。当 DRAM 处于空闲状态时,可以退出 VrefDQ 校准模式。在发出退出 VrefDQ 校准模式的 MRS 命令后,必须发出 DES 命令,直到满足 tVREFDQX,此后可以发出任何合法命令。

4.13.1 VREFDQ 校准模式示例脚本

当 MR6 [7] = 0 时,MR6 [6:0] = XXXXXXX。

进入 VREFDQ 校准模式(范围 1):

- MR6 [7:6] = 10,且 [5:0] = XXXXXX

- 所有后续 VREFDQ 校准 MR 设置命令为 MR6 [7:6] = 10,MR6 [5:0] = VVVVVV

{VVVVVV 为 VrefDQ 的期望设置} - 发出 ACT/WR/RD 命令,检查通过/失败,以确定 Vcent(中点),如有需要

- 在退出 VREFDQ 校准模式之前:

-

- 最后两个 VREFDQ 校准 MR 命令为:

-

-

- MR6 [7:6] = 10,MR6 [5:0] = VVVVVV',其中 VVVVVV' = VREFDQ 的期望值

- MR6 [7] = 0,MR6 [6:0] = XXXXXXX 以退出 VREFDQ 校准模式

-

进入 VREFDQ 校准模式(范围 2):

- MR6 [7:6] = 11,且 [5:0] = XXXXXX

- 所有后续 VREFDQ 校准 MR 设置命令为 MR6 [7:6] = 11,MR6 [5:0] = VVVVVV

{VVVVVV 为 VrefDQ 的期望设置} - 发出 ACT/WR/RD 命令,检查通过/失败,以确定 Vcent(中点),如有需要

- 在退出 VREFDQ 校准模式之前:

-

- 最后两个 VREFDQ 校准 MR 命令为:

-

-

- MR6 [7:6] = 11,MR6 [5:0] = VVVVVV',其中 VVVVVV' = VREFDQ 的期望值

- MR6 [7] = 0,MR6 [6:0] = XXXXXXX 以退出 VREFDQ 校准模式

-

4.14 Per DRAM Addressability(PDA)

DDR4 允许对单个 rank 上的每个设备进行编程。例如,这个功能可以用来在给定 rank 上的 DRAM 设备上编程不同的 ODT 或 Vref 值。

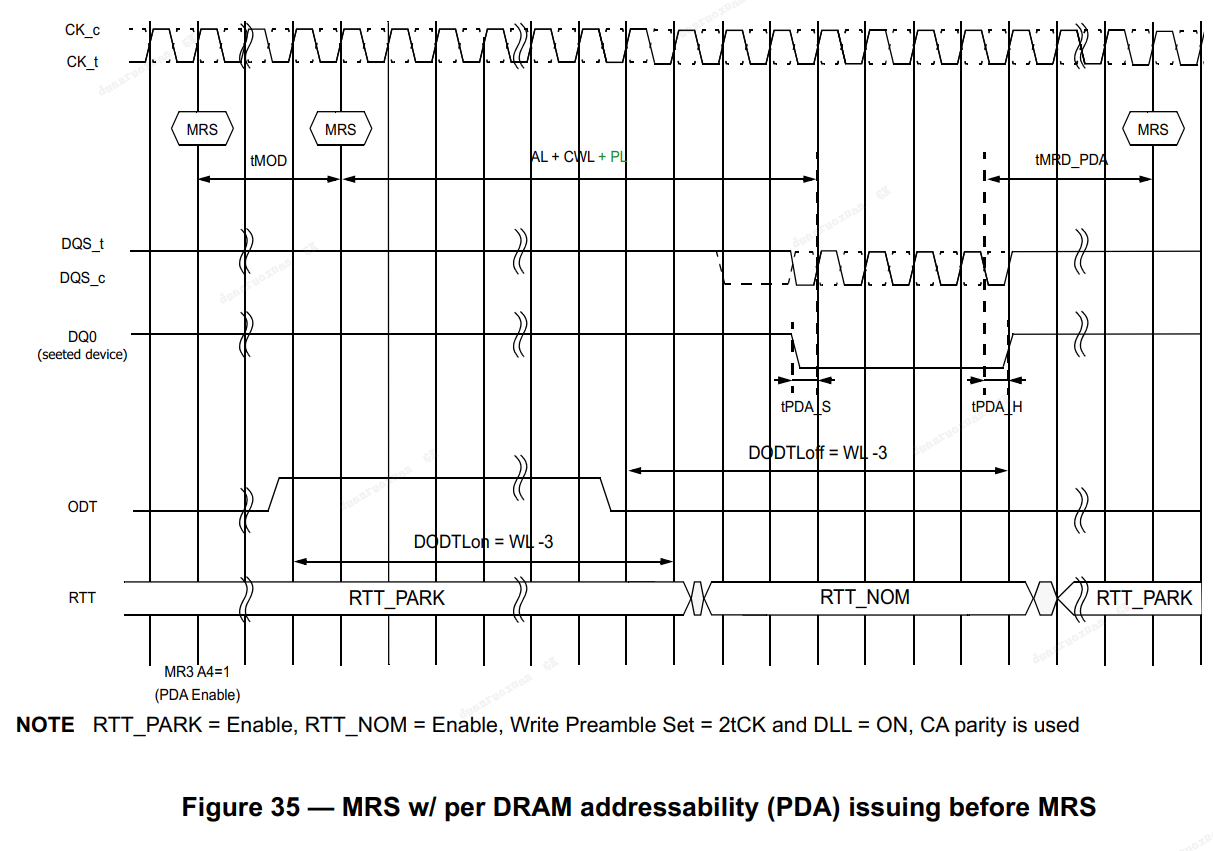

- 在进入“每 DRAM 地址可寻址(PDA)”模式之前,需要进行写入延迟调整。

- 在进入“每 DRAM 地址可寻址(PDA)”模式之前,可以进行以下 Mode Register 设置:

- RTT_PARK MR5 {A8:A6} = Enable

- RTT_NOM MR1 {A10:A9:A8} = Enable

- 使用 MR3 的位 “A4=1” 启用“每 DRAM 地址可寻址(PDA)”模式。

- 在 PDA 模式 下,所有 MRS 命令都以 DQ0 为条件。设备通过 DQS 信号捕获 DQ0 的值。如果 DQ0 的值为 LOW,DRAM 将执行 MRS 命令。如果 DQ0 的值为 HIGH,DRAM 将忽略 MRS 命令。控制器可以选择驱动所有的 DQ 位。 (在PDA模式下利用DQ[0]来选择需要单独编程的DRAM,利用MRS来选择需要编程的内容。(Place DRAM in PDA mode (similar to MRS function in DDR3。这一步利用了16个DRAM的DQ 互相独立的特性。)

- 使用 MRS 命令和 DQ0(对于 x4 和 x8)或 DQL0(对于 x16)编程所需的设备和模式寄存器。

- 在PDA模式下,仅允许执行 MRS 命令。

- 在 PDA 模式下,模式寄存器设置命令周期时间为 AL + CWL + BL/2 - 0.5tCK + tMRD_PDA + (PL),这是完成模式寄存器写操作的最小时间,两个 MRS 命令之间的时间如图 35 所示。

- 通过将 MR3 位 “A4=0” 移除 DRAM 的“每 DRAM 地址可寻址”模式(此命令需要 DQ0=0 对于 x4 和 x8,DQL0 对于 x16,如图 36 所示)。

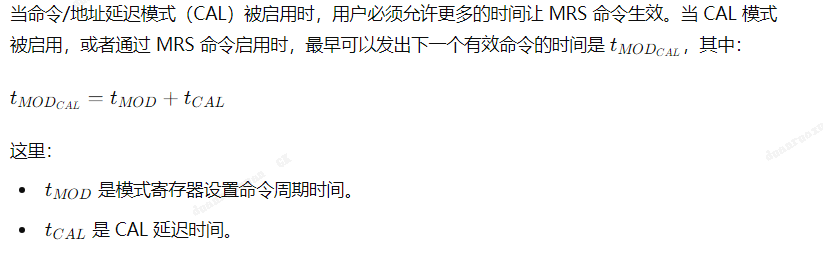

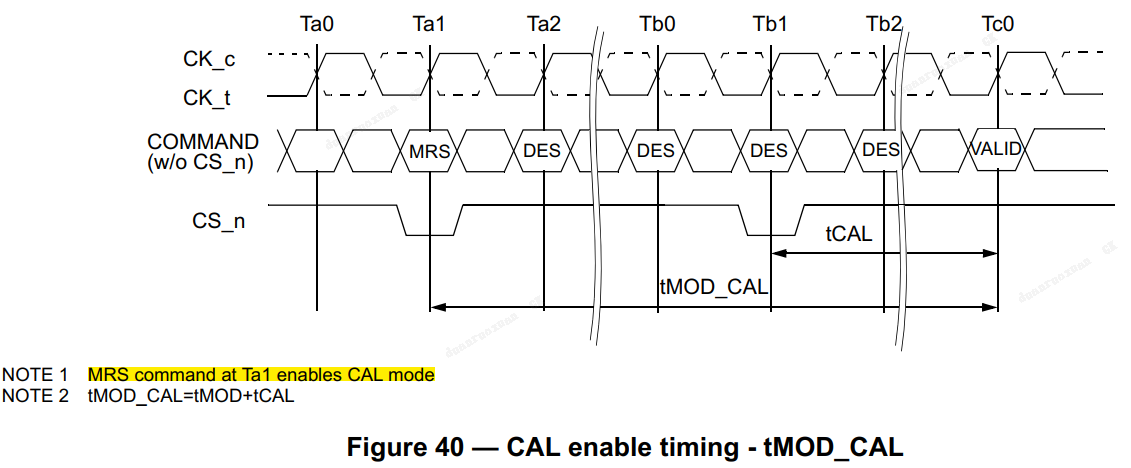

4.15 CAL模式(CS_n到命令地址延迟)

4.15.1 CAL模式说明

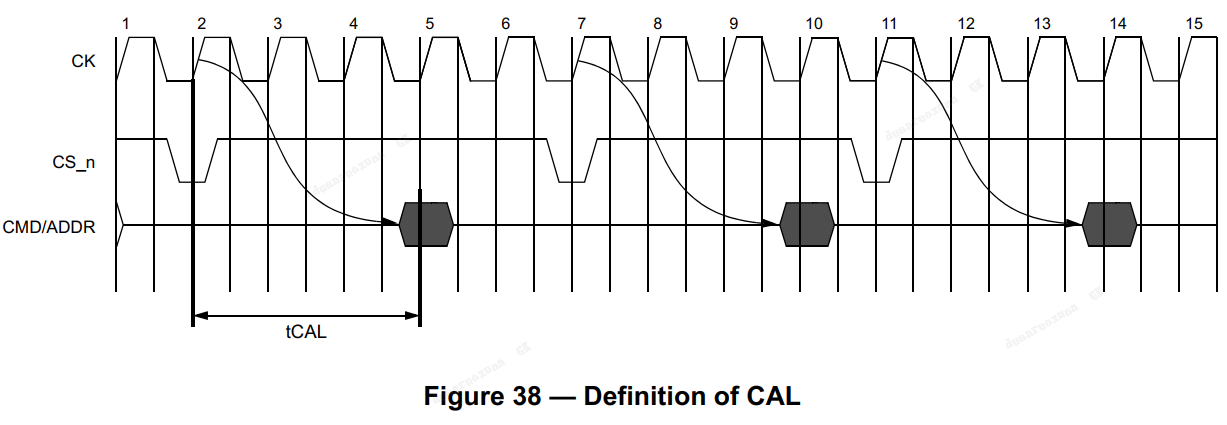

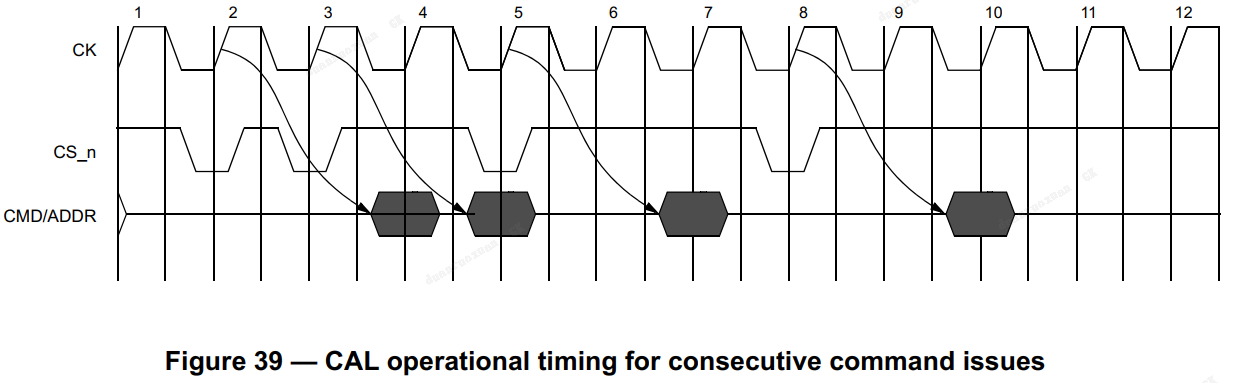

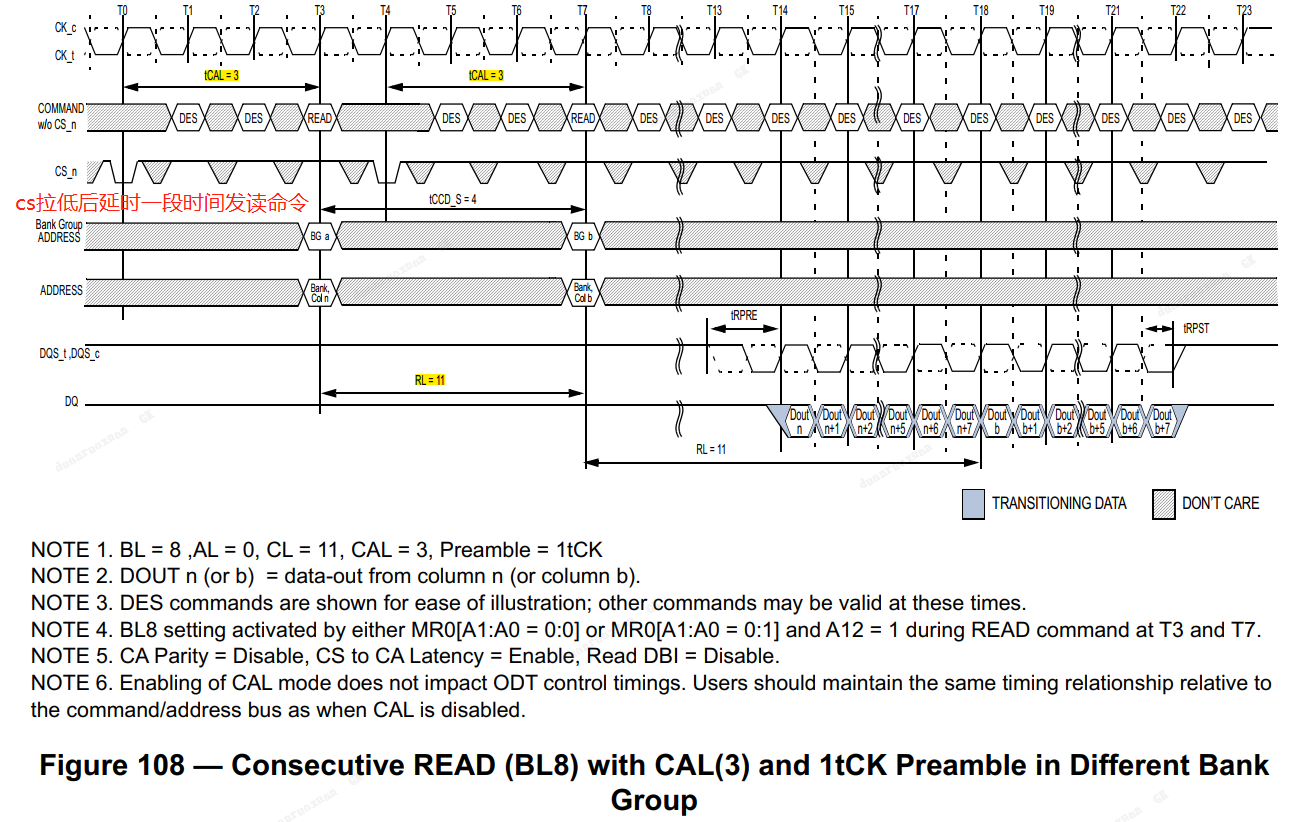

DDR4 支持命令地址延迟(CAL)功能,作为节能特性的一部分。CAL 是指在 CS_n 和 CMD/ADDR 之间的时钟周期延迟,这个延迟由 MR4[A8] 定义(见图 38)。

CAL 的作用是给 DRAM 提供时间来启用 CMD/ADDR 接收器,在发出命令之前。命令和地址一旦被锁存,接收器可以被禁用。对于连续命令,DRAM 将在整个命令序列的持续时间内保持接收器启用状态(见图 39)。

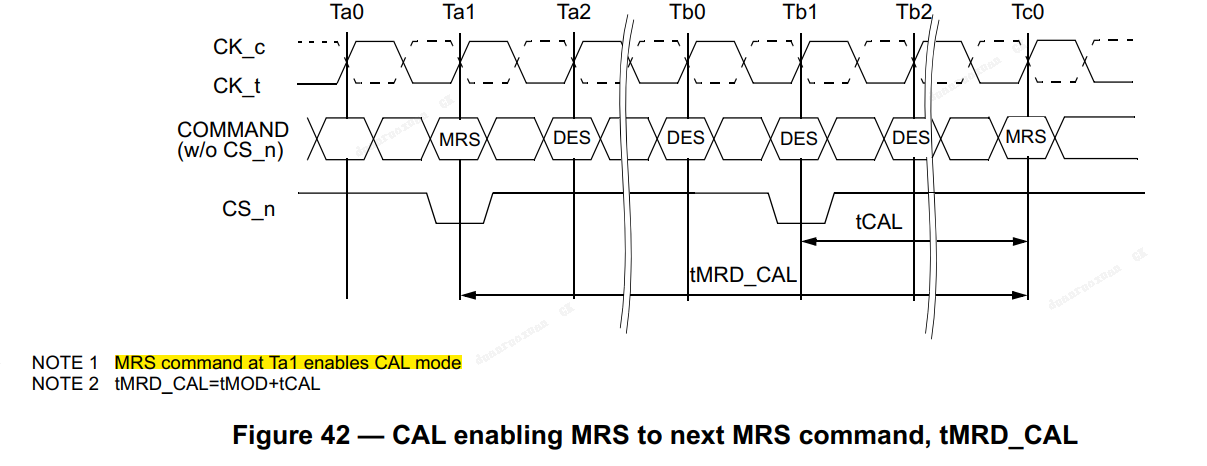

4.15.2 Self Refresh Entry, Exit Timing with CAL

4.16 CRC

4.16.1 CRC多项式和逻辑方程

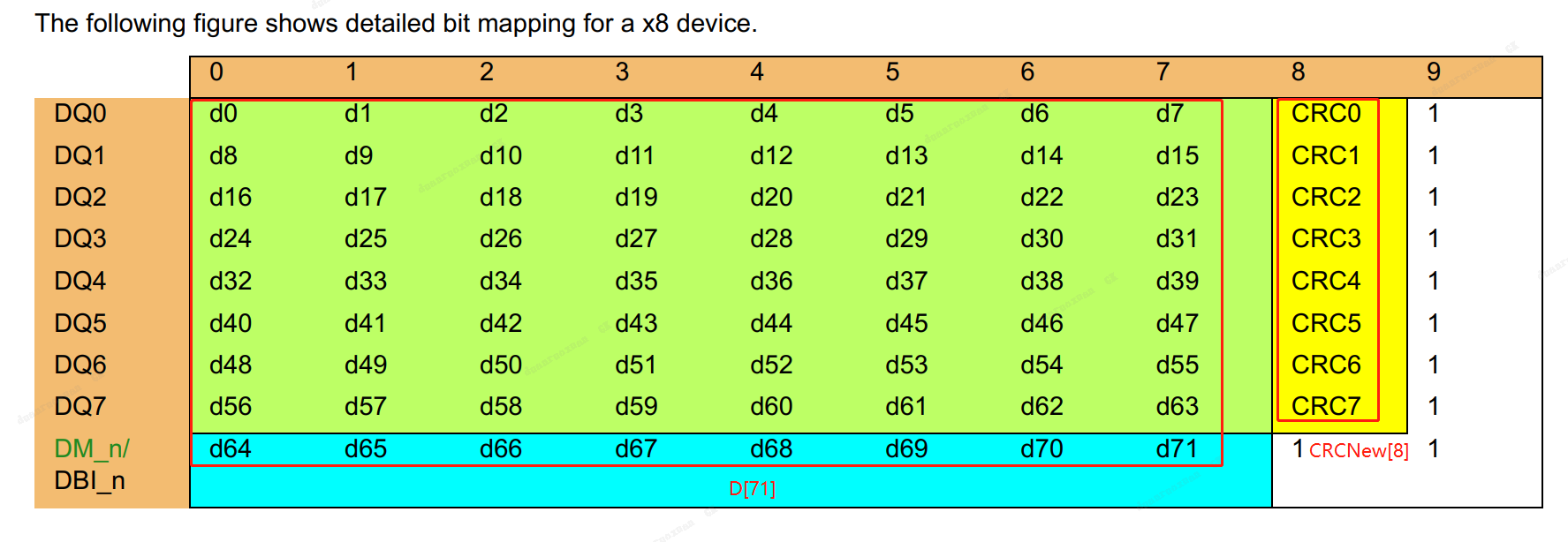

DDR4 支持写操作的 CRC 校验,但不支持读操作的 CRC 校验。DDR4 使用的 CRC 多项式为 ATM-8 HEC,多项式表达式为 ( X^8 + X^2 + X^1 + 1 )。

对于 72 位数据(8n预取+尾部添加的8位CRC校验码)的 8 位 CRC 校验,其组合逻辑实现包含 272 个双输入 XOR 门,分布在 8 个 6 层深的 XOR 树中。

DDR4 使用的 CRC 多项式和组合逻辑与 GDDR5 相同。

在DDR4中,CRC校验啊采用以下电路模二除法进行计算:

CRC COMBINATORIAL LOGIC EQUATIONS

module CRC8_D72;

// polynomial: (0 1 2 8)

// data width: 72

// convention: the first serial data bit is D[71]

// initial condition all 0 implied

function [7:0] nextCRC8_D72;

input [71:0] Data;

reg [71:0] D;

reg [7:0] NewCRC;

begin

D = Data;

NewCRC[0] = D[69] ^ D[68] ^ D[67] ^ D[66] ^ D[64] ^ D[63] ^ D[60] ^

D[56] ^ D[54] ^ D[53] ^ D[52] ^ D[50] ^ D[49] ^ D[48] ^

D[45] ^ D[43] ^ D[40] ^ D[39] ^ D[35] ^ D[34] ^ D[31] ^

D[30] ^ D[28] ^ D[23] ^ D[21] ^ D[19] ^ D[18] ^ D[16] ^

D[14] ^ D[12] ^ D[8] ^ D[7] ^ D[6] ^ D[0] ;

NewCRC[1] = D[70] ^ D[66] ^ D[65] ^ D[63] ^ D[61] ^ D[60] ^ D[57] ^

D[56] ^ D[55] ^ D[52] ^ D[51] ^ D[48] ^ D[46] ^ D[45] ^

D[44] ^ D[43] ^ D[41] ^ D[39] ^ D[36] ^ D[34] ^ D[32] ^

D[30] ^ D[29] ^ D[28] ^ D[24] ^ D[23] ^ D[22] ^ D[21] ^

D[20] ^ D[18] ^ D[17] ^ D[16] ^ D[15] ^ D[14] ^ D[13] ^

D[12] ^ D[9] ^ D[6] ^ D[1] ^ D[0];

NewCRC[2] = D[71] ^ D[69] ^ D[68] ^ D[63] ^ D[62] ^ D[61] ^ D[60] ^

D[58] ^ D[57] ^ D[54] ^ D[50] ^ D[48] ^ D[47] ^ D[46] ^

D[44] ^ D[43] ^ D[42] ^ D[39] ^ D[37] ^ D[34] ^ D[33] ^

D[29] ^ D[28] ^ D[25] ^ D[24] ^ D[22] ^ D[17] ^ D[15] ^

D[13] ^ D[12] ^ D[10] ^ D[8] ^ D[6] ^ D[2] ^ D[1] ^ D[0];

NewCRC[3] = D[70] ^ D[69] ^ D[64] ^ D[63] ^ D[62] ^ D[61] ^ D[59] ^

D[58] ^ D[55] ^ D[51] ^ D[49] ^ D[48] ^ D[47] ^ D[45] ^

D[44] ^ D[43] ^ D[40] ^ D[38] ^ D[35] ^ D[34] ^ D[30] ^

D[29] ^ D[26] ^ D[25] ^ D[23] ^ D[18] ^ D[16] ^ D[14] ^

D[13] ^ D[11] ^ D[9] ^ D[7] ^ D[3] ^ D[2] ^ D[1];

NewCRC[4] = D[71] ^ D[70] ^ D[65] ^ D[64] ^ D[63] ^ D[62] ^ D[60] ^

D[59] ^ D[56] ^ D[52] ^ D[50] ^ D[49] ^ D[48] ^ D[46] ^

D[45] ^ D[44] ^ D[41] ^ D[39] ^ D[36] ^ D[35] ^ D[31] ^

D[30] ^ D[27] ^ D[26] ^ D[24] ^ D[19] ^ D[17] ^ D[15] ^

D[14] ^ D[12] ^ D[10] ^ D[8] ^ D[4] ^ D[3] ^ D[2];

NewCRC[5] = D[71] ^ D[66] ^ D[65] ^ D[64] ^ D[63] ^ D[61] ^ D[60] ^

D[57] ^ D[53] ^ D[51] ^ D[50] ^ D[49] ^ D[47] ^ D[46] ^

D[45] ^ D[42] ^ D[40] ^ D[37] ^ D[36] ^ D[32] ^ D[31] ^

D[28] ^ D[27] ^ D[25] ^ D[20] ^ D[18] ^ D[16] ^ D[15] ^

D[13] ^ D[11] ^ D[9] ^ D[5] ^ D[4] ^ D[3];

NewCRC[6] = D[67] ^ D[66] ^ D[65] ^ D[64] ^ D[62] ^ D[61] ^ D[58] ^

D[54] ^ D[52] ^ D[51] ^ D[50] ^ D[48] ^ D[47] ^ D[46] ^

D[43] ^ D[41] ^ D[38] ^ D[37] ^ D[33] ^ D[32] ^ D[29] ^

D[28] ^ D[26] ^ D[21] ^ D[19] ^ D[17] ^ D[16] ^ D[14] ^

D[12] ^ D[10] ^ D[6] ^ D[5] ^ D[4];

NewCRC[7] = D[68] ^ D[67] ^ D[66] ^ D[65] ^ D[63] ^ D[62] ^ D[59] ^

D[55] ^ D[53] ^ D[52] ^ D[51] ^ D[49] ^ D[48] ^ D[47] ^

D[44] ^ D[42] ^ D[39] ^ D[38] ^ D[34] ^ D[33] ^ D[30] ^

D[29] ^ D[27] ^ D[22] ^ D[20] ^ D[18] ^ D[17] ^ D[15] ^

D[13] ^ D[11] ^ D[7] ^ D[6] ^ D[5];

nextCRC8_D72 = NewCRC;

endmodule4.16.2 x8设备的CRC数据位映射

4.16.5 针对 x4、x8 和 x16 设备的写入 CRC

控制器生成 CRC 校验和,并按照第 4.16.1 节至第 4.16.4 节所示的方式形成写入数据帧。

对于 x8 DRAM,若启用了 CRC,控制器必须在传输 9 中发送 1;若启用了 DBI 功能,则必须在 DBI_n 通道的传输 8 和传输 9 中发送 1。

对于 x16 DRAM,若启用了 CRC,控制器必须在传输 9 中发送 1;若启用了 DBI 功能,则必须在 DBIL_n 和 DBIU_n 通道的传输 8 和传输 9 中发送 1。

DRAM 通过比较接收到的校验和与计算出的校验和来检查收到的代码字 D[71:0] 中是否有错误,若存在不匹配,则通过 ALERT_n 信号报告错误。

x8 设备有一个 72 输入位的 CRC 树。如果启用了写入 DBI 或 DM则占据高8 位。注意,写入 DBI 和 DM 功能不能同时启用。如果两者都禁用,则上高8 位 D[71:64] 的输入为 '1'。

x16 设备有两个相同的 72 输入位 CRC 树。如果启用了写入 DBI 或 DM,则使用高 8 位。注意,写入 DBI 和 DM 功能不能同时启用。如果两者都禁用,则高 8 位 [D(143:136) 和 D(71:64)] 的输入为 '1'。

x4 设备有一个 32 输入位的 CRC 树。上 40 位 D[71:32] 的输入为 '1'。

对于完整写入,DRAM 可以在不等待 CRC 检查的情况下将数据写入 DRAM 核心。如果坏数据被写入 DRAM 核心,控制器将重试该事务并覆盖坏数据。控制器负责数据的一致性。

4.16.6 CRC 错误处理

CRC 错误机制使用相同的 Alert_n 信号来报告对 DRAM 写入时的错误。控制器无法区分 CRC 错误与命令/地址/奇偶校验错误,除非读取 DRAM 的模式寄存器。然而,在多rank配置中,这是一个非常耗时的过程。

为了加快 CRC 错误的恢复,CRC 错误仅作为脉冲反馈。脉冲的最小宽度为六个时钟周期。到达 Alert_n 信号的延迟定义为 tCRC_ALERT,如下图所示。

DRAM 在检测到 CRC 错误时,会将 MR5 的 A3 位的 CRC 错误清除位设为 '1',并将 MPR3 页1 中的 CRC 错误状态位设为 '1'。CRC 错误清除位将保持为 '1',直到主机通过 MRS 命令显式清除它为止。

当控制器检测到脉冲宽度的错误时,会重试写入事务。控制器会了解 Alert_n 的最坏延迟(在初始化期间),并根据情况备份事务,或者控制器可以更加智能,尝试将写入 CRC 错误与特定的秩或事务相关联。控制器还负责打开任何页面,并确保重试写入时以一致的方式进行。

如果出现多个 CRC 错误,由于 Alert_n 是菊花链总线,控制器可能会看到脉冲宽度超过六个时钟周期(?)。

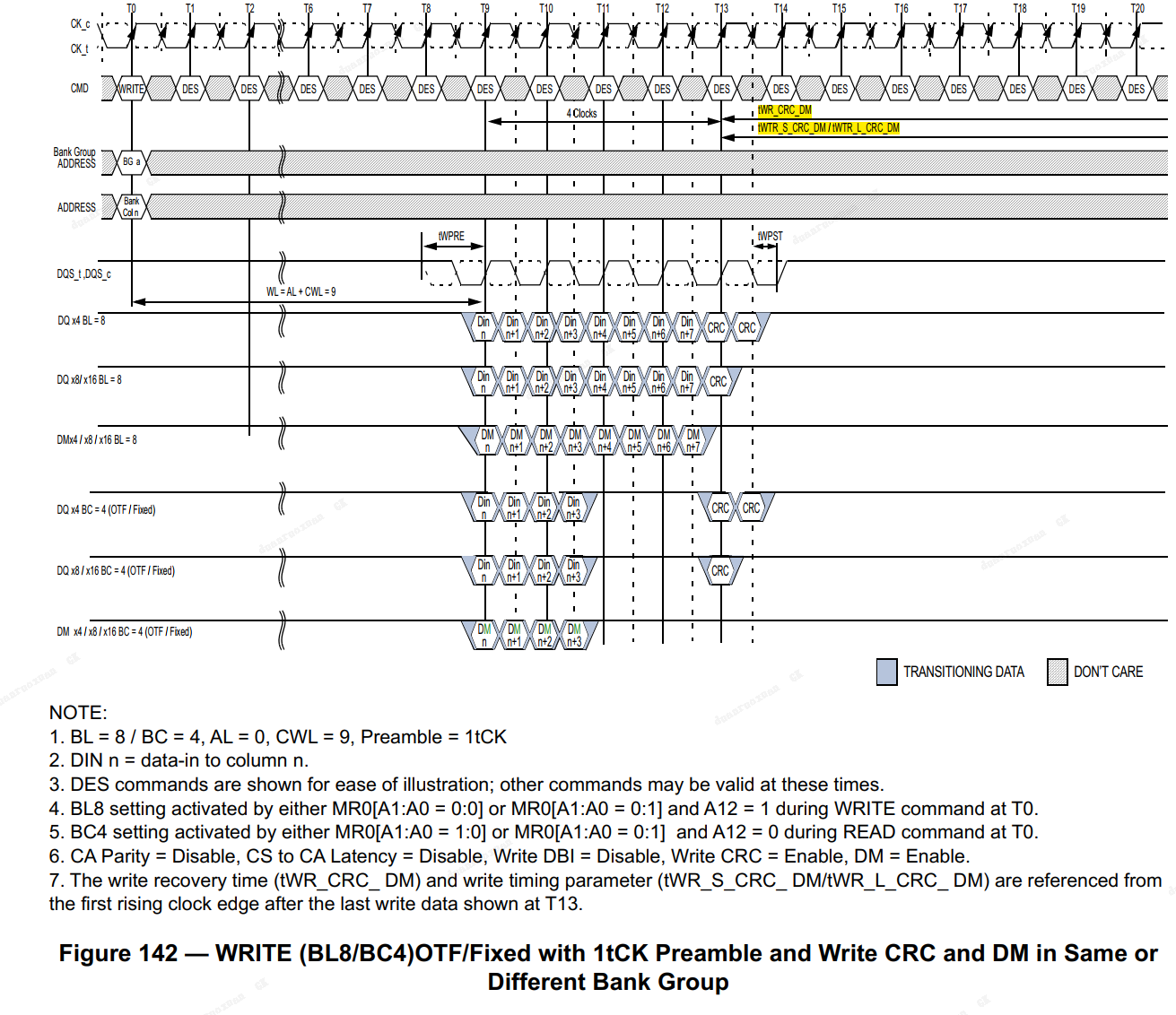

4.16.8 同时启用 DM 和 CRC 功能

当在 DRAM 模式寄存器中同时启用 DM(数据掩码)和写入 CRC 时,DRAM 会在将写入数据送入存储阵列之前计算 CRC。如果出现 CRC 错误,DRAM 将阻止写操作并丢弃数据。对于 x16 DRAM,当 DRAM 在 CRC 检查树中检测到错误时,DDR4 DRAM 可能会根据具体供应商的实现行为屏蔽所有 DQ 或一半的 DQ。两种实现方式都是有效的。对于屏蔽一半 DQ 的 DDR4 DRAM,如果较低字节的 CRC 检查树中有错误,DQ0 到 DQ7 会被屏蔽;如果较高字节的 CRC 检查树中有错误,DQ8 到 DQ15 会被屏蔽。

4.16.9 同时启用 MPR 写入、每 DRAM 可寻址性和 CRC 功能

以下组合的 DDR4 功能禁止同时操作:

- MPR 写入与写入 CRC (注意:MPR 写入通过地址引脚实现)

- 每 DRAM 可寻址性与写入 CRC (注意:在 PDA 模式下只允许 MRS 命令,并且 DQ0 用于 PDA 检测)

4.17 命令地址奇偶校验(CA 奇偶校验)

MR5 的 [A2] 位用于启用或禁用 C/A 奇偶校验。C/A 奇偶校验的默认状态是禁用。如果通过在模式寄存器中编程非零值启用 C/A 奇偶校验(启用 C/A 奇偶校验模式时,奇偶校验错误位必须设置为零),那么 DRAM 必须确保在执行命令之前没有奇偶校验错误。当启用 C/A 奇偶校验时,执行命令所需的额外延迟是通过模式寄存器 (MR5, A2) 中的 C/A 奇偶校验延迟(PL:奇偶校验延迟)进行编程的,并且应用于在 CS_n 为低时,通过 CK_t 上升沿锁存的命令。该命令在设备内部执行之前会被保持奇偶校验延迟的时间。这意味着内部命令的发出时序由 PL 决定。当启用 C/A 奇偶校验时,只有 DES 在有效命令之间被允许,以防止 DRAM 发生任何故障。C/A 奇偶校验模式支持在 DLL 开启模式下使用,不允许在 DLL 关闭模式下使用。

在DRAM管脚上有一个单独的CA校验输入信号,符号为PAR,当在MR5中开启CA校验功能,则CA校验通过ACT_n, RAS_n/A16, CAS_n/A15, WE_n/A14以及其他的地址信号(包括BG0-1, BA0-1, C0-C2)来计算校验值,CKE,ODT和CS_n信号不参与计算。在2.7章节的Pinout Desciption中也有说明,如下图所示。

手册中对CA校验的计算有一个举例,例如在4Gbit的x4单片器件中,CA校验由BG0, BG1, BA1, BA0, A16/ RAS_n, A15/CAS_n, A14/WE_n, A13-A0 and ACT_n信号计算得出,当然,DRAM内部应该将未用到的地址pin视为0。

一般来说,parity一般为偶校验,也就是说,所有用来进行Parity计算的输入,包括Parity信号,应该保持为偶数个1。可以通过改变Parity信号的输入值,来确保所有参与计算的信号其为1的个数为偶数个。

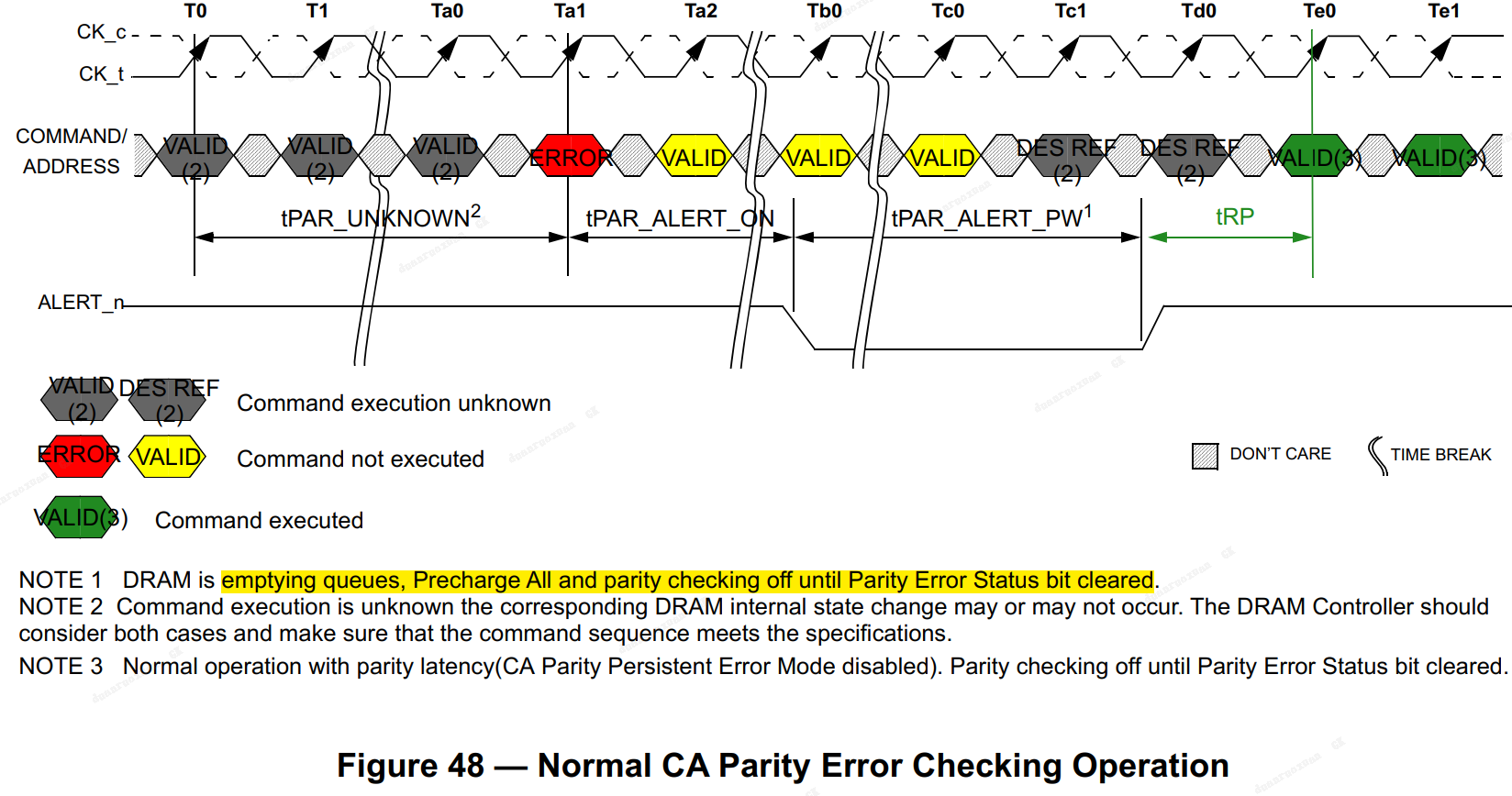

在CS_n拉低时,当DRAM在任何命令中检测到CA校验错误,则会执行以下步骤:

- 忽略出错的命令。在出错的命令之前的命令,也就是位于tPAR_UNKNOWN时间窗口期的命令是否能够被DRAM执行未可知,可能被执行了,也可能没有被执行。当窗口期中的READ命令未被执行,那么DRAM将不会使能DQS的输出。

- DRAM自己会将错误信息写入MPR Page1(?)中。

- 设置MR5中的Parity Error Status位(DRAM自己写1),这个设置必须在ALERT_n信号被DRAM释放之前进行设置也就是需要在tPAR_ALERT_ON + tPAR_ALERT_PW(min)的时间窗口期内进行设置。

- 在tPAR_ALERT_ON时间后置位ALERT_n信号。

- 等待所有正在进行中的命令完成。这些命令是在tPAR_UNKNOWN窗口期接收的。如果在自刷新退出后,parity error出现在tXS_FAST和tXS之间的窗口期中,DRAM将延迟ALERT_n信号的释放。详见图52。

- 在关闭所有打开的page之前等待tRAS_min(ACT到PRE命令的周期)。DRAM在tPAR_ALERT_ON + tPAR_ALERT_PW的时间窗口期不会执行任何命令。这句话是否和前面的发送MRS命令冲突? 其实不冲突,前者是出错后,DRAM自己自动地将MR5中的Parity Error Status置1,而非内存控制器去发送MRS命令。后面也会介绍到外部设置MR5中的Parity Error Status位时,只能写0,不能写1。

- 满足tPAR_ALERT_PW_min时序后,释放ALERT_n。

- ALERT_n信号释放后在DRAM跳到Pre-charge状态。

- 在(tPAR_ALERT_ON + tPAR_ALERT_PW)之后,DRAM可以接收其它命令,并进行正常操作。Parity的Latency会影响命令的时序,但如果不对MR5的Parity Error Status清零的话,parity校验将不会继续进行。

- 在(tPAR_ALERT_ON + tPAR_ALERT_PW)窗口期间,DRAM可能会忽略刷新命令,或者说刷新命令是第一个出错命令,所以推荐的做法是内存控制器多发一个额外的刷新命令。

- Parity Error Status位可以在(tPAR_ALERT_ON + tPAR_ALERT_PW)之后的任何时候去读取。

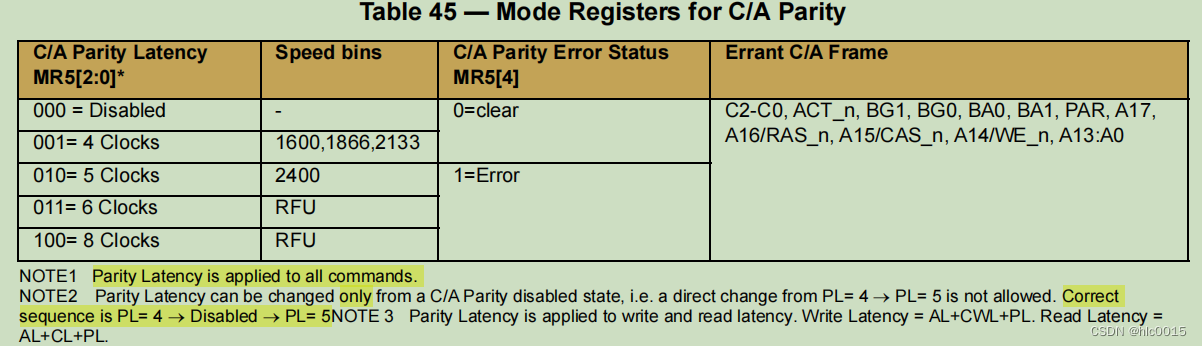

MR5中,CA Parity Latency是write only,Parity Error Status也是write only,且只能写0,不能写1。下表展示了MR5的CA parity相关的bit位。

其中,上表的脚注2对Parity Latency(PL)的切换有详细说明:不能直接从PL=4切换到PL=5,需要在切换间插入一个disable CA parity的设置。PL用于write latency和read latency中。

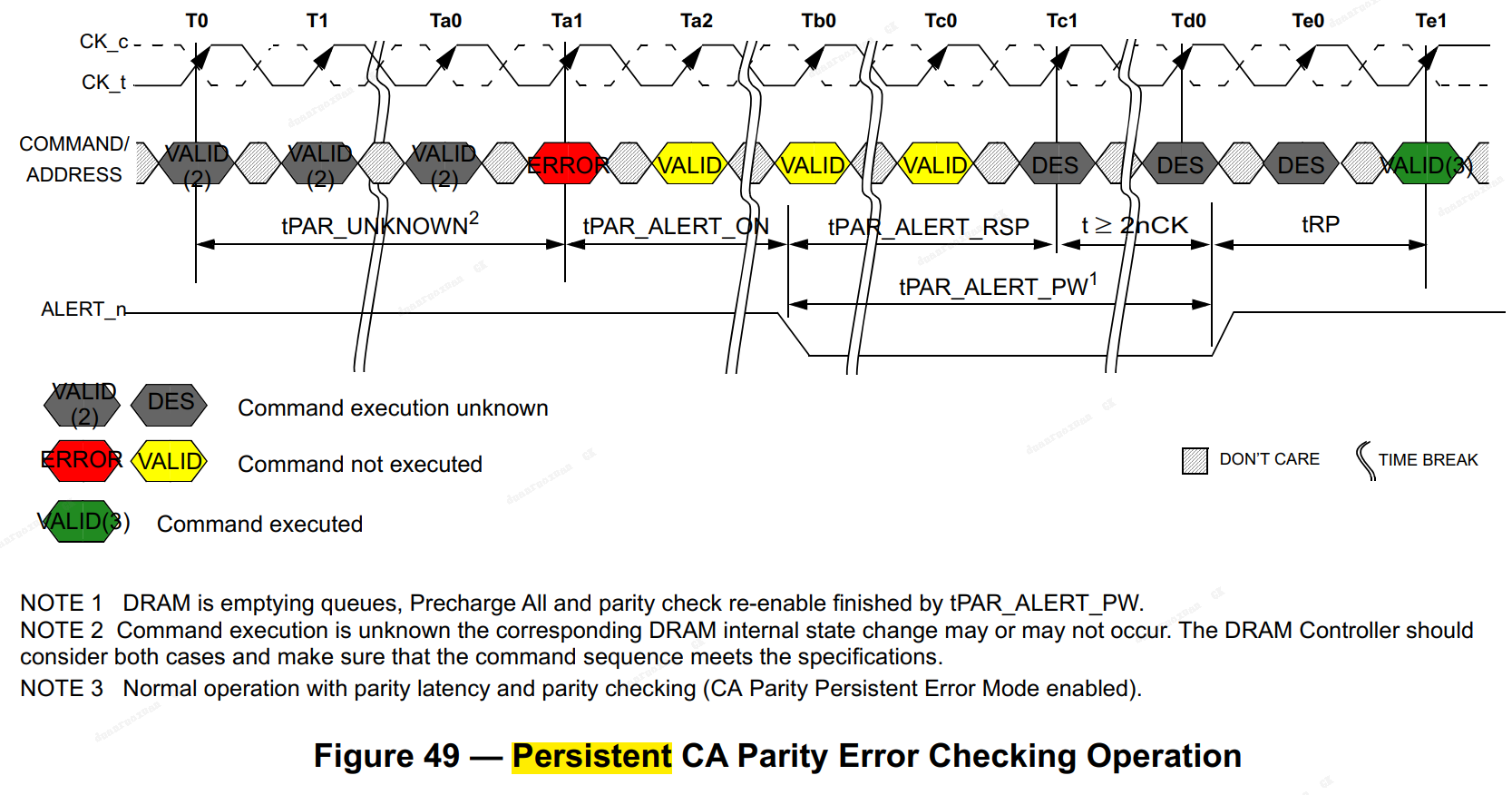

之前提到如果不对Parity Error Status进行清零的话,CA parity校验是不能继续进行的,不过有一种情况除外:当MR5的A9=1(持久性奇偶校验错误模式),则在ALERT_n释放后,即使Parity Error Status未清零,也会进行CA校验。但是,这样做有个坏处,即如果之前有误,MPR Page1中肯定会记录Error log,但是下一次再出现错误,MPR Page1中的对应位将视为"Don’t Care"。当当MR5的A9=1时,ALERT_n脉冲的持续时间依旧遵循tPAR_ALERT_PW的最大/最小值。内存控制器一旦监测到ALERT_n信号拉低了,必须立马发送DES命令,其对应的时间参数为tPAR_ALERT_RSP。

在“持久性奇偶校验错误模式”下,ALERT_n 脉冲将由 DRAM 按照 tPAR_ALERT_PW 的最小值和最大值定义进行断言和取消断言。控制器在检测到 ALERT_n 信号后必须发出取消选择(DESELECT)命令,这个响应时间定义为 tPAR_ALERT_RSP。

下图是开启了Persistenct CA Parity的Error check操作时序图,NOTE3中表示,Te1处的有效命令可以进行Parity校验。

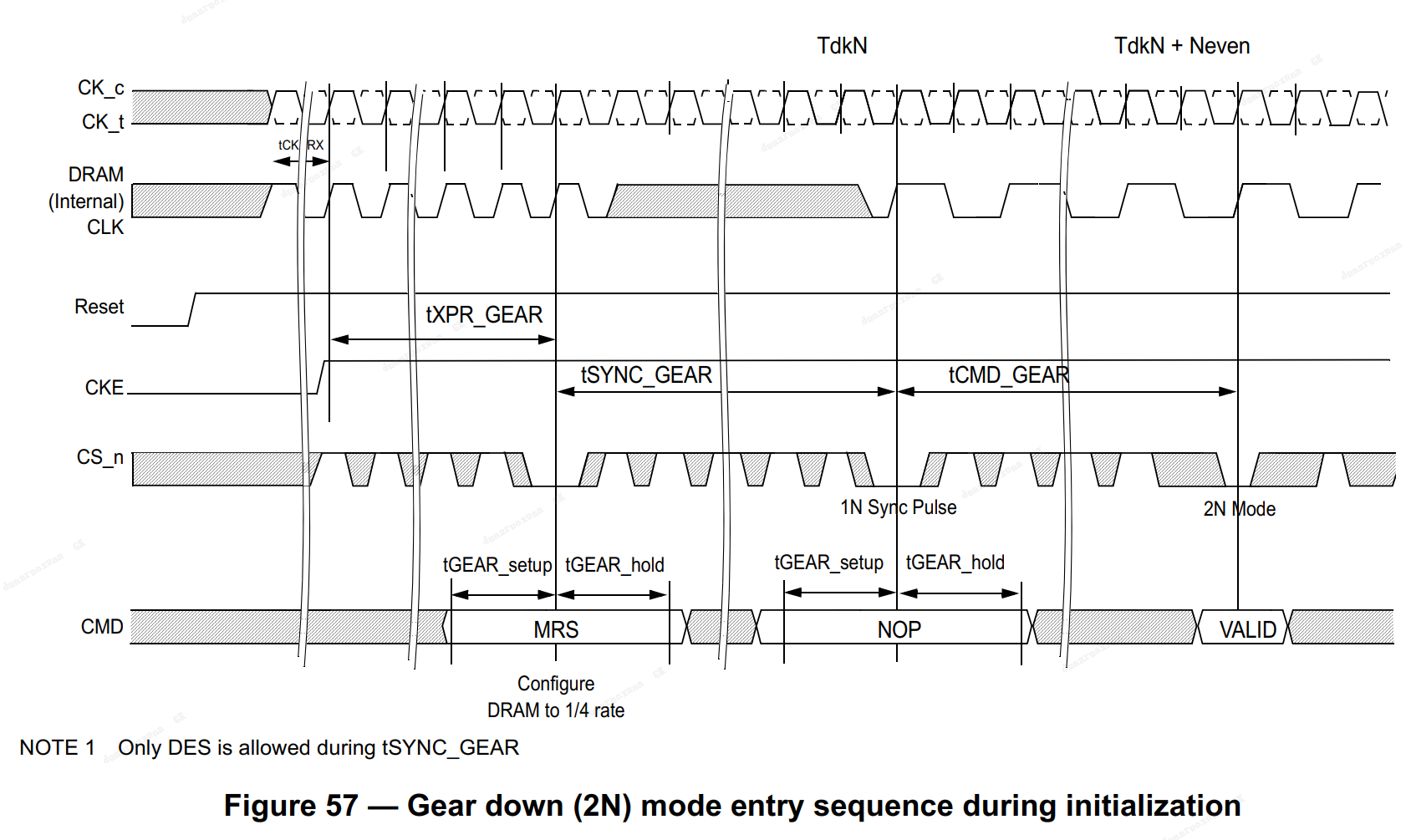

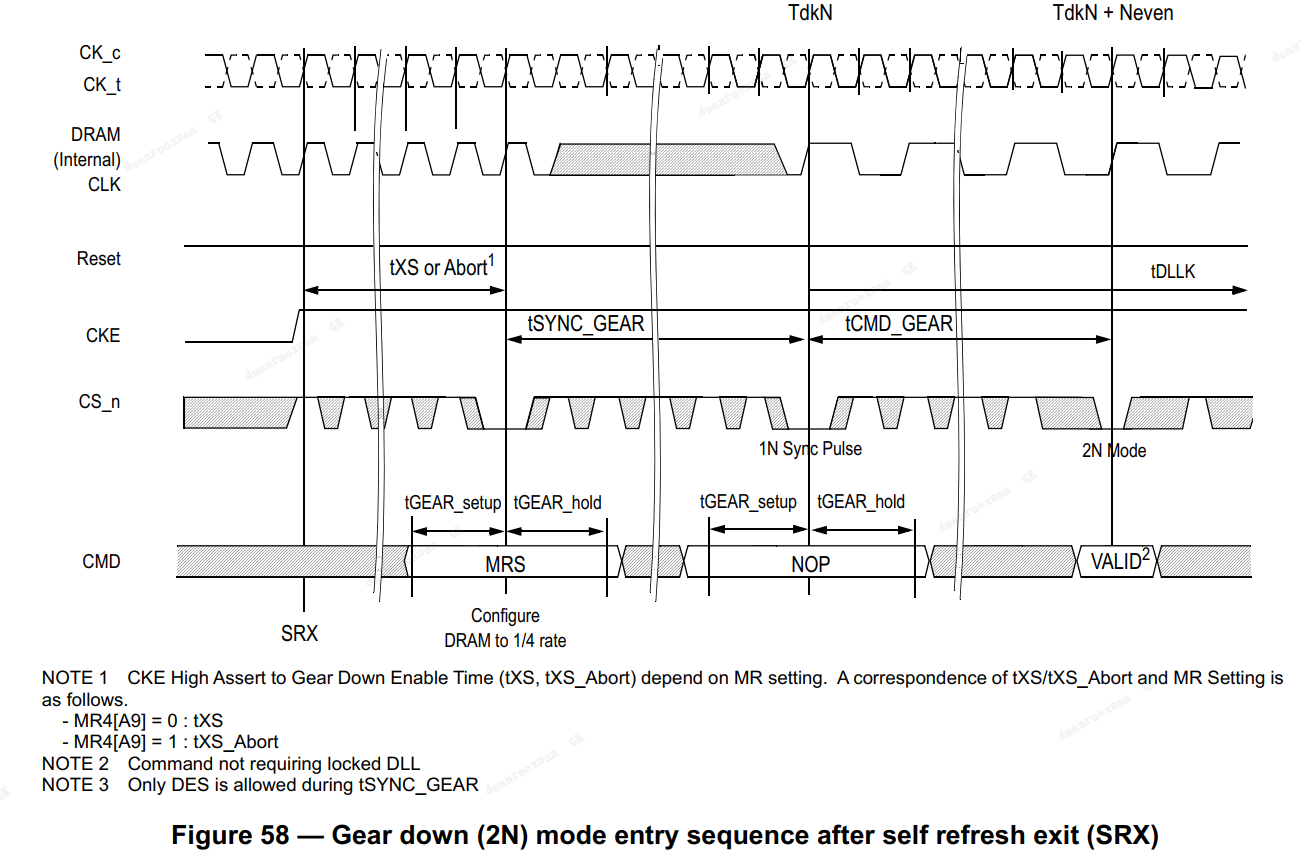

4.18 Gear down模式(??)

通过MR3 A3 bit来控制SDRAM是否进入gear down模式。gear down模式只能在初始化和SRE(退出自刷新)时使用。SDRAM模式位于1/2的rate(1N,即时钟周期为1N)模式,处于此速率模式下的DRAM利用低频率的MRS命令,后续跟随一个同步脉冲来将1/4(2N,即时钟周期为2N,周期长了一倍)rate速率下的CS_n,CKE和ODT信号对齐到合适的时钟边沿。对于1/2 rate模式下,不需要额外的MRS命令与同步脉冲来进入geardown模式。

降频模式初始化操作的一般序列

- 在上电和复位的情况下,DRAM默认处于1/2速率模式。

- 将Reset拉高。CKE置位有效来使能DRAM。

- 发送低频率的MRS命令,该MRS命令设置MR3的A3=1,持续周期为N*tCK时长,但CS_n只有1N周期时长。

- 内存控制器发送1N周期的同步脉冲信号,与此对应的为N*tCK个NOP命令。tSYNC_GEAR时长是偶数个时钟周期,即同步脉冲距离MRS命令有偶数个时钟周期。

- 采样到上一步的1N周期的同步脉冲后的tCMD_GEAR时长后,此后的初始化序列,包括tDLLK和tZQinit,便从2N模式开始(即1/4rate模式)。

自刷新退出后降频模式的操作序列

- DRAM 在自刷新过程中复位到 1N 模式。

- 通过低频 N*tCK MRS 降频命令访问 MRS(设置 MR3为 1),Ntck 静态 MRS 命令由符合 tXS 或 tXS_Abort 的 1N CS_n 限定。在 Ntck 静态 MRS 命令之前,只允许发出刷新命令。

- DRAM 控制器发送 1N 同步脉冲,使用低频 N*tCK NOP 命令。tSYNC_GEAR 是一个偶数时钟周期,同步脉冲在 MRS 命令的偶数时钟边界上触发。

- 不需要锁定 DLL 的有效命令在 1N 同步脉冲(??)后的 tCMD_GEAR 时间内可以在 2N 模式下执行。

- 需要锁定 DLL 的有效命令在 1N 同步脉冲后的 tDLLK 时间内可以在 2N 模式下执行。

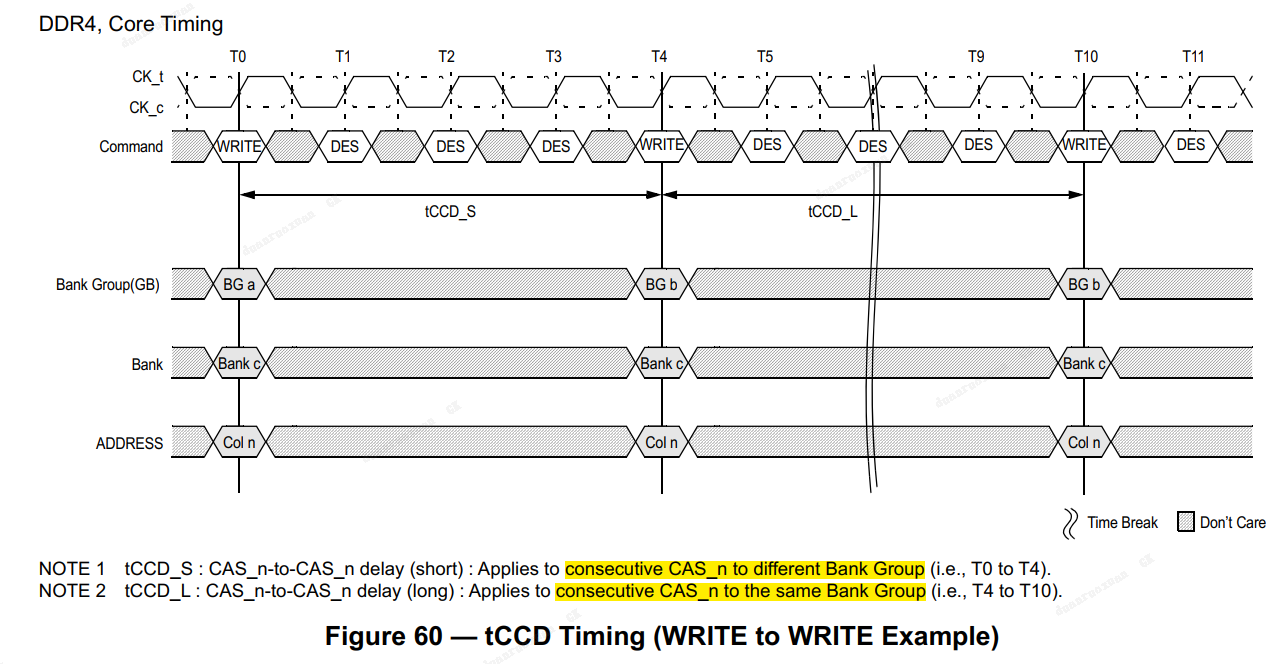

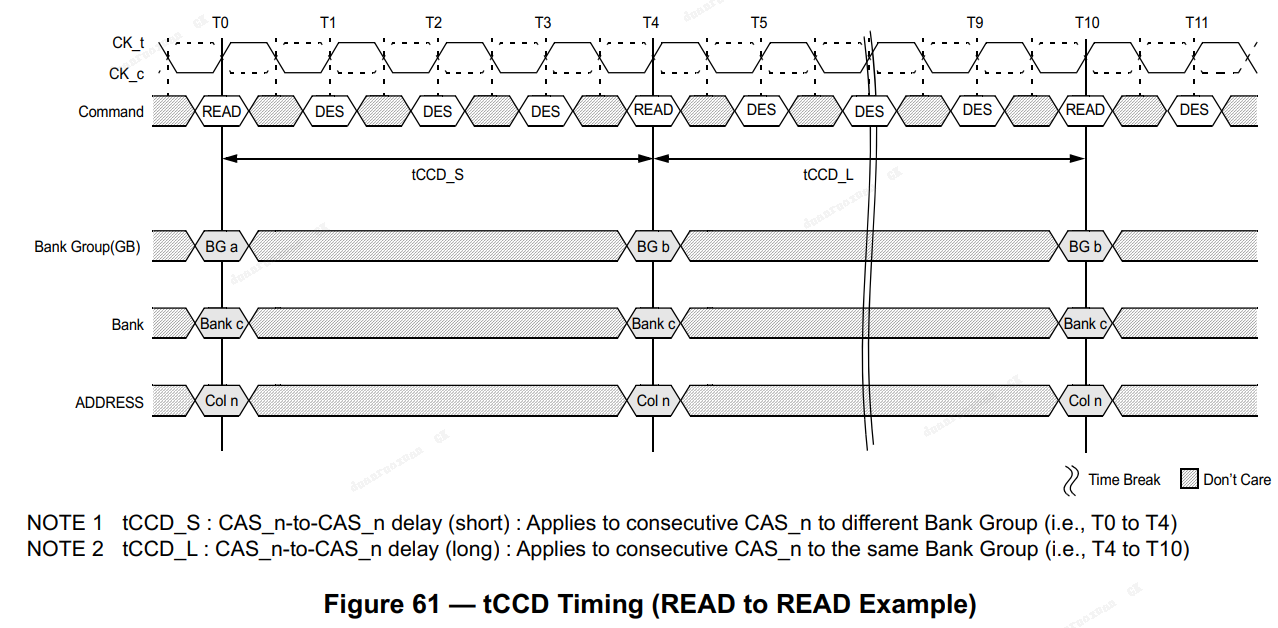

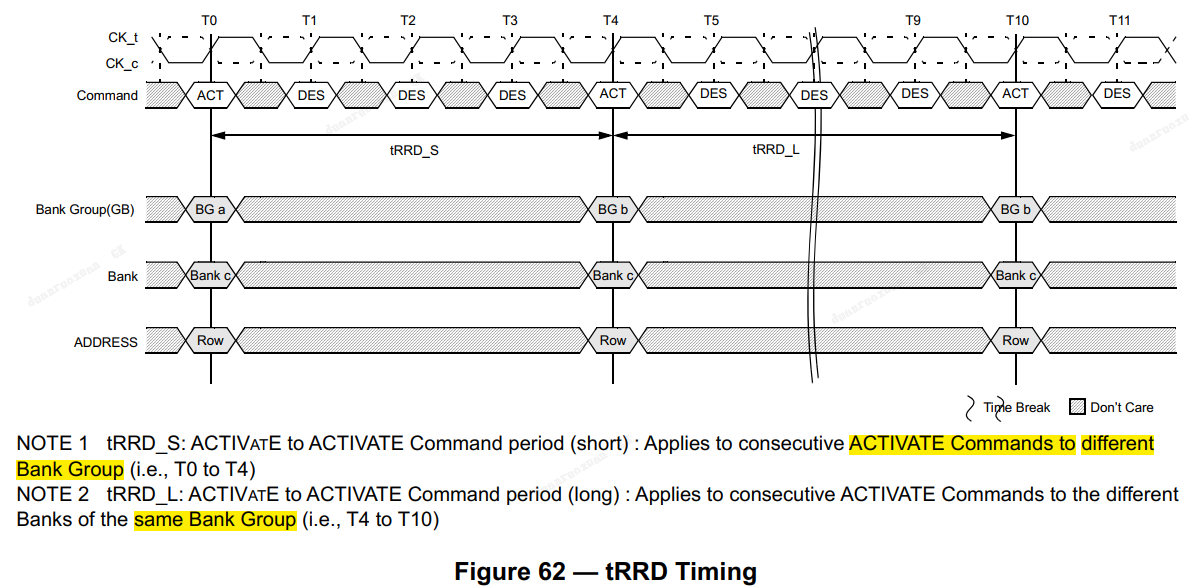

4.19 DDR4 关键核心时序

4.20 Programmable Preamble

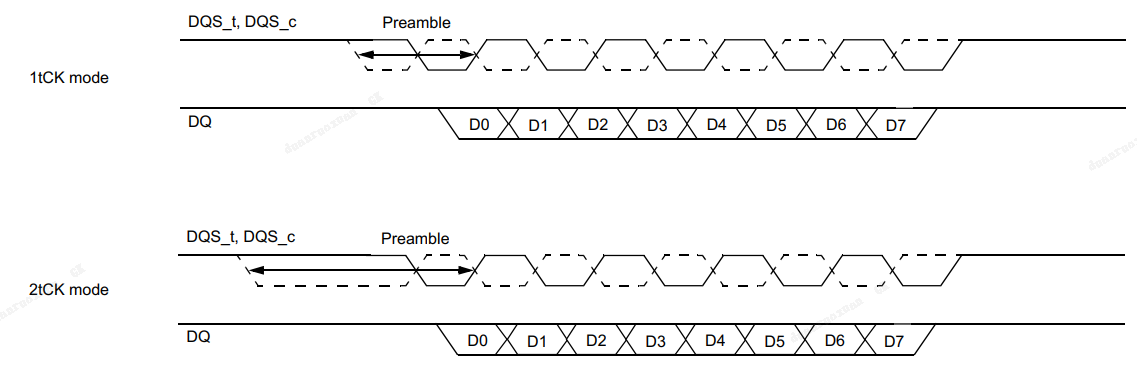

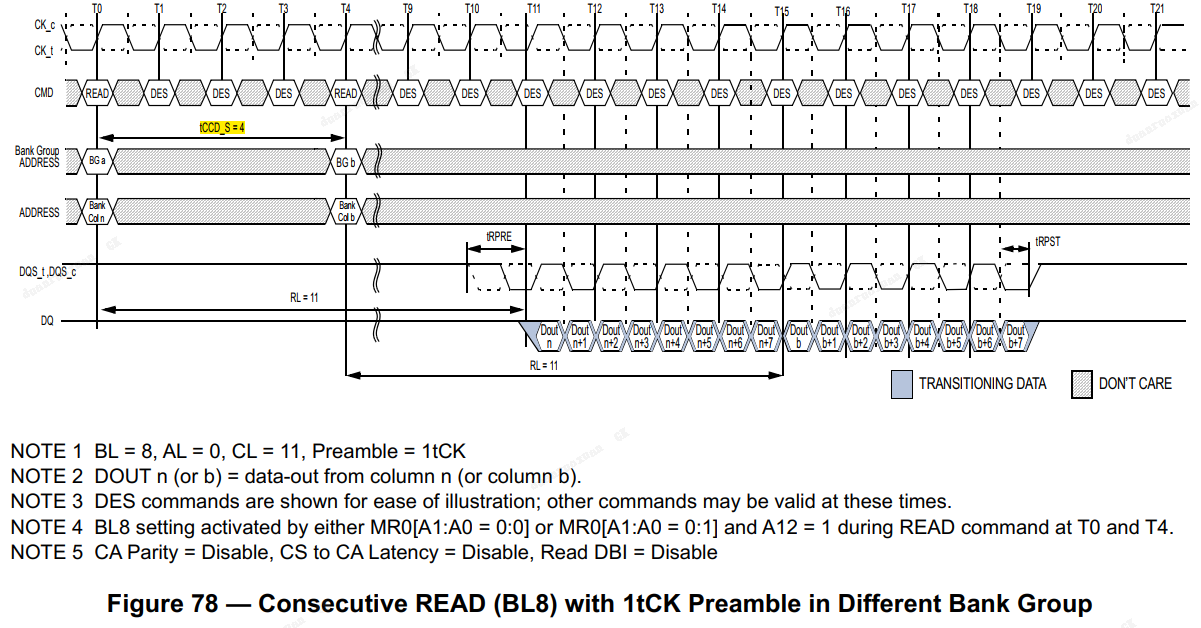

DQS preamble 时间可以通过模式寄存器设置(MRS,MR4 [A12, A11])编程为 1 tCK 或 2 tCK 的 preamble 。1 tCK preamble 适用于所有速度等级,而 2 tCK preamble 则适用于 DDR4-2400、2666 和 3200 的速度等级表。

4.20.1 Write Preamble

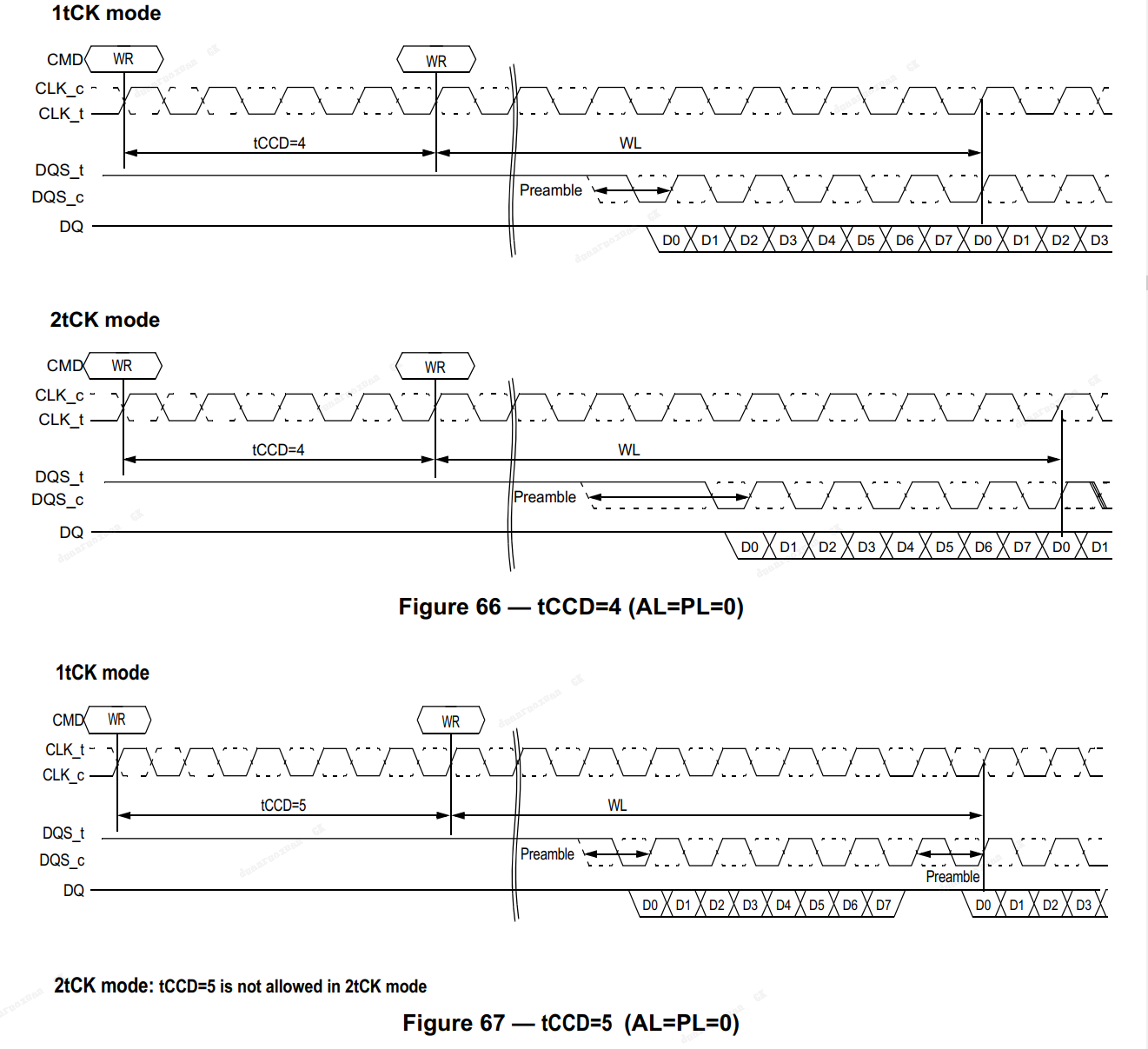

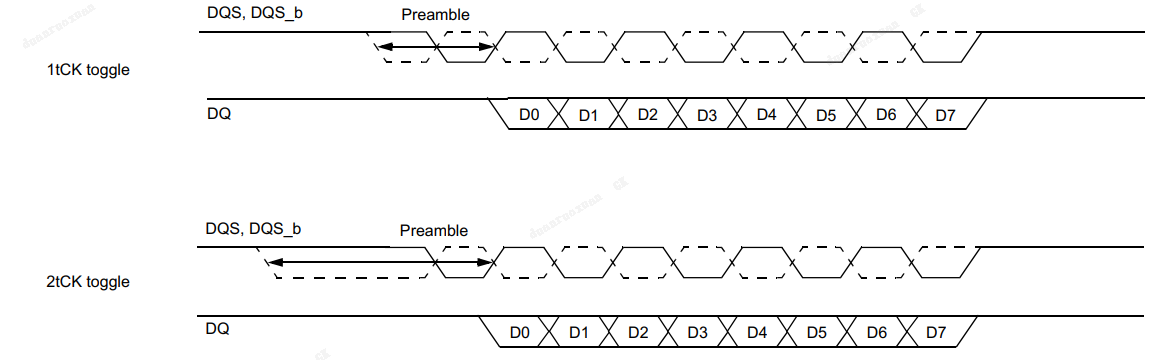

DDR4 支持可编程的write preamble 。可以通过 MR4 [A12] 选择 1 tCK 或 2 tCK 的write preamble。以下显示了 1 tCK 和 2 tCK 的write preamble模式。

当工作在 2 tCK write preamble模式时,在 MR2 表 7 中,第一组的 CWL 需要增加 2 个 nCK(n是多少?),而第二组的 CWL 无需增加。tWTR 必须比适用的速度分类表中所要求的 tWTR 增加一个时钟周期。WR 必须根据可用设置,编程为比适用速度分类表中要求的 WR 设置多一个或两个时钟周期的值。

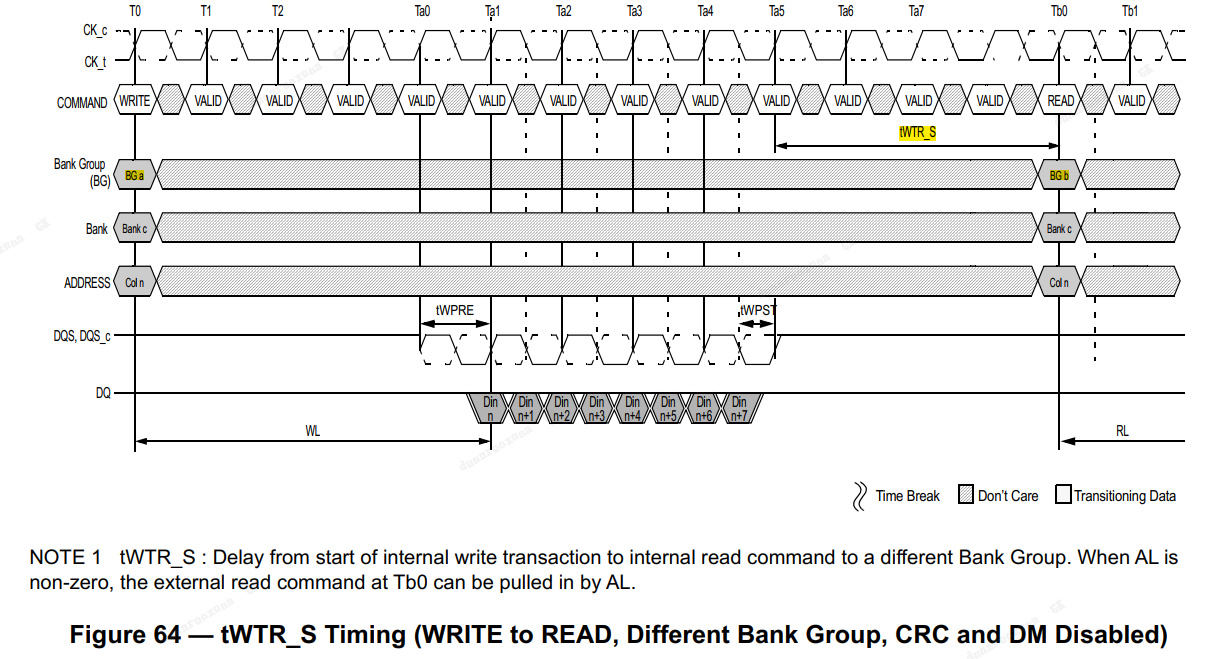

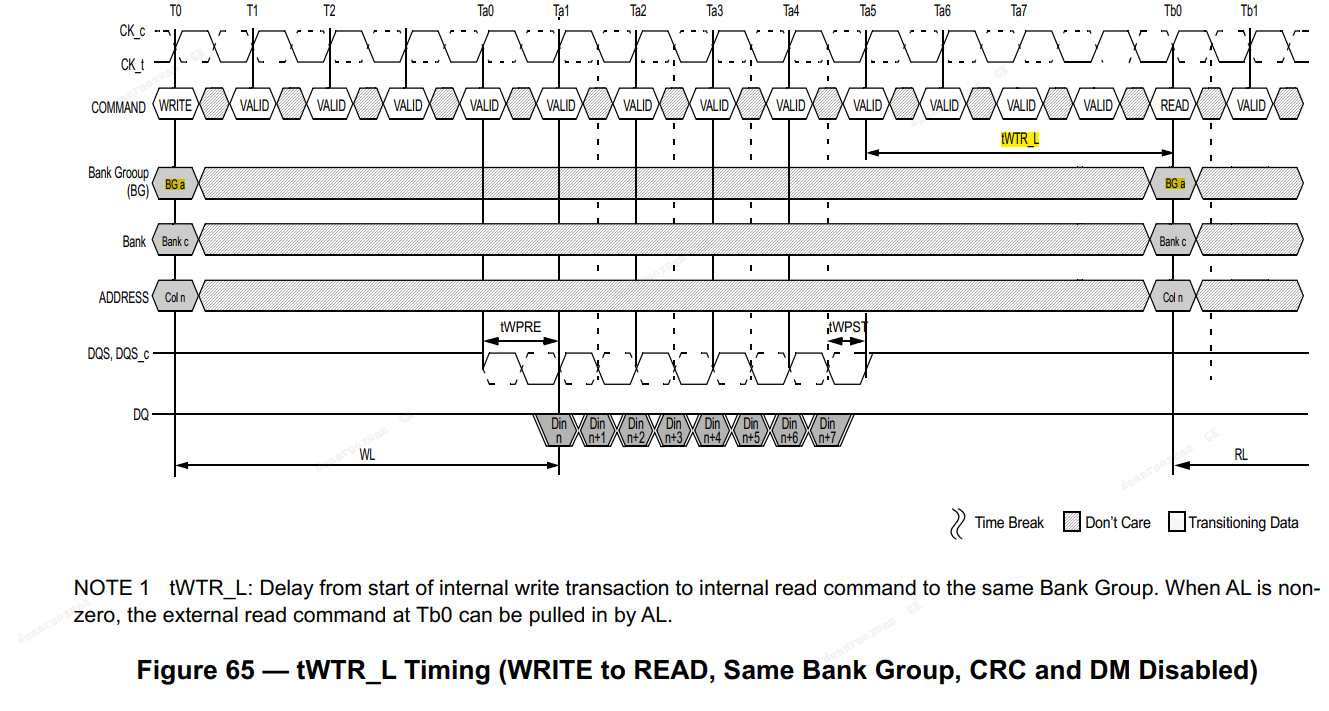

图 66、图 67 和图 68 中的时序图说明了在连续写入命令的情况下,1 tCK 和 2 tCK write preamble场景,分别对应 tCCD 时序为 4、5 和 6 个 nCK。当设置 tCCD 为 5 nCK 时,2 tCK write preamble模式是不允许的。

4.20.2 Read Preamble

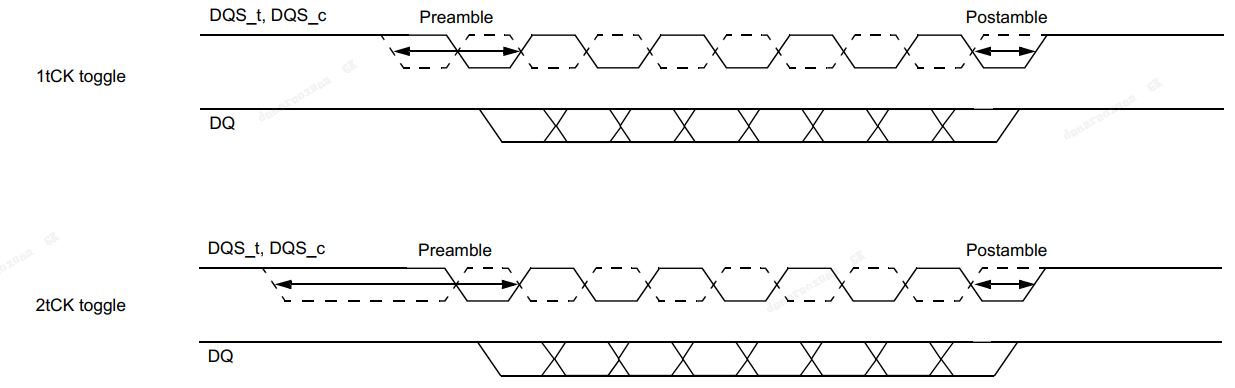

DDR4 支持可编程的read preamble 。可以通过 MR4 [A11] 选择 1 tCK 或 2 tCK 的read preamble。以下显示了 1 tCK 和 2 tCK 的read preamble模式:

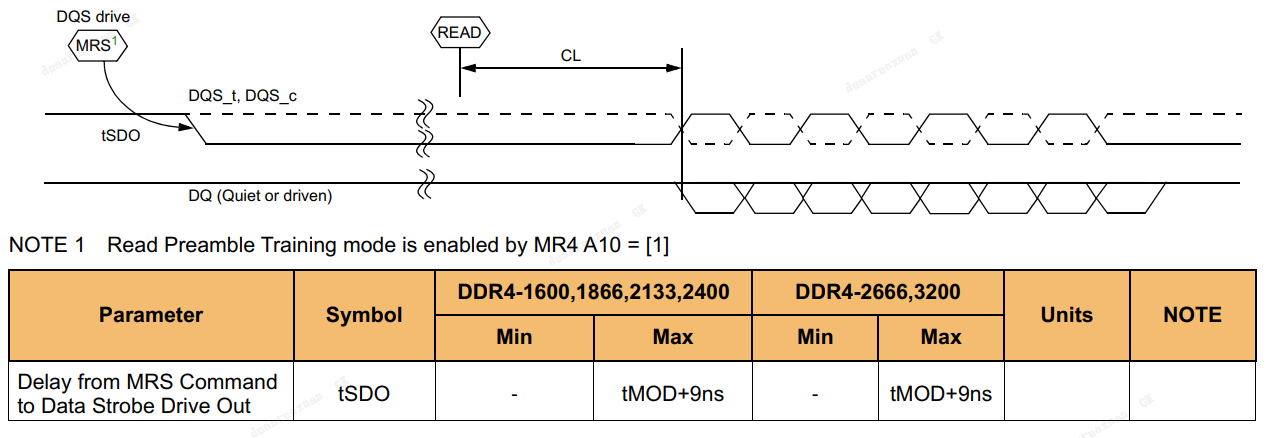

4.20.3 Read Preamble Training

如下面所示,read preamble训练可以在 DRAM 处于 MPR 模式时通过 MR4 [A10] 启用。如果 DRAM 不处于 MPR 模式,则read preamble训练是非法的。read preamble训练可用于读均衡(??)(read leveling)。

在read preamble训练期间,非法的 READ 命令、任何在 READ 过程中的命令或启动 READ 过程的命令,都是不允许的。

4.21 Postamble

4.21.1 Read Postamble

DDR4 将支持固定的read postamble 。对于 1 tCK 和 2 tCK read postamble模式,read postamble的标准值为 0.5 tCK,具体如下所示:

4.21.2 Write Postamble

DDR4 将支持固定的 Write postamble。对于 1 tCK 和 2 tCK 预序模式,Write postamble 的标准值为 0.5 tCK,具体如下所示:

4.22 激活命令

ACTIVATE 命令用于打开(或激活)特定 bank 中的一行,以便后续访问。在 X4/8 配置中,BG0-BG1 的值以及在 X16 配置中,BG0 的值选择 bank 组;BA0-BA1 输入选择 bank 组内的 bank,A0-A17 输入的地址选择行。该行在访问过程中保持激活(或打开)状态,直到对该 bank 发出预充电命令或发出全体预充电命令。在打开同一 bank 中的不同行之前,必须先对该 bank 进行预充电。

4.23 充电命令

PRECHARGE 命令用于关闭特定 bank 中的打开行或所有 bank 中的打开行。在 PRECHARGE 命令发出后,指定时间 (tRP) 之后,该 bank 将可用于后续行激活操作。例外情况是并发自动预充电(??),在这种情况下,只要不打断当前 bank 的数据传输,并且不违反任何其他时序参数,可以对不同的 bank 发出 READ 或 WRITE 命令。一旦某个 bank 完成预充电,它将进入空闲状态,并且在对该 bank 发出任何 READ 或 WRITE 命令之前,必须先进行激活。

如果该 bank 处于空闲状态(无打开行)或之前打开的行已经在预充电过程中,则允许发出 PRECHARGE 命令。不过,预充电时间将由最后一个对该 bank 发出的 PRECHARGE 命令决定。

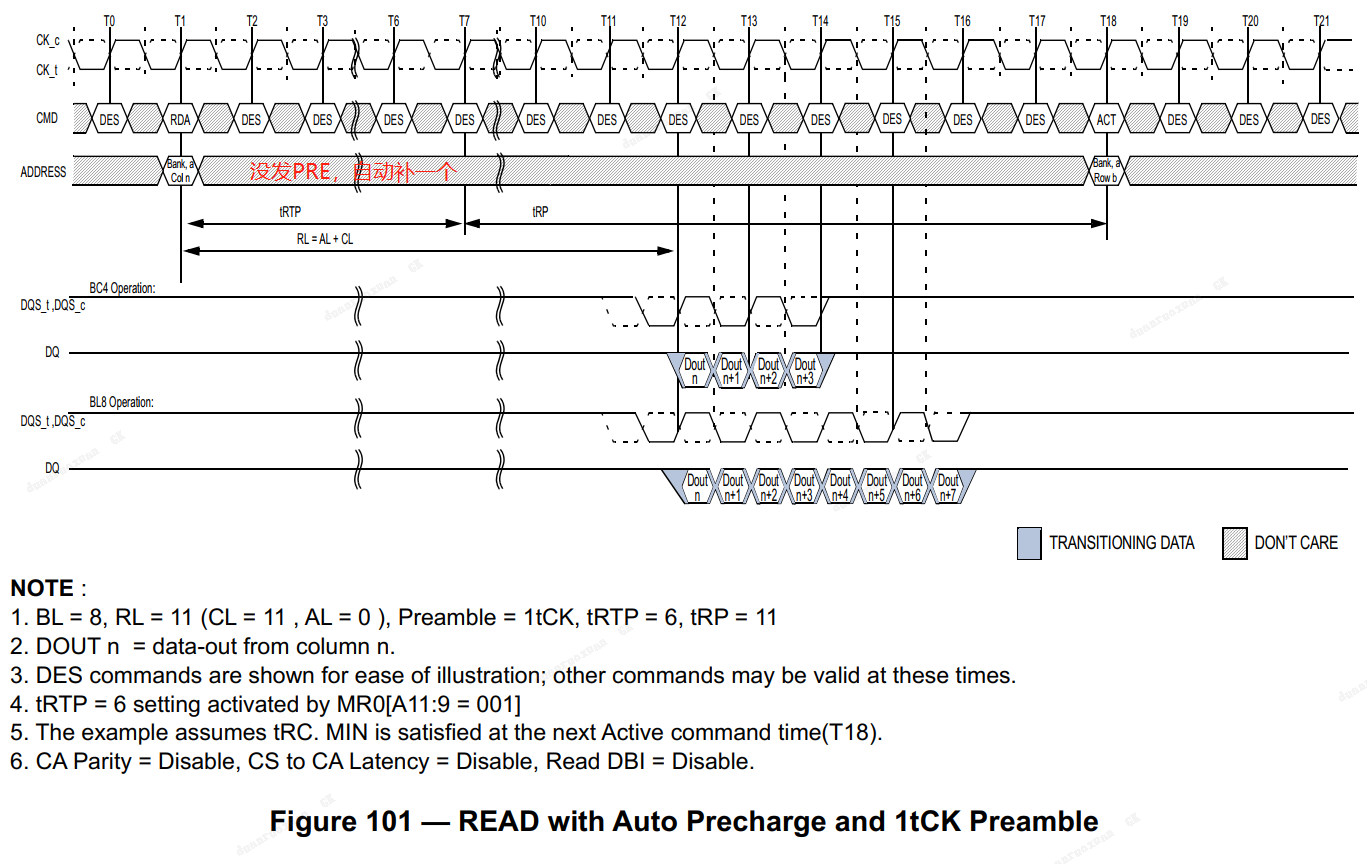

当在发出 Read 或 Write 命令时 A10 为高电平,则会启用自动预充电功能。该功能允许在突发读周期期间部分或完全隐藏预充电操作(取决于 CAS 延迟),从而提高系统在随机数据访问中的性能。RAS 锁定电路会在完成阵列恢复操作(满足 tRAS)后内部延迟预充电操作,因此可以在任何读操作中发出自动预充电命令。自动预充电也会在 Write 命令期间执行。自动预充电命令启动的预充电操作要等到突发写序列的最后一组数据正确存储在存储阵列中后才会开始。隐藏的 PRECHARGE 命令(自动预充电)发出后,指定时间 (tRP) 后,该 bank 将可用于后续行激活。

4.24读操作

4.24.2 READ Burst Operation

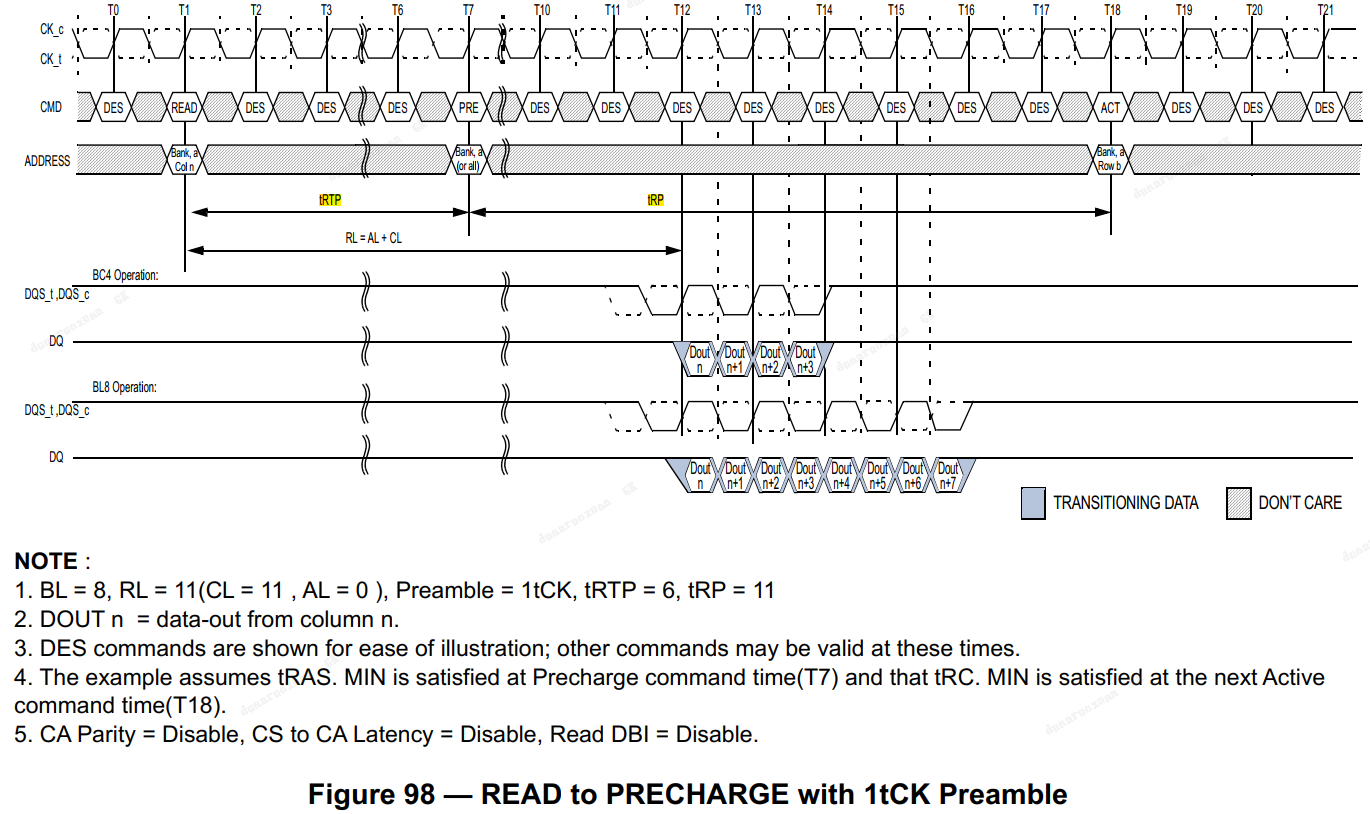

4.24.3 读后预充电时序

相同 bank 的最小外部 Read 命令到 Precharge 命令的间隔等于 AL + tRTP,其中 tRTP 是内部 Read 命令到 Precharge 命令的延迟。此外,还必须满足最小的 ACT 到 PRE 时序 tRAS。内部 Read 命令到 Precharge 命令延迟的最小值由 tRTP.min 给出。

当同时满足以下两个条件时,可以对同一 bank 发出新的激活命令:

- 从预充电开始的时钟周期起,最小 RAS 预充电时间 (tRP.MIN) 已满足。

- 从上一次 bank 激活开始,最小 RAS 周期时间 (tRC.MIN) 已满足。

图 98 到图 100 显示了 Read 命令后跟随 Precharge 命令的示例。

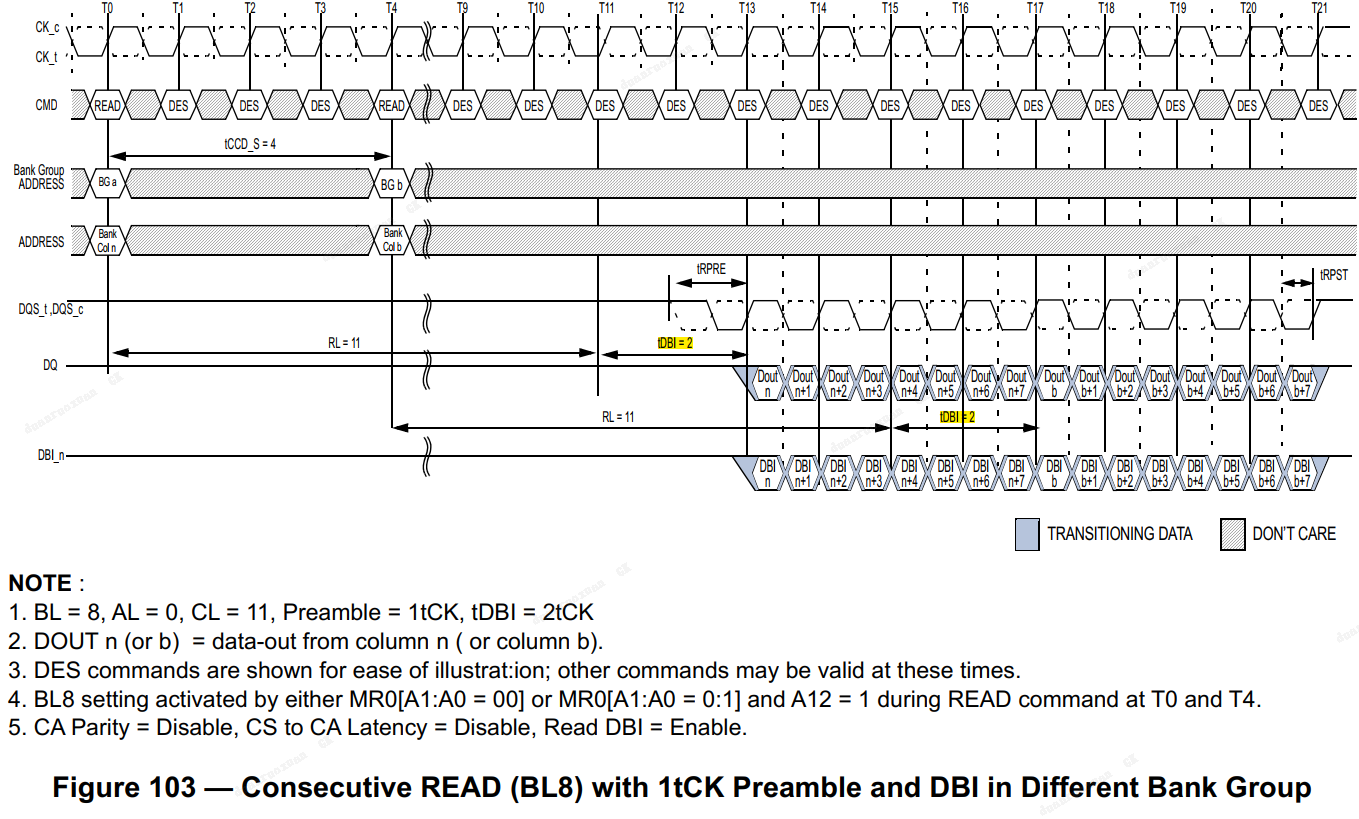

4.24.4 带DBI的读操作

读延时后面需要加个tDBI延时。

4.24.5 带CA奇偶校正的读操作

没啥区别。

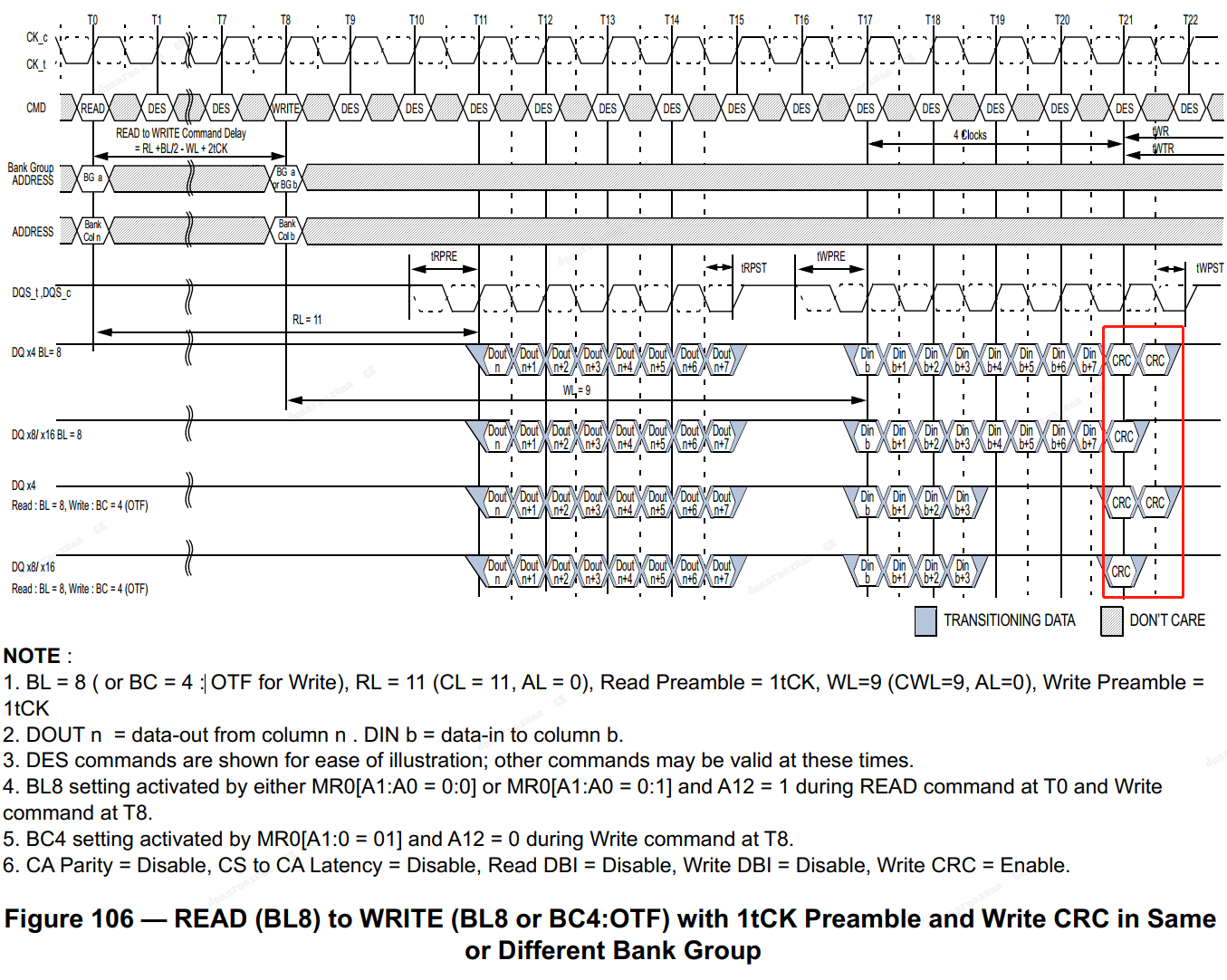

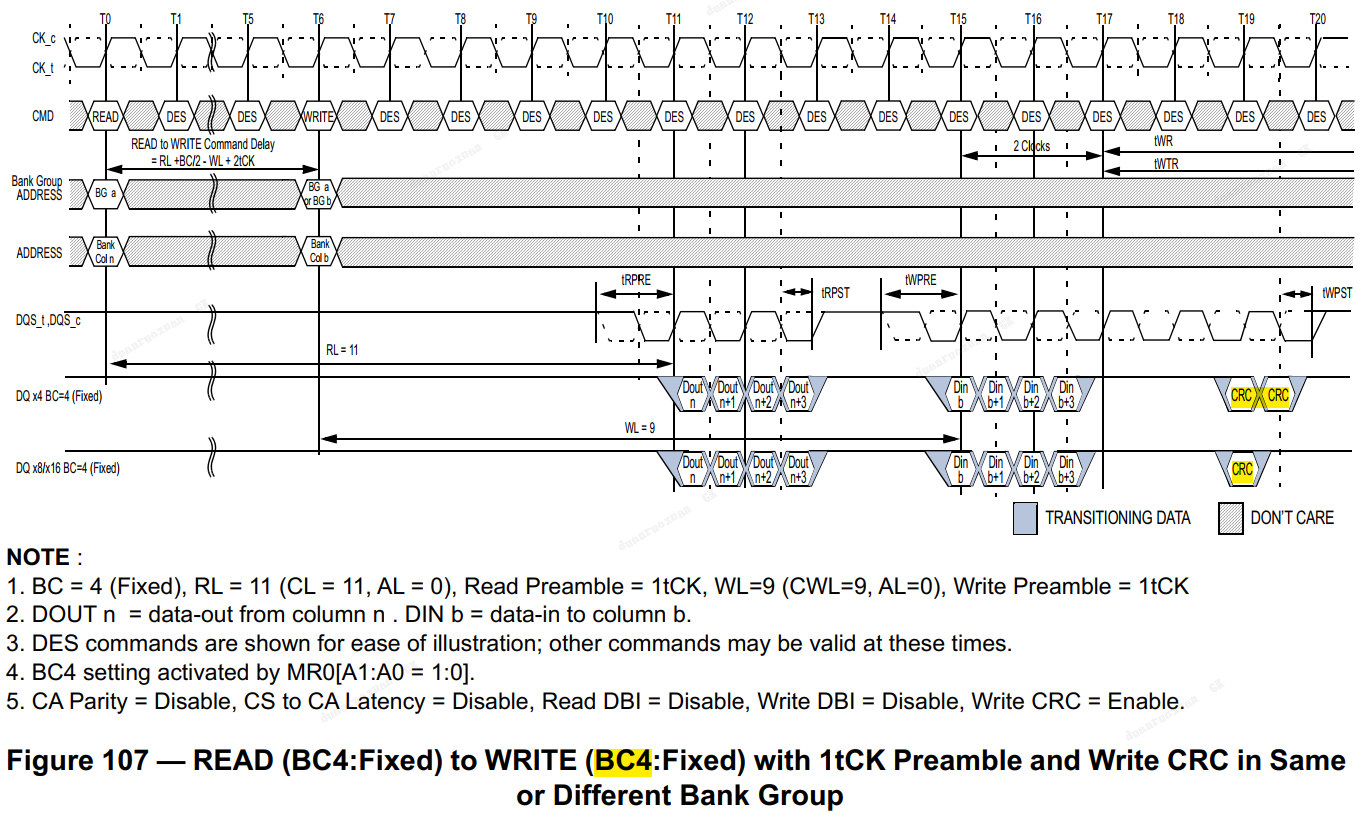

4.24.6 读到带CRC的写操作

BC4是在8数据后出CRC,中间缺的四个补1。

4.24.7 带CS to CL延时的读操作

4.25写操作

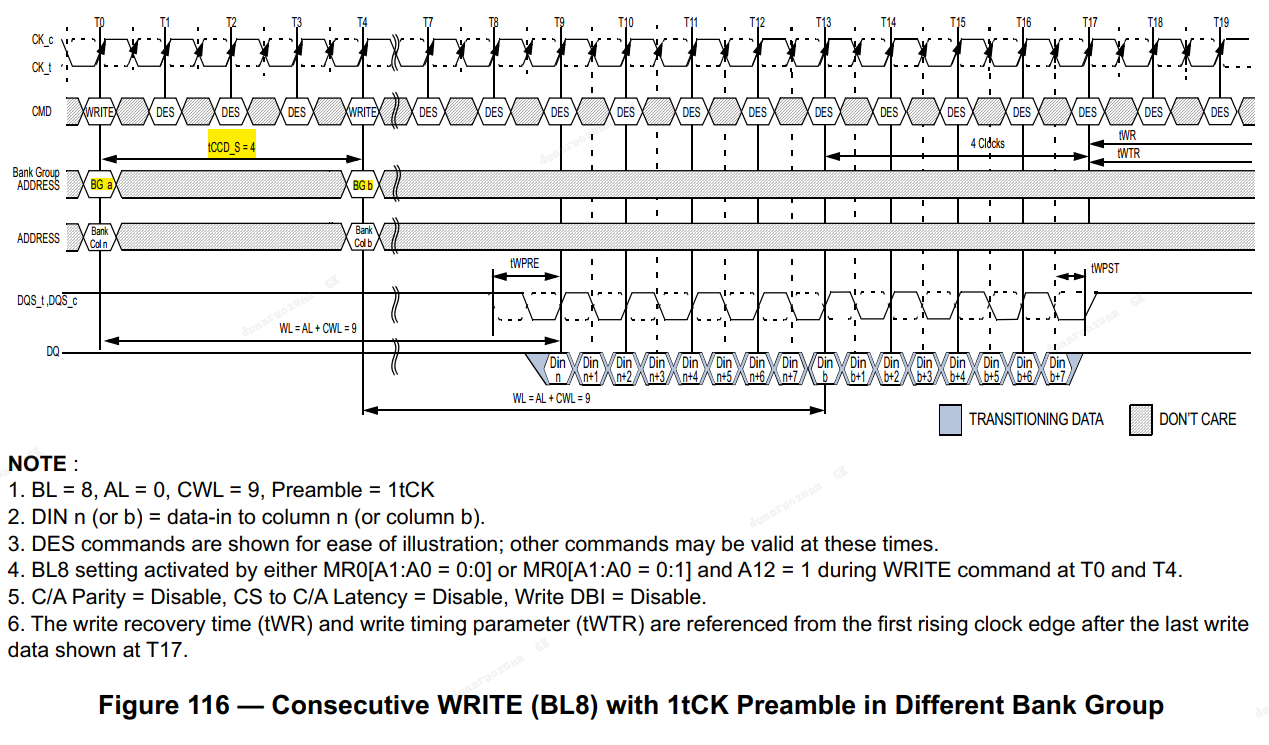

4.25.2 写突发操作

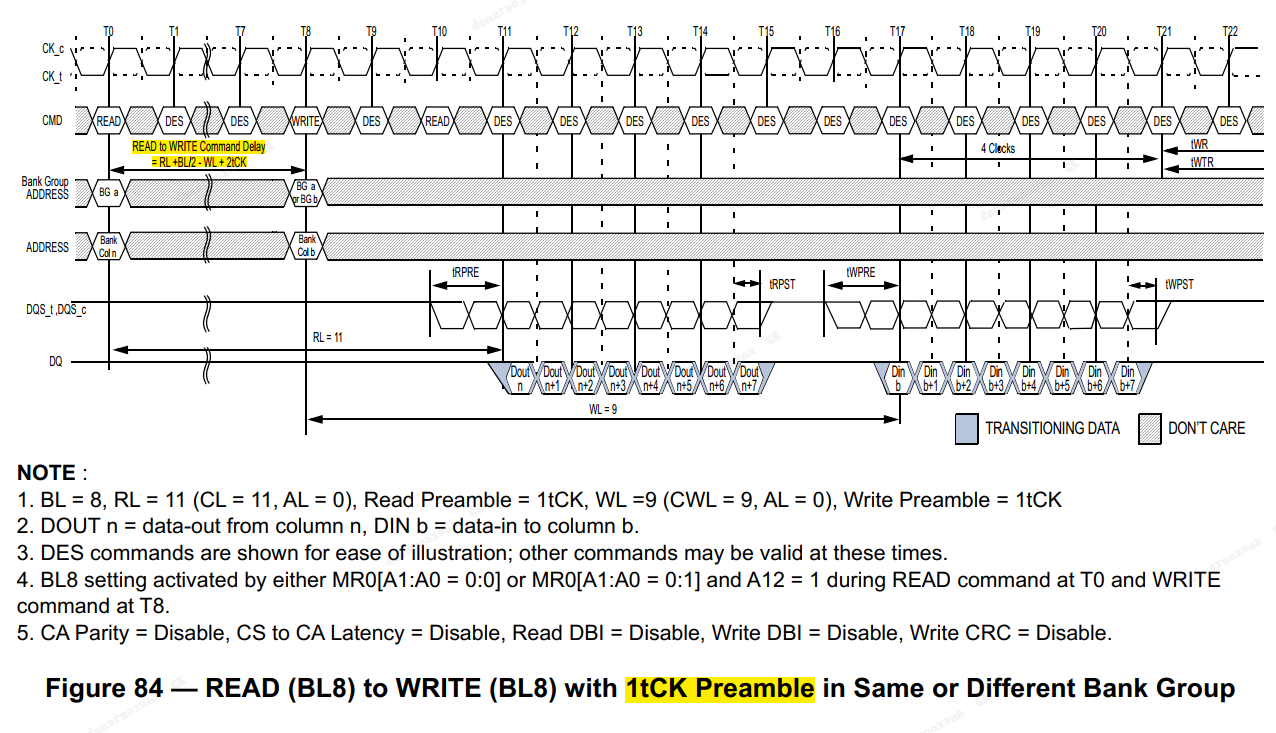

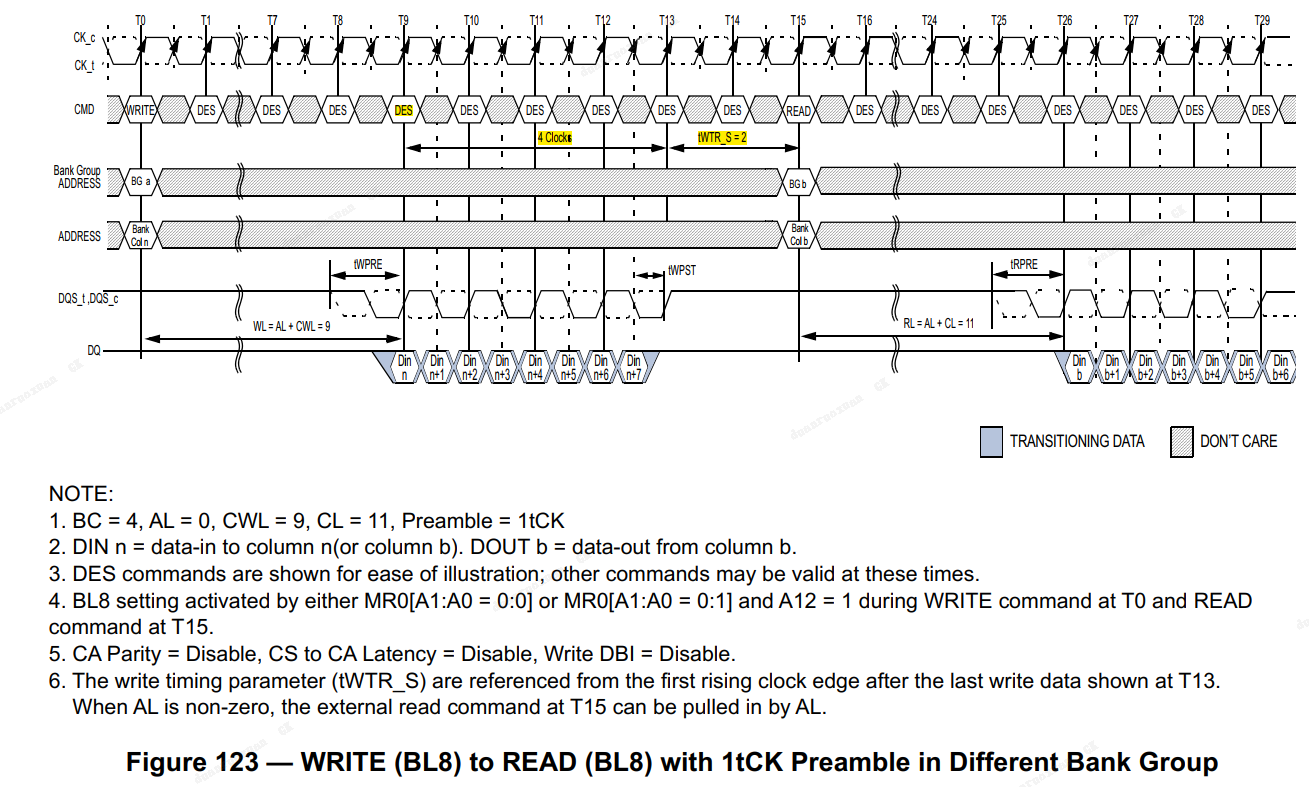

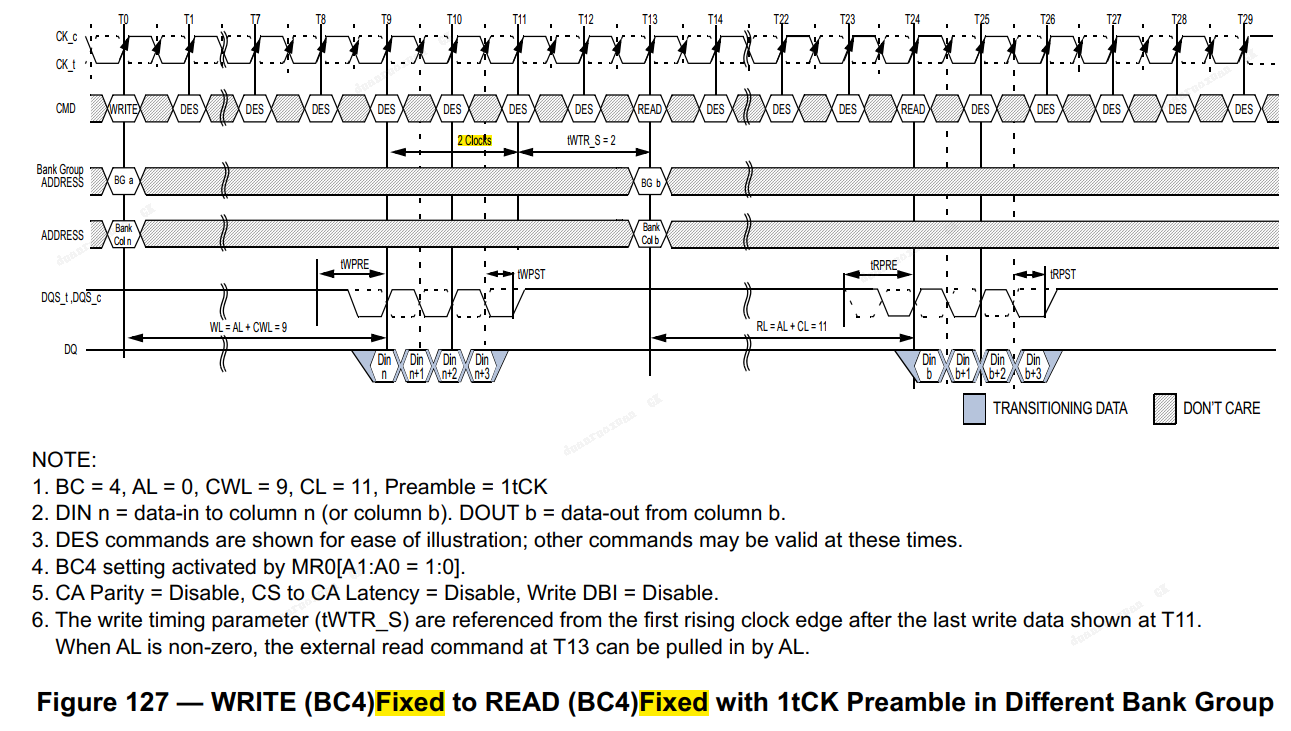

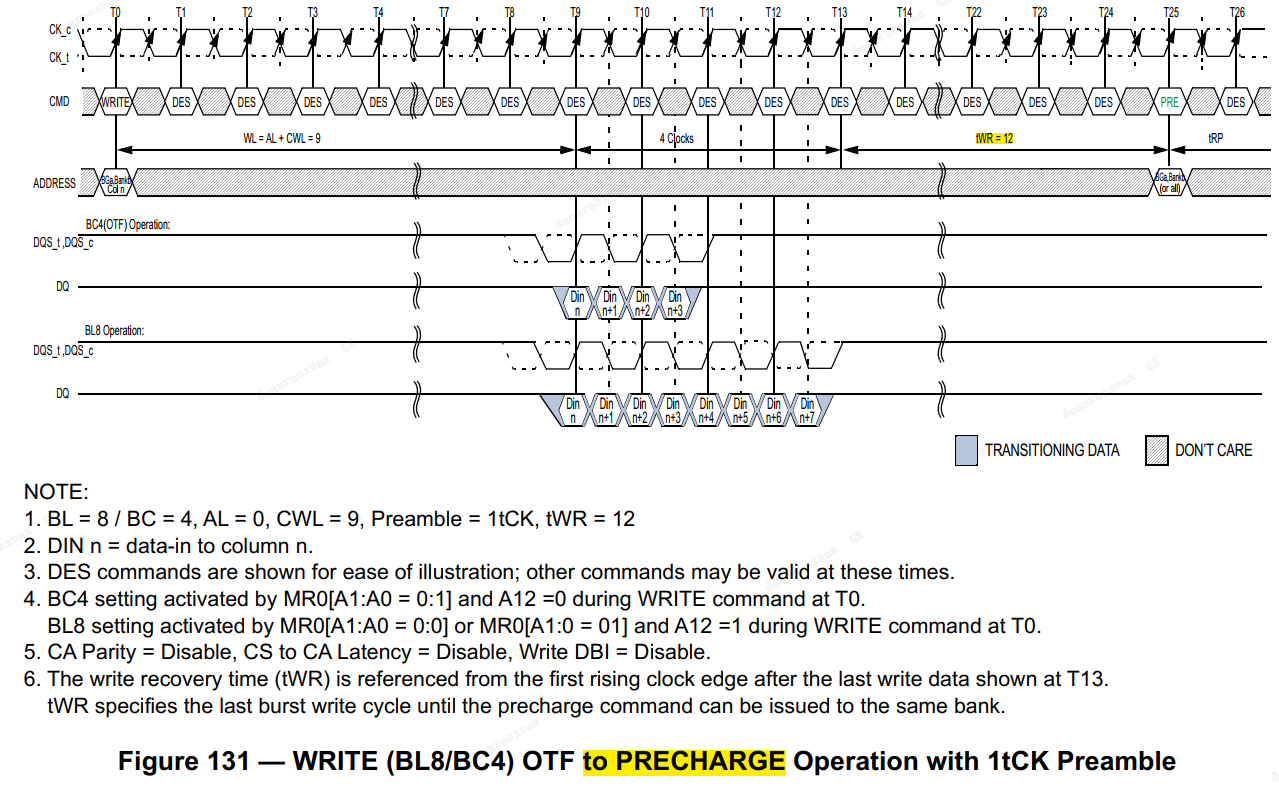

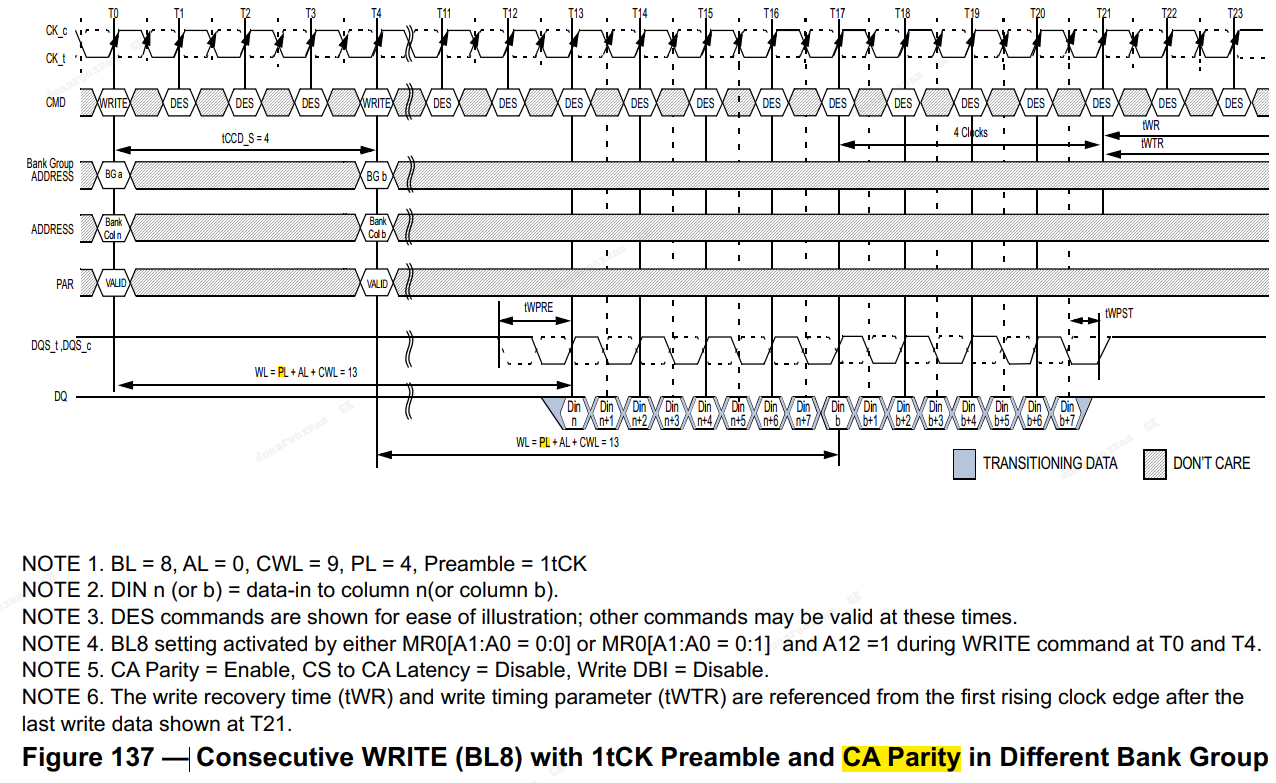

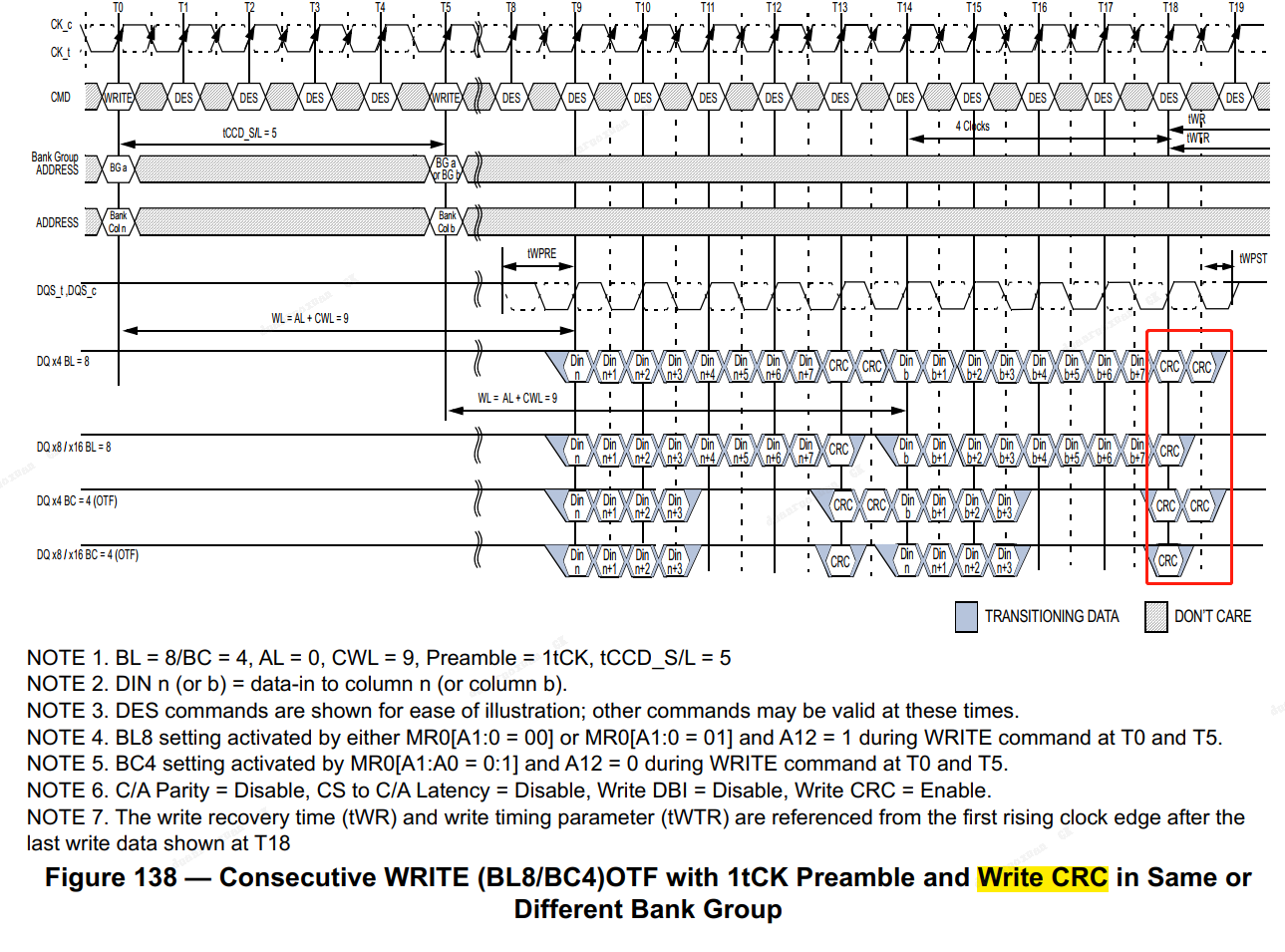

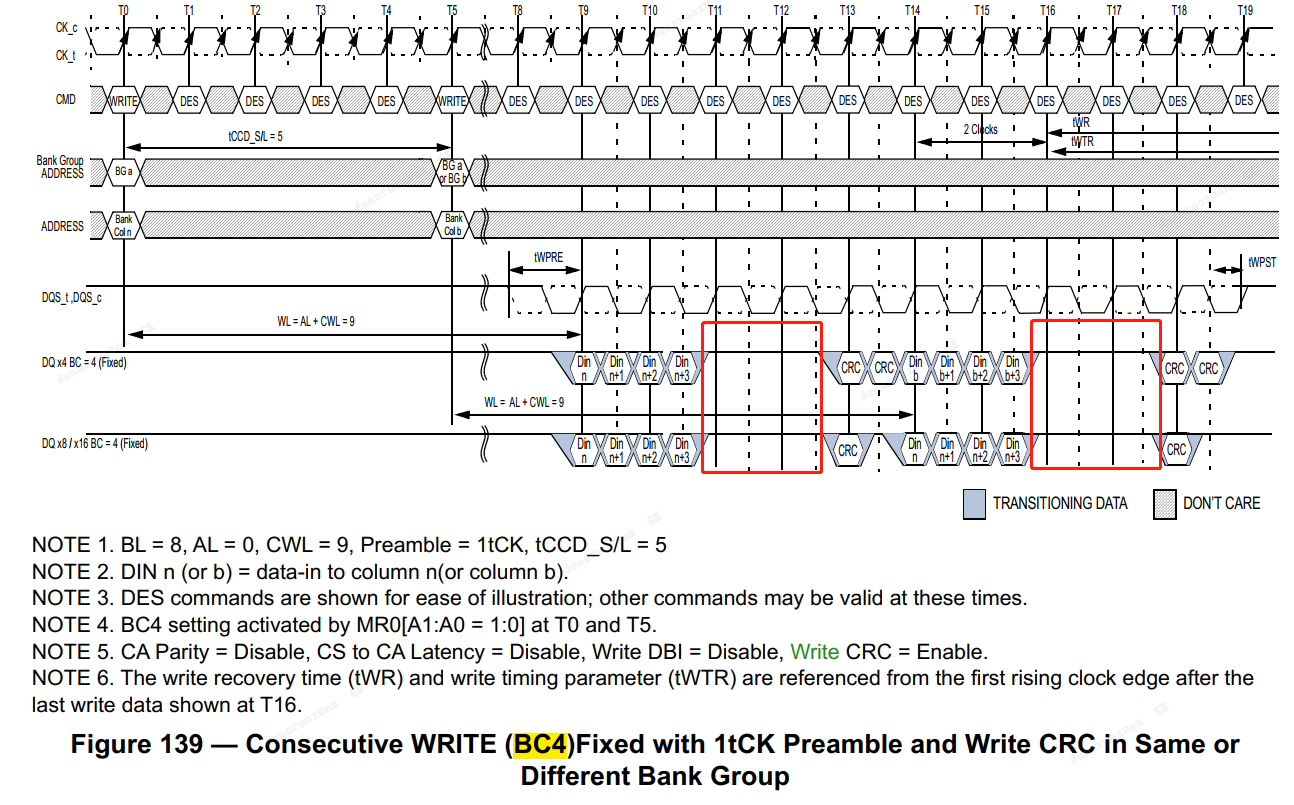

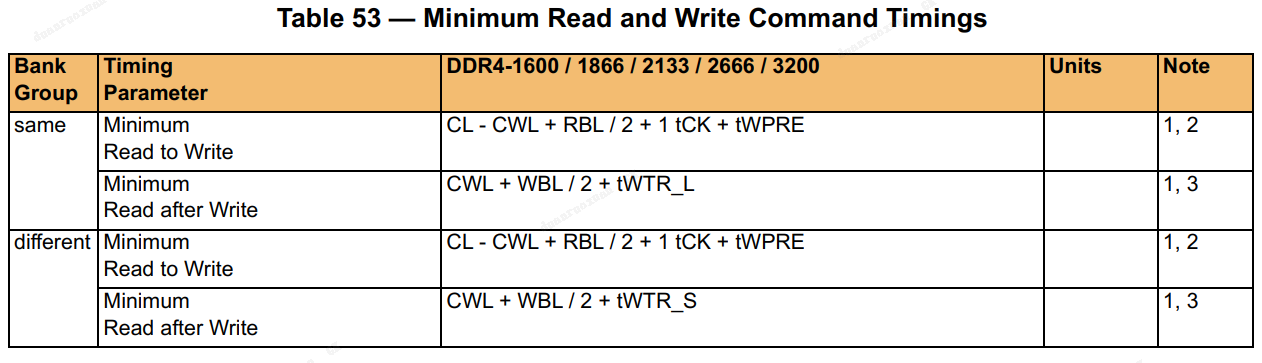

4.25.3 读写命令间隔

4.27 自刷新

4.27.1 低功耗自刷新

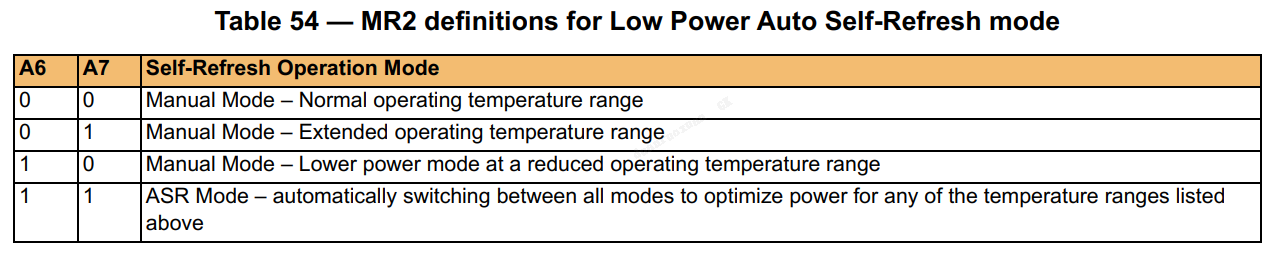

DDR4 设备在多个温度范围内支持低功耗自动自刷新 (LP ASR) 操作(见下方温度表)。

自动自刷新 (ASR)

DDR4 DRAM 提供自动自刷新模式 (ASR) 以便于应用。通过将 MR2 的 A6 和 A7 位设置为 1,可以启用 ASR 模式。DRAM 将根据支持的温度范围管理自刷新的进入。在此模式下,DRAM 会根据工作温度的变化调整自刷新速率:在低温下降低,在高温下提高。

手动模式

如果未启用 ASR 模式,则必须手动将低功耗 ASR 模式寄存器编程为上述三种自刷新操作模式之一。在此模式下,用户可以根据系统内存温度条件,在自刷新进入时选择固定的自刷新操作模式。用户有责任在自刷新操作期间保持所选模式所需的内存温度条件。用户可以在退出自刷新后和下一个自刷新进入之前更改所选模式。如果所选模式的温度条件被超出,可能会存在数据保留风险,从而导致数据丢失。

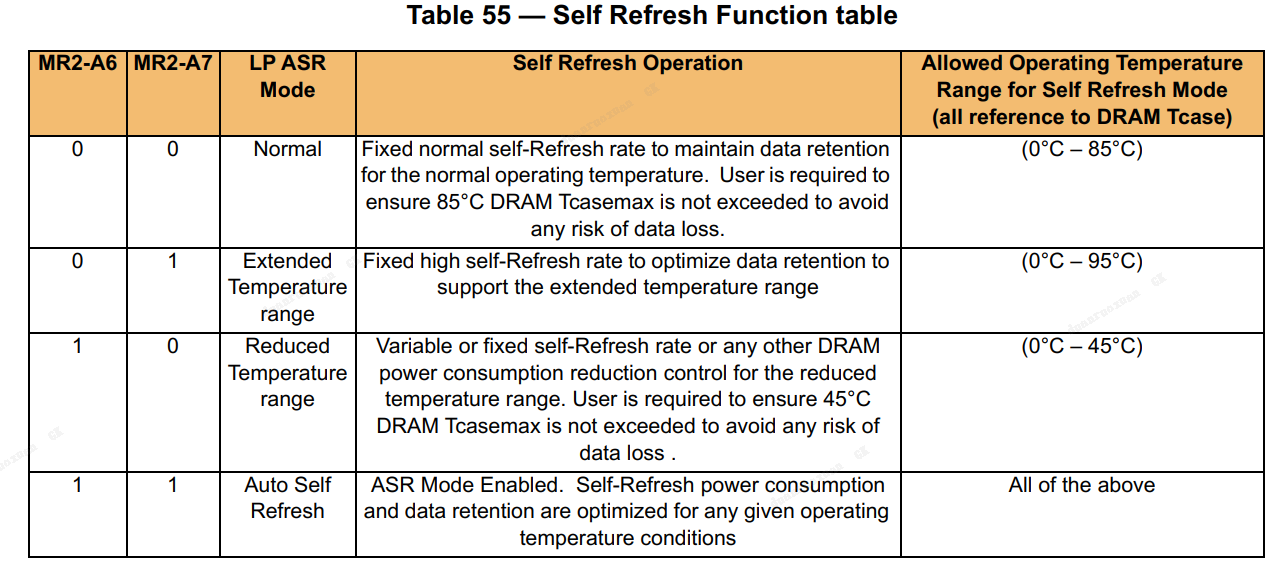

4.27.1 无操作命令自动刷新退出

使用无操作命令 (NOP) 的自刷新退出允许在活动 DRAM 与处于最大节能模式的 DRAM 之间使用共同的命令/地址总线。自刷新模式可以通过无操作命令 (NOP) 退出,前提条件如下:

- DRAM 进入自刷新模式时已禁用 CA 奇偶校验和 CAL。

- tMPX_S 和 tMPX_LH 满足要求。

- NOP 命令仅在 tMPX_LH 窗口期间发出。

在发出 SRX 命令后,tMPX_LH 窗口期间不允许发出其他命令。(见图 147)

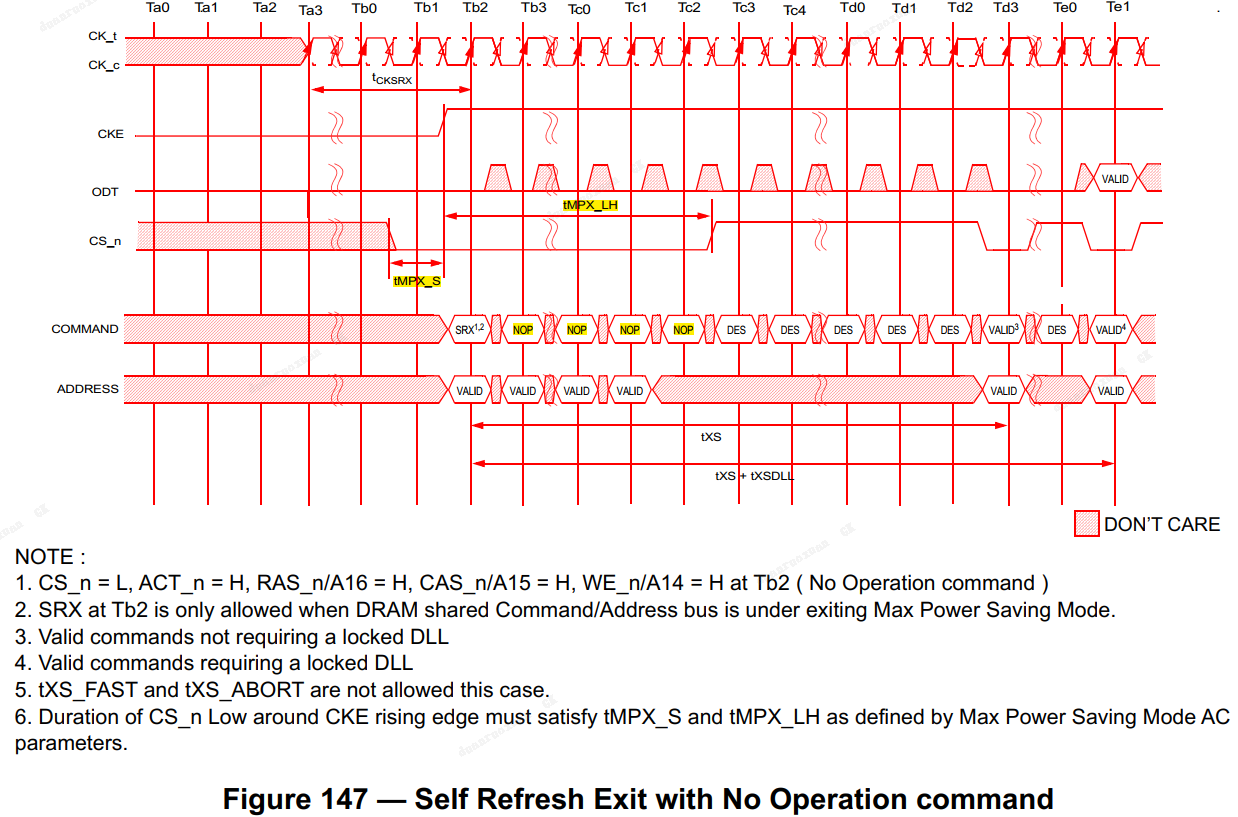

4.29 最大节能模式

此模式提供最低功耗消耗,类似于自刷新状态,但没有内部刷新活动。当 DDR4 SDRAM 处于最大节能模式时,它不需要保证数据保留,也不响应任何外部命令(除了最大节能模式退出和将 RESET_n 信号置为低电平),以最大限度地降低功耗。

4.29.2 Mode entry

最大节能模式通过 MRS 命令进入。对于具有共享控制/地址信号的设备,可以使用每个 DRAM 地址的 MRS 命令将单个 DRAM 设备置于最大节能模式。

请注意,在模式退出时,CS_n 到 CKE 的较长保持时间可能会导致 DRAM 功能失常,因此在进入最大节能模式的 MRS 命令之前,必须禁用 CA 奇偶校验、CAL 和 Gear Down 模式。

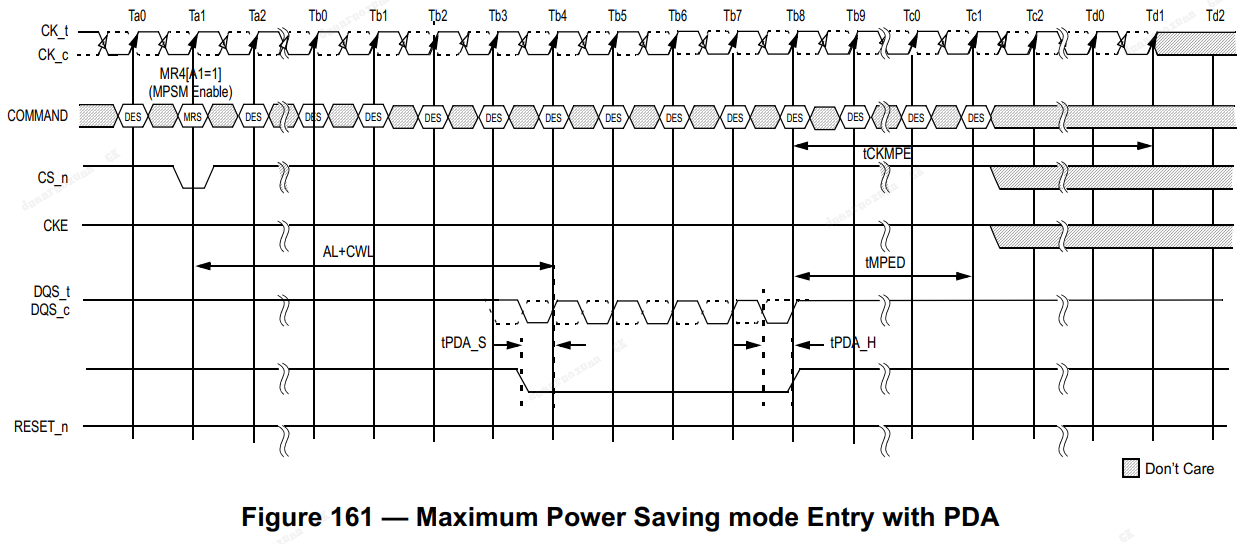

图 161 下方展示了与每个 DRAM 地址可寻址性 (PDA) 相关的最大节能模式所需的序列和时间参数。

在进入最大节能模式时,只有 DES 命令被允许,直到 tMPED 满足。在模式进入命令后的 tMPED 时期内,DRAM 不会对除 CS_n、CKE 和 RESET_n 信号之外的任何输入信号作出响应,所有其他输入信号可以处于高阻态 (High-Z)。时钟 (CLK) 应在 tCKMPE 时期内有效,然后可以设置为高阻态 (High-Z)。

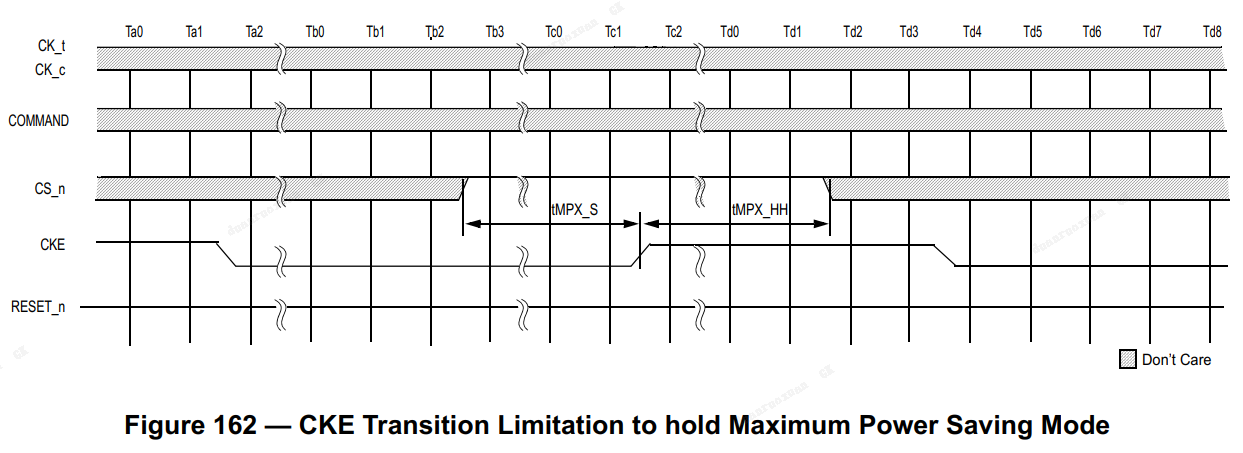

4.29.3 模式期间的CKE转换

CKE切换在DRAM处于最大省电模式时是允许的。为了防止设备退出该模式,CS_n应该在CKE从‘L’到‘H’的边缘时保持为‘高’,并遵循适当的设置时间tMPX_S和保持时间tMPX_HH。

4.29.4 模式退出

DRAM会监控CS_n信号电平,并在检测到CKE从‘L’到‘H’的转换时,根据CKE转换时的CS_n信号电平决定是退出省电模式还是继续保持在该模式中。由于在该模式下CK接收器已关闭,因此CS_n = ‘L’是在CKE信号上升沿被捕捉的。如果检测到CS_n信号为‘L’,DRAM将启动内部退出省电模式的程序。在设备退出最大省电模式之前,CK必须重新启动并在tCKMPX周期内保持稳定。在退出时间tXMP期间,DDR4 SDRAM不允许接收任何有效指令,除DES指令外;并且在tXMP_DLL期间,不允许任何需要锁定DLL的有效指令被发送给DDR4 SDRAM。

从该模式恢复时,DRAM会清除该模式的MRS位,这意味着MR4 [A1]的设置将自动变为‘0’。

4.31 CLK/read DQS时序参数

DDR4支持DLLOFF模式。DLL开/关模式下DQS与CLK的skew不同。

4.32 封装后修复(hPPR)

PPR全称为Post Package Repair,中文直译为封装后修复,其意为当一个row损坏后,利用算法将损坏的row映射到冗余的row上,利用冗余的row来进行数据传输。PPR有两种修复方式,一种为hPPR,一种为sPPR。

hPPR为硬件修复,修复后不可更改,内存控制器需要记录此次修复,因为此次修复无法更改,坏道已经映射到了冗余的通道上,若下次再发送相同的hPPR操作,DRAM将无法执行此操作。修复是在硬件层面上的走线更改,好处是修复了这一次后就一劳永逸,掉电后不丢失,重新启动后,不用再次修复。

sPPR为软件修复,是更改颗粒里面的软路由,并且还可以被其它的sPPR命令以及hPPR命令更改。掉电后丢失,且下次启动后发现仍然有坏row,仍然要启动sPPR进行修复。

在DDR4的标准手册中,定义了PPR修复功能在4Gb容量中是可选的,但是8Gb以及8Gb以上的容量,必须配备PPR功能,即配备冗余的row。并且还说明,PPR功能需要视每个内存生产商而定,这给了生产商很大的自由度。

在hPPR中,DDR4可以对每个BG进行一个Row的修复,也就是说每个BG有一个冗余的Row。内存控制器需对每次hPPR的修复进行记录。

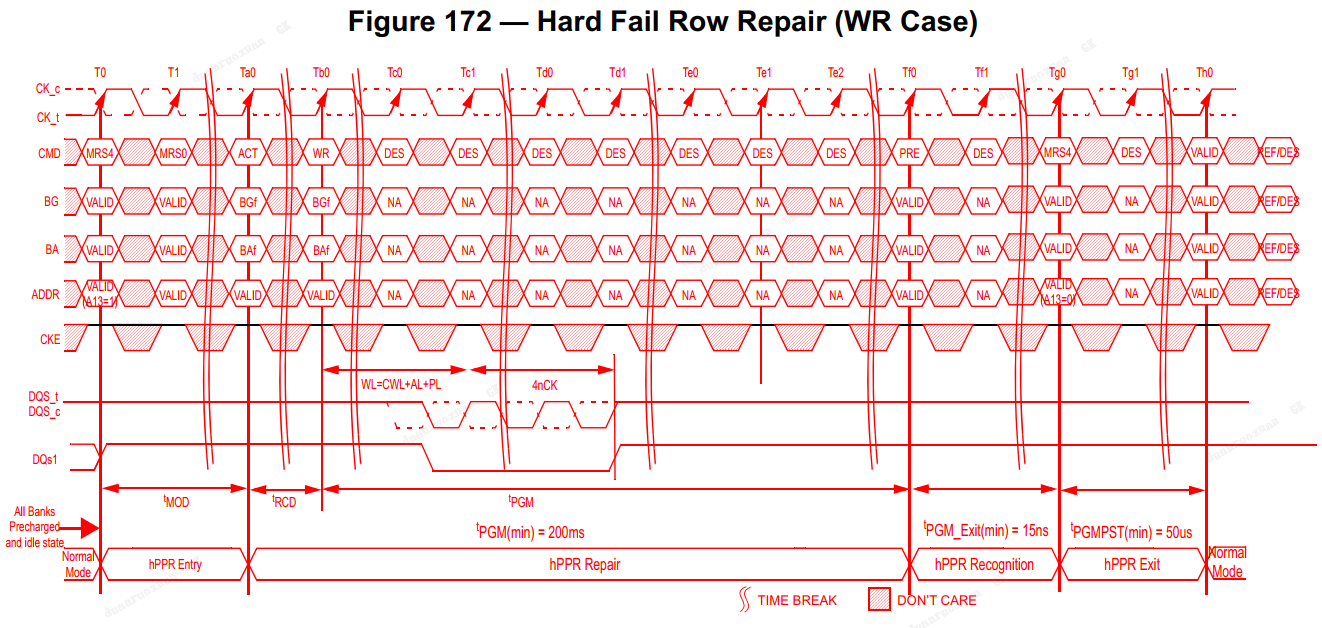

有两种方法可以进行hPPR,一种为利用WRA命令,其后进行REF操作从而保证数据不被改变(正在修复坏道的bank的数据不会被保留,此时BA[0] Don‘t Care)(因为hPPR用时较长,故为了保持DRAM中的数据不丢失,可以在发送WRA命令后发送REF命令)。另一种为直接发送WR命令,不发送REF命令,此情况下,由于没有REF命令,故不能保证DRAM中的数据仍旧能够保持。

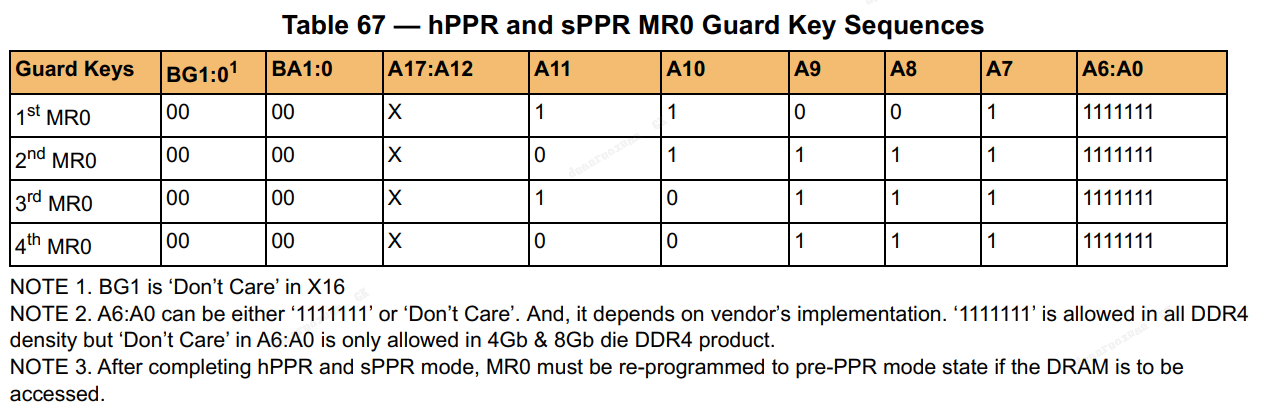

当进入hPPR或sPPR模式时,需要通过一系列的MRS设置来避免非法的hPPR/sPPR操作,这个一系列的MRS设置称为Guard Key。

在进入hPPR模式(MR4的A13=1)后需要立即设置4个MRS命令来设置MR0,从而启动Guard Key。在对MR0进行四个连续的MRS命令设置时,不允许其他命令发送,也不允许对其它的MR寄存器进行设置的MRS命令,必须将MR0全部设置完成后,上了锁之后在发送其它命令。假设在设置MR0时被其它命令中断(这个命令称为offending command),或者在设置MR0时未按照规定的顺序进行设置,则不会进入hPPR/sPPR模式,offending command可能会执行错误,offending command不会造成DRAM锁定(lock up)。

另外,当进入hPPR或sPPR的顺序被中断,后续的ACT和WR命令将会被视作正常操作DRAM的命令。如果hPPR操作过早地、贸然地被终止,则发送后续的hPPR或sPPR操作前,MR4的A13必须设置为0;如果sPPR操作过早地、贸然地被终止,则发送后续的sPPR或hPPR操作前,MR4的A5必须被设置为0。如果未能按照规定的顺序启动Guard Key,DRAM并不会提供一个错误指示信号。

表67展示了进入Guard Key的顺序,MRS需要对MR0进行四次设置。

4.32.1 以WRA命令进行hPPR(可以发送REF)

- 在进入hPPR模式之前,所有的bank都必须Precharge;必须关闭DBI和CRC。

- 将MR4的A13设置为1,并等待tMOD时长。

- 启动Guard Key:按表67发送4个MR0的MRS命令,每个MRS命令需等待tMOD时长。

- 在发送ACT命令时指明要修复的Bank和Row地址。写数据用于选择Rank中的具体的DRAM。

- 在tRCD时长后,发送WRA,并跟随一个有效地址。虽然是一个有效地址,但DRAM在此时Don't Care。

- 等待WL后(WL=CWL+AL+PL),修复坏道的DRAM的所有DQ pin将会拉低四个CK周期。如果DRAM的所有DQ持续拉高大于或等于两个CK周期,那么DRAM将不会执行sPPR操作,如果发送了REF命令,DRAM的数据将会保持;如果所有的DQ没有保持四个CK的低电平,也没有保持大于等于两个周期的高电平,则sPPR操作是否执行了未可知。

- 等待tPGM时长,DRAM在此时间内会进行内部修复坏道,之后发送PRE命令。

- 在PRE命令后等待tPGM_Exit。

- 通过设置MR4的A13=0来退出hPPR。

- 对于相同的BG发送多个sPPR请求,最近的sPPR及其对应的地址将会覆盖掉先前发送的地址;对于不同的BG进行sPPR,重复步骤2到9。在发送hPPR前,可以进行sPPR。

- 如果有多个row地址损坏,重复2到9步骤。

另外,在hPPR模式下,当之前发送的命令为WRA时,后续可以发送REF命令,具体时间为在发送WRA命令后的PL+WL+BL/2+tWR+tRP时间之后,且REF命令需要在tPGM和tPGMPST时间内发送。可以按tREFI时间间隔正常发送REF命令,也可以按照tREFI/2的间隔发送,也可以按tREFI/4的间隔发送,但是时间间隔不能更小了。发送REF命令后,DRAM将会正常执行REF命令,除了正在修复的坏道的bank,其它的bank数据都可以被保留,当然在此过程中BA[0] don't care。在tPGM时间内只允许发送REF命令,否则无法完成hPPR修复。

一旦退出hPPR修复模式,为了验证对应的坏道是否映射到了冗余的通道上,用户可以给对应的坏道进行写数据操作,并将其回读,从而查看是否修复完成。当然,上述操作需要在hPPR退出后的tPGMPST时长后才能进行。

4.32.2 以WR命令进行hPPR(不允许发送REF)

在手册中,4.32.2章节所述的步骤是完全照抄4.32.1章节的步骤,根本没有改动,最主要体现在没有删除第六步的关于REF命令的操作的话语(文档错误??)。尽管手册上在步骤11之后的下一段写了一句“不允许REF命令”。

- 在进入hPPR模式之前,所有的bank都必须Precharge;必须关闭DBI和CRC。

- 将MR4的A13设置为1,并等待tMOD时长。

- 启动Guard Key:按表67发送4个MR0的MRS命令,每个MRS命令需等待tMOD时长。

- 在发送ACT命令时指明要修复的Bank和Row地址。

- 在tRCD时长后,发送WR,并跟随一个有效地址。虽然是一个有效地址,但DRAM在此时Don't Care。

- 等待WL后(WL=CWL+AL+PL),修复坏道的DRAM的所有DQ pin将会拉低四个CK周期。如果DRAM的所有DQ持续拉高大于或等于两个CK周期,那么DRAM将不会执行hPPR操作;如果所有的DQ没有保持四个CK的低电平,也没有保持大于等于两个周期的高电平,则hPPR操作是否执行了未可知。

- 等待tPGM时长,DRAM在此时间内会进行内部修复坏道。发送PRE命令。

- 在PRE命令后等待tPGM_Exit时长。

- 通过设置MR4的A13=0来退出hPPR。

- 在tPGMPST时间后,DDR4可以正常操作。

- 如果有多个row地址损坏,重复2到9步骤。

在上述操作中,在进入hPPR后和退出hPPR模式前不允许发送REF命令。

一旦退出hPPR修复模式,为了验证对应的坏道是否映射到了冗余的通道上,用户可以给对应的坏道进行写数据操作,并将其回读,从而查看是否修复完成。当然,上述操作需要在hPPR退出后的tPGMPST时长后才能进行。

图172为上述时序过程。

4.33 封装后修复(软件级的封装后修复)

相较于hPPR,sPPR修复所需的时间更短,但其并不像hPPR一样修复之后一劳永逸,sPPR修复后,掉电或者复位操作,会丢失修复的结果。表70展示了两者之间的联系与区别。

| Topic | sPPR | hPPR | Note |

| 修复后可保持的时间 | 非永久性修复 | 永久性修复 | 在下电或复位后,sPPR的修复信息会被丢失 |

| tPGM,修复所需时间 | WL+4tCK+tWR | >1000ms(tPGMa) >2000ms(tPGMb) | |

| 每个BG可修复的row | 1个row/BG | 1个row/BG | |

| 在同一BG内同时使用sPPR和hPPR | 在sPPR对另一不同的BG进行修复前,可以发送hPPR(这个框里的内容总感觉与Topic不一致) | 在进行hPPR之前需清除sPPR的信息。 | 清除sPPR有两种方式

|

| 修复所需的方式 | 发送WR命令 | 发送WRA或WR命令 | |

| 未进行修复的bank在修复期间是否能保留原有数据 | 可以 |

| WRA命令需要配合REF命令一起使用 |

| 需要修复的bank在在修复期间是否能保留原有数据 | 可以,除了需要修复的row不能保留原有数据。 | 无法保留 | sPPR需要在REF发送后的tREF时长后进行 |

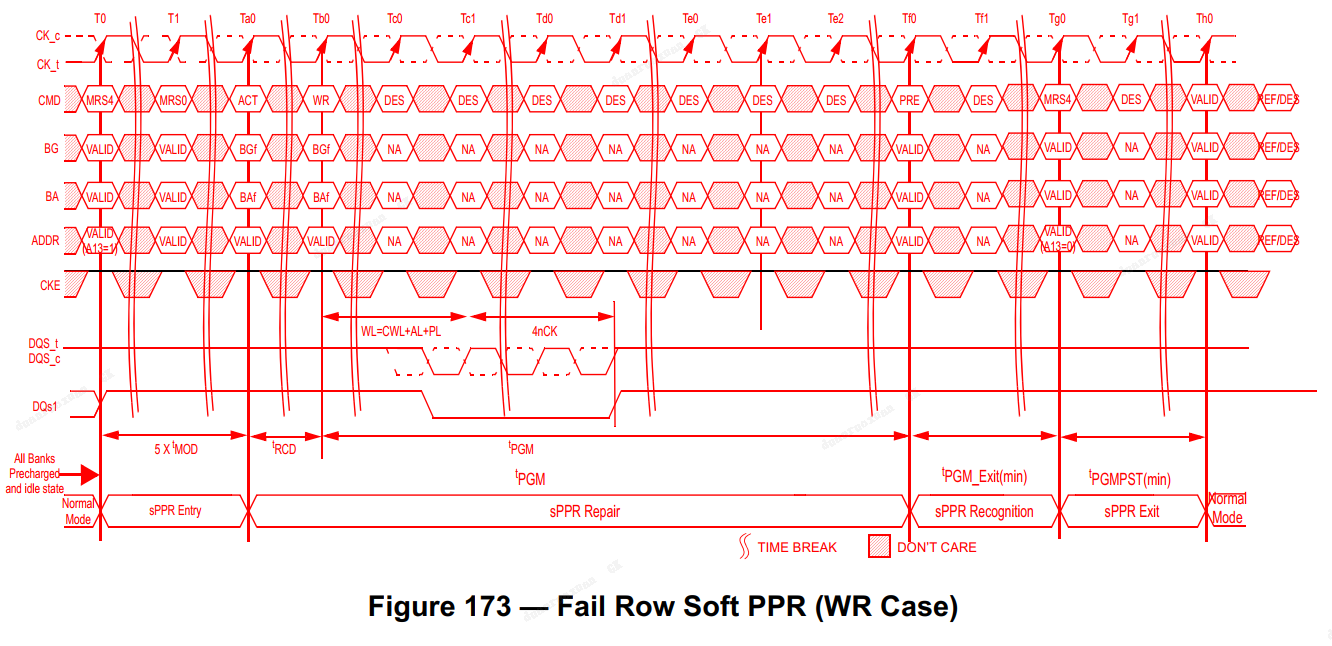

sPPR借助MR4的A5进入sPPR,与hPPR相同,sPPR也需要表67所述的Guard Key来让sPPR成功执行。在进入sPPR之前,需要发送hPPR退出命令以及sPPR退出命令。进入sPPR后,需要发送ACT命令来确定目标bank以及需要修复的目标row。在tRCD时序后,可以发送WR命令进行修复。经过写恢复时间和PRE所需的时间后,可以退出sPPR模式,之后便可对DRAM进行正常操作。只要VDD电压保持在正常的工作范围内,则DRAM将会保留sPPR修复的结果。如果DRAM掉电,或DRAM进行了复位,则sPPR修复的结果将会丢失。在进入hPPR模式前,必须通过下电操作或复位后重新初始化的操作来清除sPPR的修复结果。

DDR4的sPPR可以对每个BG进行一个row的修复,然而,当hPPR修复占用了BG中这个冗余row的资源,那么将不能再使用sPPR对此BG进行修复。如果BG中的冗余row已经被占用了,也就是说没有可供利用的row进行hPPR或sPPR修复,则DRAM将会忽略对该BG发送的PPR操作。对于4Gb和8Gb容量的DRAM,sPPR是选配的,但是对于大于8Gb的DRAM,必须配备sPPR模式。

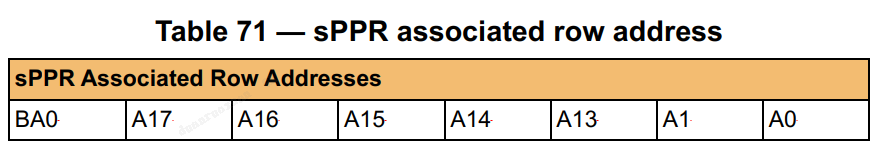

当接收到sPPR时,除了需要修复的目标row以及associated row,bank将会保存DRAM其它阵列中的数据(此对于大于8Gb的DRAM是这样的,对于小于等于8Gb的DRAM,这种情况是可选的)。如果用户并不要求在sPPR下保存阵列中的数据,则对associated row的操作会被忽略。如果要求将数据保存在bank中,则在执行sPPR之前,目标row和associated row应该备份起来并在sPPR结束后恢复其存储的数据(具体如何操作,手册上未提及)。sPPR的associated row地址如下表所示。

4.33.1 sPPR操作流程

在sPPR操作期间,不允许发送REF命令。

- 在进入sPPR模式之前,所有的bank都必须Precharge;必须关闭DBI和CRC。

- 将MR4的A5设置为1,并等待tMOD时长。

- 启动Guard Key:按表67发送4个MR0的MRS命令,每个MRS命令需等待tMOD时长。

- 在发送ACT命令时指明要修复Bank和Row地址。

- 在tRCD时长后,发送WR,并跟随一个有效地址。虽然是一个有效地址,但DRAM在此时Don't Care。

- 等待WL后(WL=CWL+AL+PL),修复坏道的DRAM的所有DQ pin将会拉低四个CK周期。如果DRAM的所有DQ持续拉高大于或等于两个CK周期,那么DRAM将不会执行sPPR操作;如果所有的DQ没有保持四个CK的低电平,也没有保持大于等于两个周期的高电平,则sPPR操作是否执行了未可知。

- 等待tWR时长,DRAM在此时间内会进行内部修复坏道。发送PRE命令。

- 在PRE命令后等待20ns。

- 通过设置MR4的A5=0来退出sPPR。

- 在对BG进行hPPR之前可以进行sPPR操作。当多个sPPR请求发送到同一个BG,则最后的一个sPPR对应的地址将会覆盖之前的地址。对于不同的BG进行sPPR操作,重复步骤2到9。

退出sPPR后,为了验证其是否修复完成,可以写数据并读数据来进行确认。图173为sPPR的时序。

5.ODT

5.1 ODT模式寄存器和ODT状态表

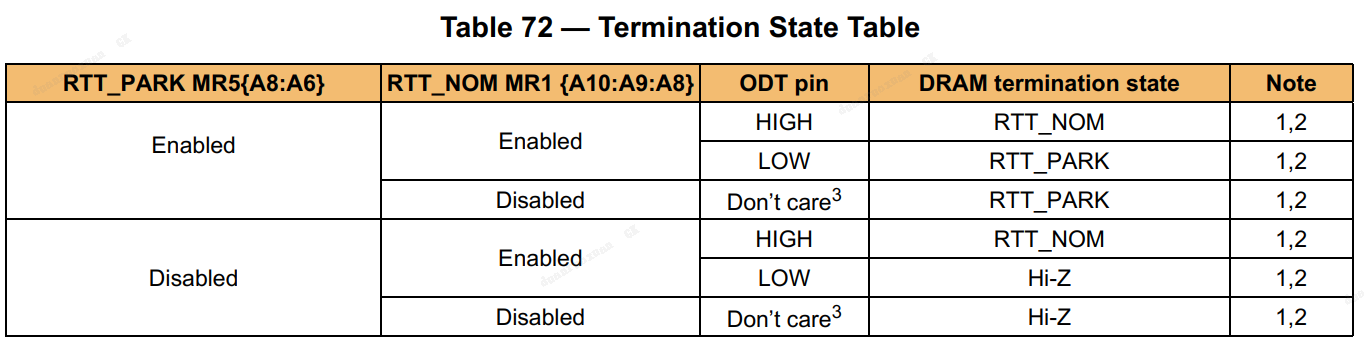

DDR4的ODT有四种状态:电阻disable、RTT_WR、RTT_NOM以及RTT_PARK。如果MR1 A[10:8]或MR2 A[10:9]或MR5 A[8:6]其中的一个或几个不是全零的情况下,则会使能ODT模式,同时,这些MR寄存器中也设置了终端电阻的阻值到底是多少。

进入自刷新模式后,DRAM自动disable ODT电阻并无视MR的设置将其设置为高阻态。

应用举例:内存控制器可以结合ODT pin,在WR/RD命令时控制每个RTT的阻值具体是多少。

- RTT_WR:无论ODT pin的电平为高还是为低,当rank(注意这里是rank)接收写入颗粒的数据时,终端电阻阻值为RTT_WR。

- RTT_NOM:假设MR1的ODT没有被disable,当ODT pin拉高时,此时终端电阻阻值为RTT_NOM。

- RTT_PARK:给MR5以合适的设置,且当ODT pin脚为低时,终端电阻阻值为RTT_PARK。

- 电阻Disable:在发送READ命令后,DRAM驱动数据回传到控制器时,会disable终端电阻。disable的时间起点为发送READ命令之后的(RL-X)个CK周期,持续时长为BL/2 + X个CK周期。其中X为前导时钟长度。

RTT阻值的优先级如下:电阻Disable > RTT_WR > RTT_NOM > RTT_PARK。优先级表明,当ODT pin为高电平时,如果WR命令到来,则此时对应的终端电阻为RTT_WR而非RTT_NOM;如果此时为RD命令,即使ODT pin为高,回传数据时DARM将会disable终端电阻。

表72为具体的终端电阻状态。

5.2 同步ODT模式

当DLL打开并被锁定时,都将选择同步的ODT模式。同步ODT模式包括:

- 当CKE为高时任何bank被激活

- 当CKE为高时的刷新

- 当CKE为高时DRAM的idle状态

- Active Power downw模式

- Precharge Power down模式

其中第四点和第五点要根据4.28章节的Power Down内容给出解释,如下:

如果任何命令完成后,所有的bank都被关闭,此时进入power down模式,称为precharge Power Down模式;如果命令完成后,有任何一个bank打开,此时进入Power down模式称为active power down模式。详见表56的描述。

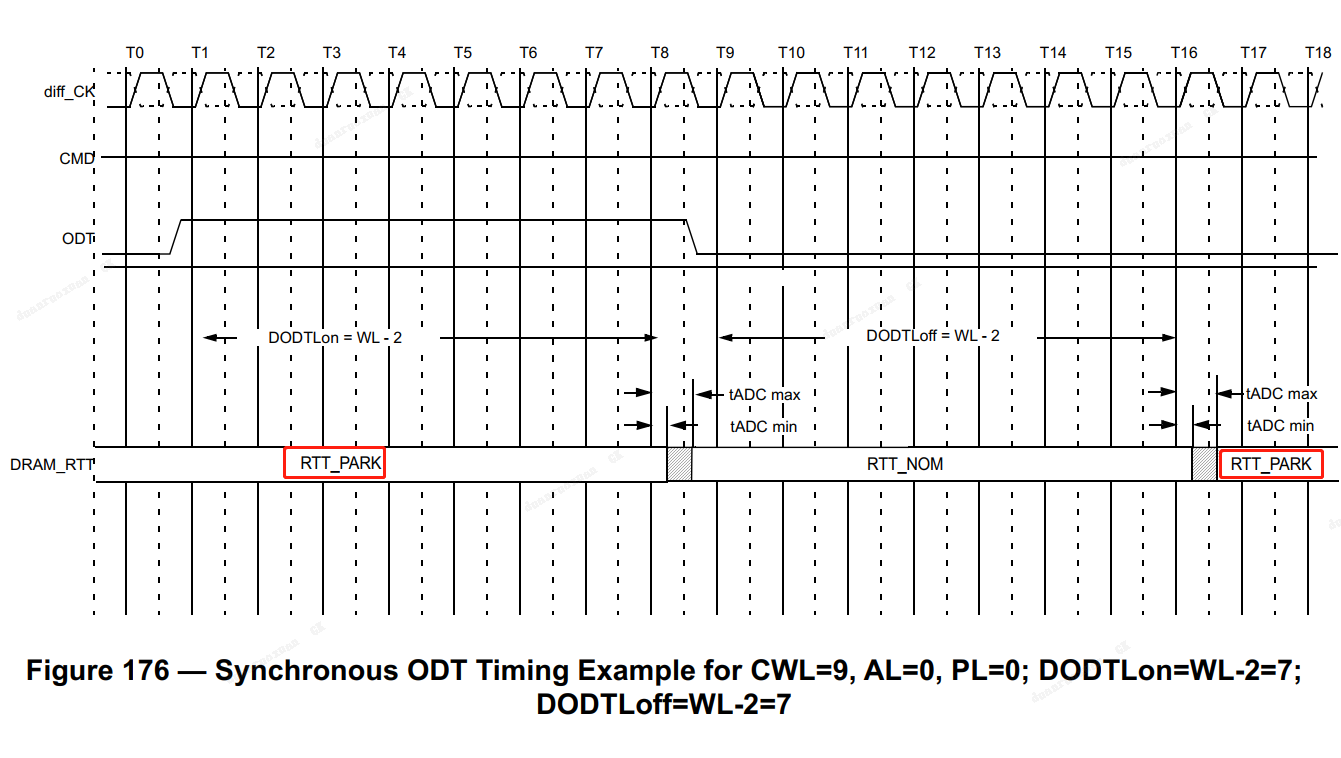

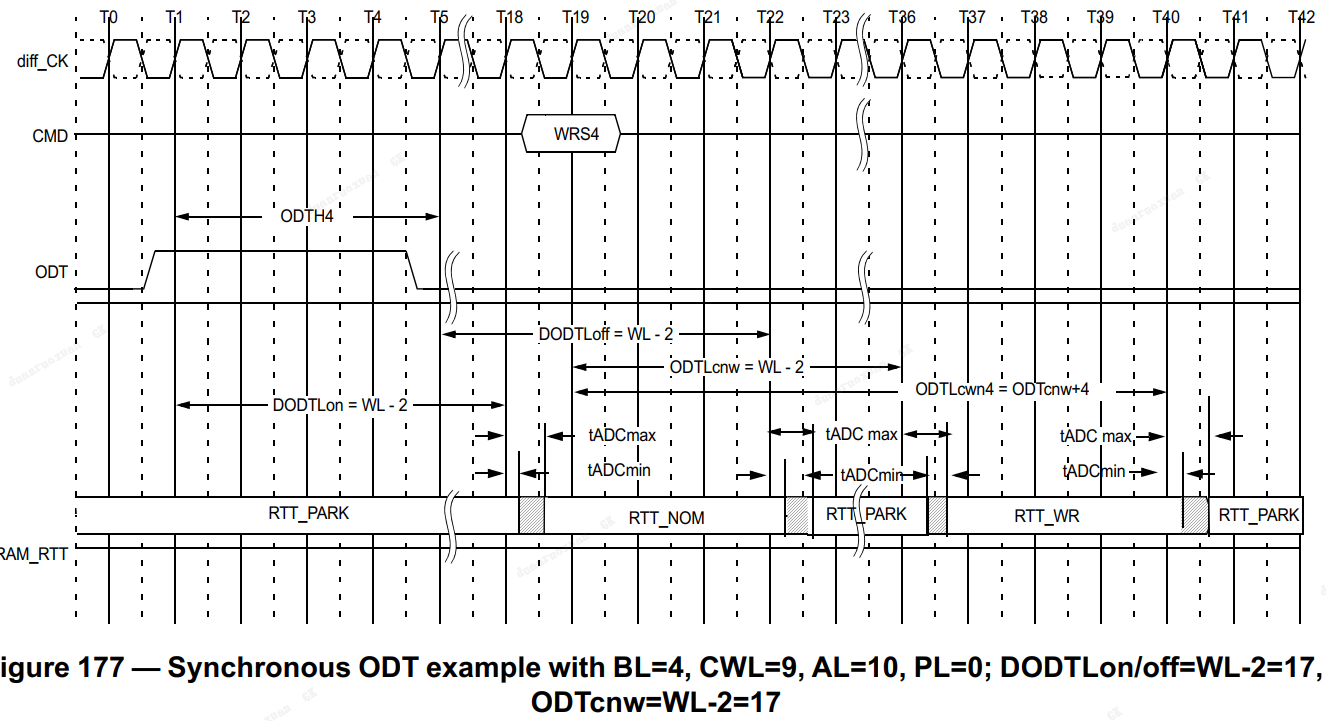

在同步ODT模式中,当CK上升沿采样到ODT pin为高时,经DODTLon个CK周期后,终端电阻值变为RTT_NOM,当在CK上升沿采样ODT pin为低时,经DODTLoff个CK周期后,终端电阻阻值不再为RTT_NOM。ODT开启和关闭的延迟与Write Latency有关,WL = CL+AL+PL,DODTLon=WL-2,DODTLoff=WL-2。前导时钟为2tCK时,DODTLon=WL-3,DODTLoff=WL-3。

5.2.2 时序参数

在同步ODT模式下,有如下时序参数:DODTLon, DODTLoff, RODTLoff, RODTLon4, RODTLon8, tADC,min,max。其中tADCmin、tADCmax为RTT从某个值切换到另一个值所需要的时间。时间参数tADC在同步ODT模式和电阻Disable模式下都适用。

当ODT pin拉高,必须保持ODTH4个CK周期(突发长度为4),或者必须保持ODTH8个CK周期(突发长度为8)。另外,根据MRS设置的不同,当开启CRC或前导为2tCK时,ODTH的值也会发生变化。

图176展示了同步ODT的时序。可见,ODT pin在CK下降沿进行改变,不到一个周期就能改变完成。tADCmax/min时间小于一个CK。这里有个问题,当ODT在下降沿改变时,为何tADC在ODT下降沿之前就开始出现了?实际上,参见5.6节tADC的测量方式,其不是根据ODT pin的高低电平来测量的,而是根据DODTLon/DODTLoff的右边界来作为tADC的起点。

图177展示了带有WRS4命令的时序图。这里有个疑问,在ODT拉高4个周期的时候,并没有发送写命令,从而不会知道突发长度到底是多少。难道在T0时刻前已经规定了突发长度?按照后续发送的WRS4命令,看起来应该是在T0以前规定了突发长度。另外,WRS4命令的发送正好处于DODTLon结束后的下一个CK上升沿,非常巧合,非常特例。个人理解,WRS4也可以推迟几个CK周期再发送。

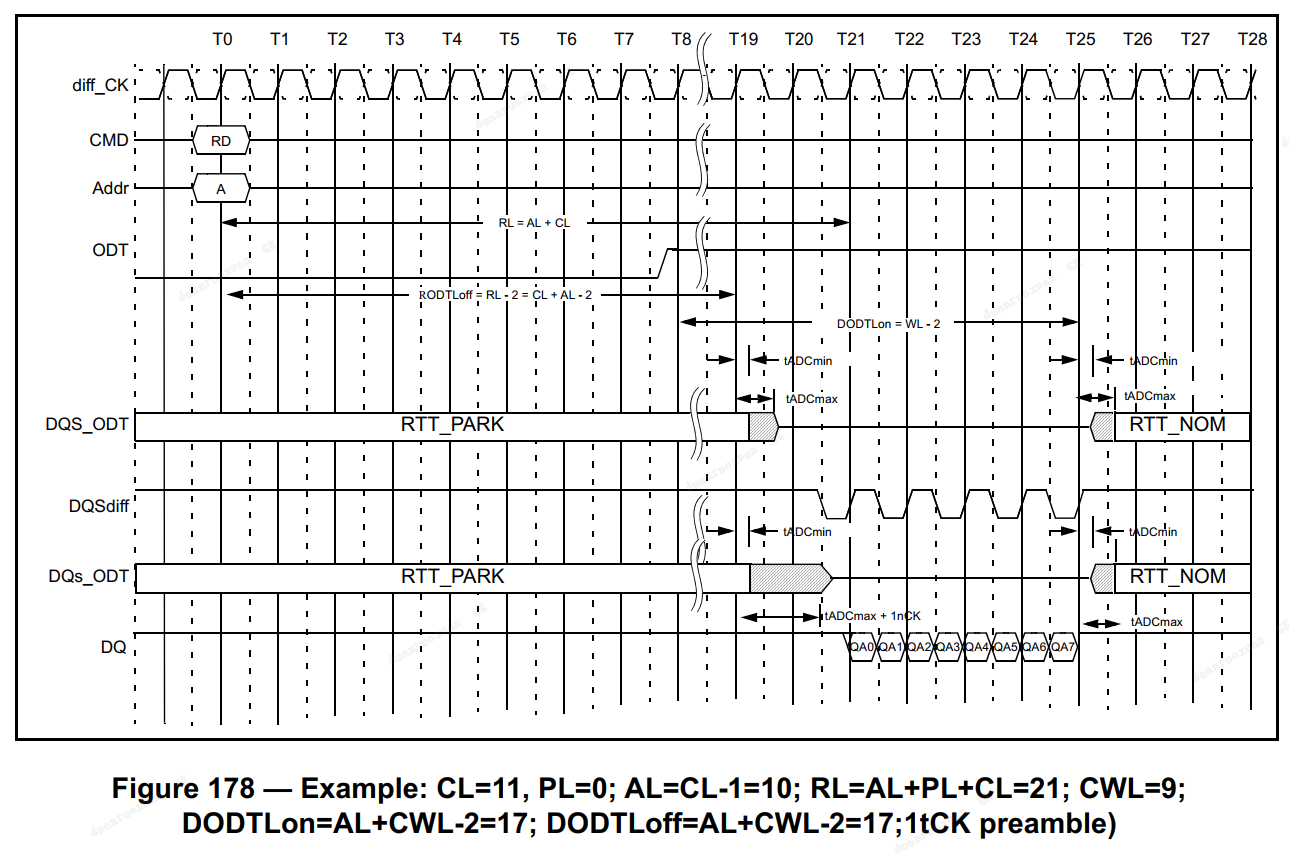

5.2.3 读期间的ODT

由于读操作需要DRAM返回数据给内存控制器,故需要驱动DQS信号和DQ信号,而DRAM不能在驱动信号的同时还挂载一个终端电阻(这就是为什么在数据返回时,本身DQS和DQ为高阻态,但是由于有数据返回,变成了有变化的数据信号)。在读后导结束前,RTT将不会回到RTT_NOM值,如图178的T25时所示。

在下图的阴影处,本质上为高阻态。时序参数tHZ对应tADC。

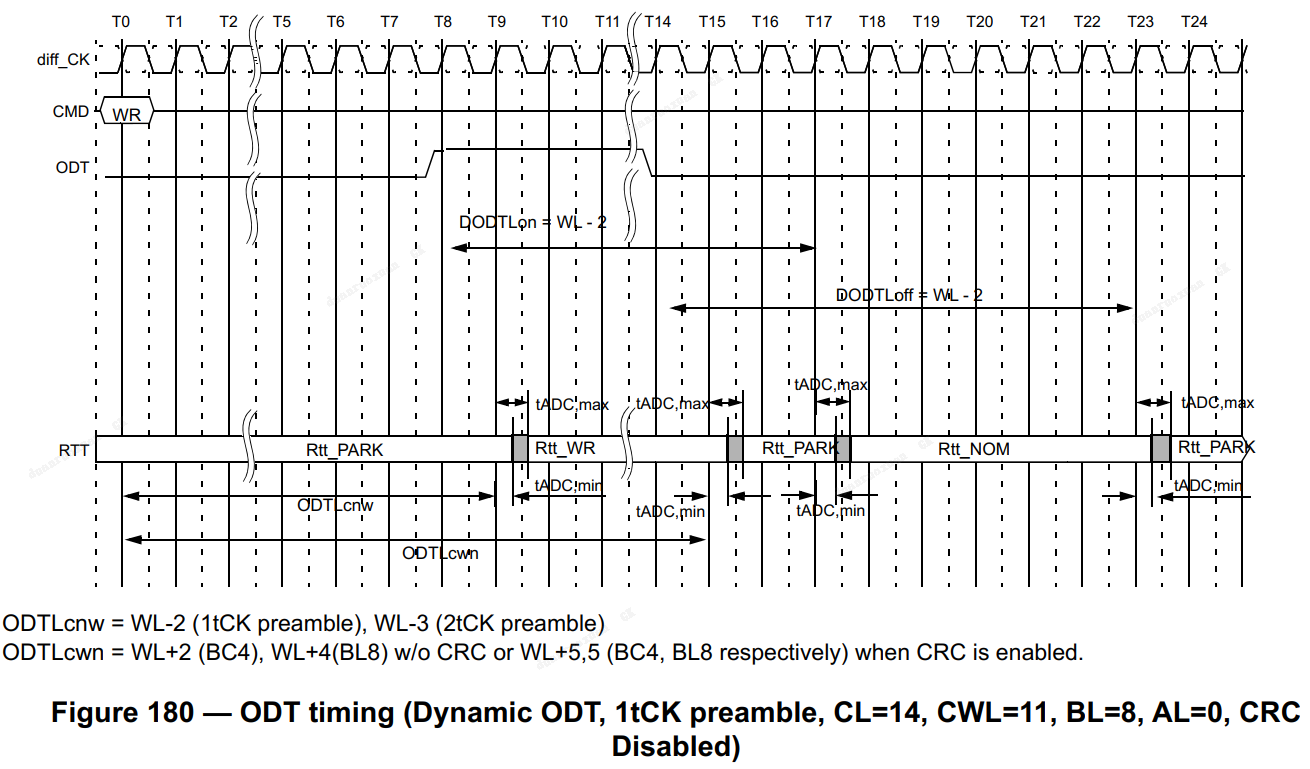

5.3 动态ODT

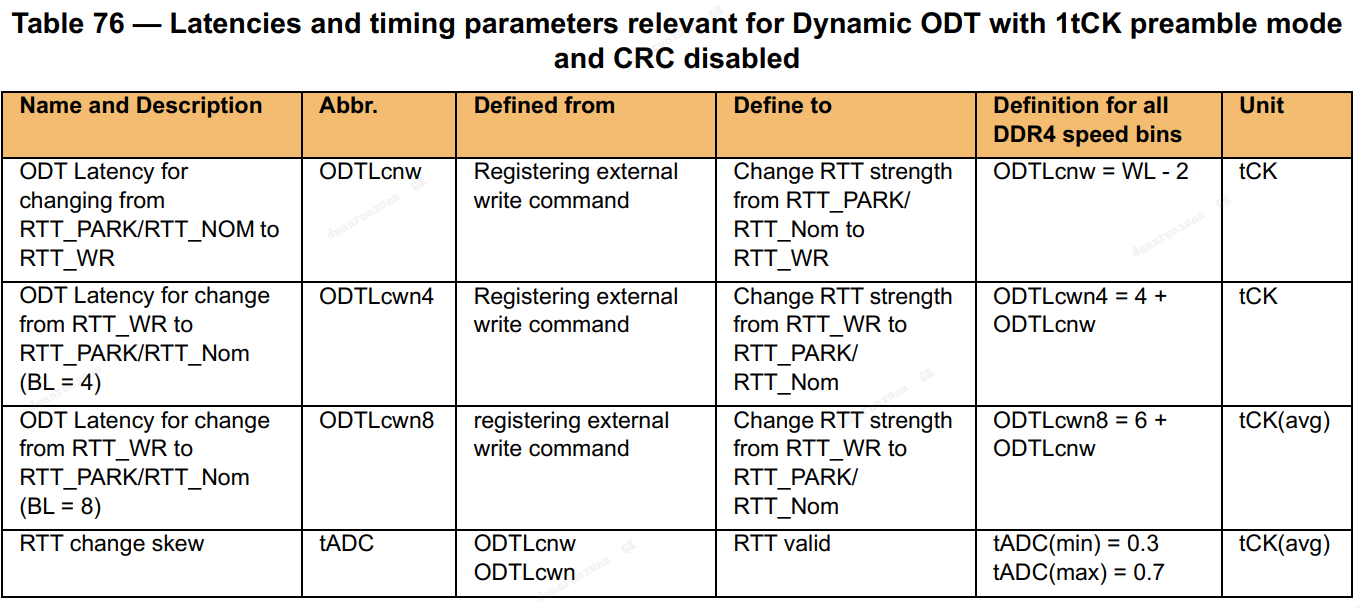

动态ODT即为不发送MRS命令即可改变RTT值。支持动态ODT功能描述如下:

5.3.1功能描述

将MR2的A9或A10其中一个设置为1,即可进入动态ODT模式。

- 动态ODT支持三种RTT值:RTT_NOM, RTT_PARK and RTT_WR,相比与同步ODT模式,少了一个电阻disable。

- 在没有命令发送的情况下,终端电阻如下:

终端电阻要么为RTT_NOM,要么为RTT_PARK。

RTT_NOM的开/关时序由ODT pin以及ODTLon/off的延迟决定;当ODT pin为低时,RTT = RTT_PARK。

- 当有写命令时,如果使能了动态ODT,则终端电阻如下:

在写命令发送后的ODTLcnw时序后,RTT = RTT_WR。

在写命令发送后的ODTLcwn8(突发长度为BL8(Fixed or OTF))或ODTLcwn4(突发长度为BL4(Fixed or OTF)),RTT不再等于RTT_WR。

当处于CRC或者2tCK前导模式下,ODTLcnw的时长应该增减1或2个CK周期。

表76展示了动态ODT模式下的时序参数和延迟时间,其中未使能CRC,且前导时钟为1tCK。

5.3.2动态ODT时序

5.4 异步ODT模式

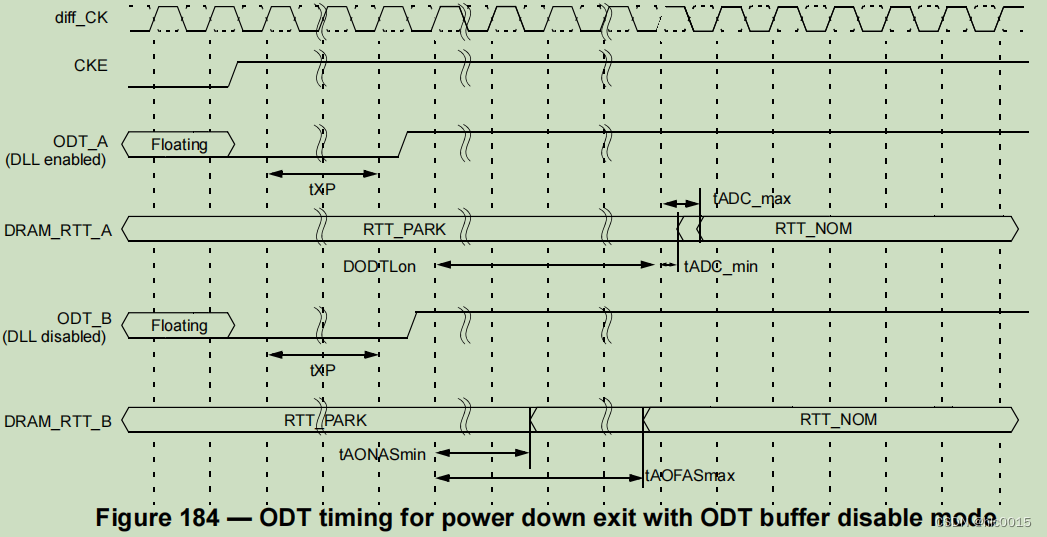

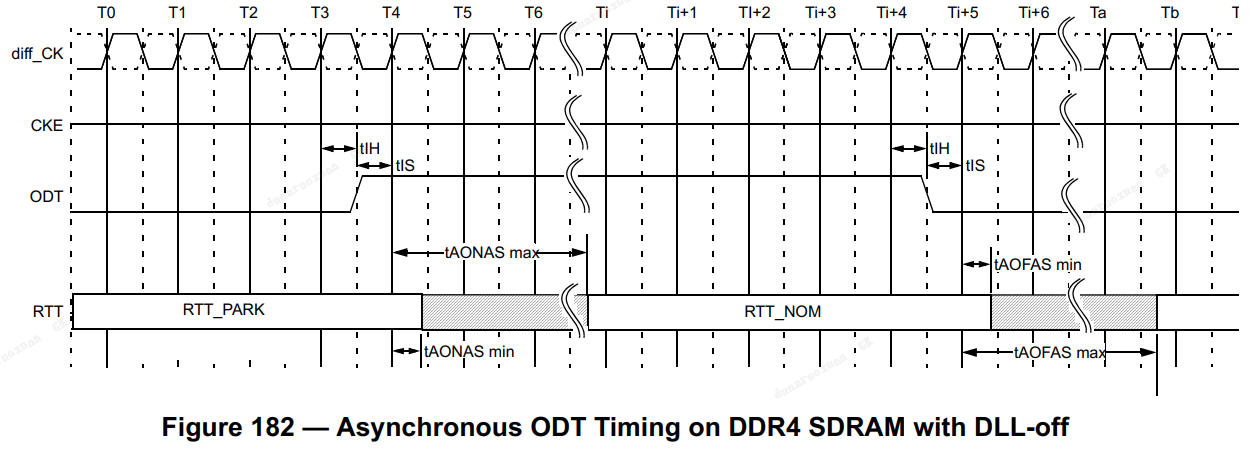

当DLL被disable时,也就是MR1的A0=0时(即DLL off时),ODT的模式为异步ODT模式。在异步ODT模式下,内部ODT命令不会受到AL延迟的影响,也不会受到外部ODT信号的影响(这句话存疑)。此模式下所用的时序参数为tAONAS,tAOFAS。

tAONSAS为开启RTT_NOM的时间。tAONASmin的右边界为终端电阻的阻值从RTT_PARK开始变换,tAONASmax的右边界为终端电阻变成了RTT_NOM,两者的左边界为CK信号上升沿采样到ODT pin脚信号为高的时刻。

与tAONSAS参数相对应的为tAOFAS。tAOFASmin的右边界为终端电阻阻值从RTT_NOM开始变换,ttAOFASmax的右边界为终端电阻变成了RTT_PARK,两者的左边界为CK信号上升沿采样到ODT pin脚信号为低的时刻。

图182为上述两段话的说明。

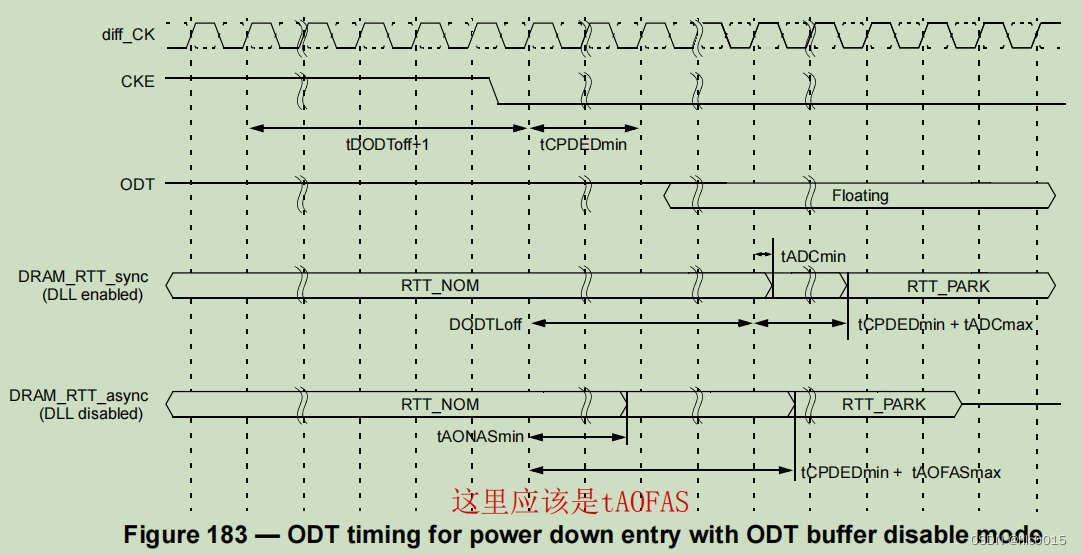

5.5 低功耗时disable ODT bufferr模式

在下电时,如果MR5的A5=1,则DRAM颗粒不会提供RTT_NOM终端电阻给所有的输入。当进入下电模式时,内存控制器必须持续控制ODT pin脚为高或者为低,即从在CK采样到CKE为低之前的tDDODToff - 1的时刻,到CK采样到CKE为低之后的tCPDEDmin,这两段时间内,ODT pin必须保持在某一稳定的电平。在此时序之后,ODT pin可以为Floating态。在CKE拉高时(以及tANPD)之前,终端电阻可以为RTT_NOM,也可以为RTT_PARK(虽然图183中CKE拉低时和拉低之前,RTT的值为RTT_NOM)。tANPD=WL-1,其右边界为PDE。

当退出Power down模式,ODT pin必须在CKE拉高之后的tXP时间后拉高。