01--Data Store Memory模块

数据存储模块一般是和数据写入还有数据访问一同搭配使用的

可以从帮助文档看到该模型如下的关键使用信息:

Data Store Memory 模块定义并初始化一个命名的共享数据存储,即一个内存区域,供指定相同数据存储名称的 Data Store Read 和 Data Store Write 模块使用。

-

如果 Data Store Memory 模块在顶层系统中,则模型中任意位置的 Data Store Read 和 Data Store Write 模块都可以访问该数据存储。

-

如果 Data Store Memory 模块在子系统中,则位于同一子系统或模型层次结构中该子系统下面的任何子系统中的 Data Store Read 和 Data Store Write 模块都可以访问该数据存储

-

Data Store Read 或 Data Store Write 模块不能访问位于包含 Model 模块的模型中或引用模型中的 Data Store Memory 模块。

-

不要在 For Each 子系统中包含 Data Store Memory 模块。

下面举例说明上述标红部分:

在最顶层且在同一层级,输出结果一致,数据可以访问

数据存储在最顶层,数据写入在内层,输出结果一致,数据可以访问

数据存储在内层,数据访问在外层报错,不可访问

这就是问什么你会发现在工程中,很多需要进行存储的变量他的数据存储模块都是在模型的最外层。

02--clock时钟模块

时钟模块有用于连续系统的clock模块,和用于离散系统的Digital Clock模块

Clock 模块在每个仿真时间步输出当前仿真时间。此模块对需要仿真时间的其他模块非常有用。在离散系统中需要当前时间时,请使用 Digital Clock 模块。

Digital Clock 模块仅以指定的采样间隔输出仿真时间。在其他时间,此模块保留输出的上一个值。要控制此模块的精度,请使用模块对话框中的 Sample time 参数。

时钟模块的采样时间是连续的但是按步长仿真显示时跟随求解器,而digital clock则在对话框直接设置,下例中求解器时间为0.1

更改digital clock采样时间后

03--Bitwise Operator位运算模块

Bitwise Operator 模块执行您为一个或多个操作数指定的按位运算。与 Logical Operator 模块的逻辑运算不同的是,按位运算将操作数视为位向量,而不是单个值。Bitwise Operator 模块不支持移位运算。对于移位运算,请使用 Shift Arithmetic 模块。

当去掉选项 Use Bit Mask时,需要有多个输出,输入值会先转化为二进制,然后按位进行运算,如下图为按位与

按位或

当将常数的数据类型有Uint8改为Uint16时,切换成逻辑非与时

当逻辑设置为异或时(当输入相同输出0,输入不同输出1为异或)

当勾选了Use bit mask时,只能有一个输入,对话框内有另外一个可以更改的输入进行逻辑运算

04--Shift Arithmetic移位模块

Shift Arithmetic 模块可以移动输入信号中的数位和/或二进制小数点。

-

当不移位时数据的二进制

-

当数据的二进制向左移2位时

-

当数据的二进制向右移2位时

-

也可以将移位放在外部接口

关于移位支持浮点数也支持定点数,更多详细内容参考Help文档

05--Extract Bits截取位模块

Extract Bits 模块允许您从输入信号的存储整数值中输出选择的连续位。使用 Bits to extract 参数定义选择输出位的方法。

-

选择

Upper half输出一半的输入位,其中包含最高有效位。 -

选择

Lower half输出一半的输入位,其中包含最低有效位。 -

选择

Range starting with most significant bit以输出一定数量的输入信号最高有效位。在 Number of bits 参数中指定要输出的最高有效位数。 -

选择

Range ending with least significant bit以输出一定数量的输入信号最低有效位。在 Number of bits 参数中指定要输出的最低有效位数。 -

选择

Range of bits以在 Bit indices 参数中指定要输出的输入信号的一系列连续位。您需要以[start end]格式指明范围,而输入位的索引将从 0(最低有效位)开始连续标记。

截取低8位

截取高8位

截取最高位的2位

截取最低位的3位

截取第4位到第10位,位的序号从0开始

06-- Detect检测的7个模块

1.Detect Increase模块

Detect Increase 模块确定输入信号是否严格大于上一个值。

-

当输入信号大于上一个值时,输出为 true(等于

1)。 -

当输入信号小于或等于上一个值时,输出为 false(等于

0)。

2.Detect Decrease 检测递减模块

The Detect Decrease block determines if an input is strictly less than its previous value.

3.Detect Change 检测不等模块

只要当前时刻值和上一时刻值不相等就置1

4.Detect Fall Negative 模块

当前时刻小于0且上一时刻不小于0

5.Detect Fall Nonpositive模块

当前时刻小于等于0且上一时刻不小于等于0

6. Detect Rise Nonnegative模块

当前时刻大于等于0且上一时刻不大于等于0

7. Detect Rise Positive模块

当前时刻大于0且上一时刻不大于0

07-- Bit Clear 和Bit Set模块

由最低位开始,把指定的位设置为0或者1

如下把最低为设置为0和1

也可以作用于向量(注意起始位都是0)

08--数学函数和多项式模块

数学函数模块:

多项式模块:

相当于 5*x^5+4*x^4+3*x^3+X^2+2*x+2,上式中x=2, 即结果为:5*32+4*16+3*8+4+4+2= 258

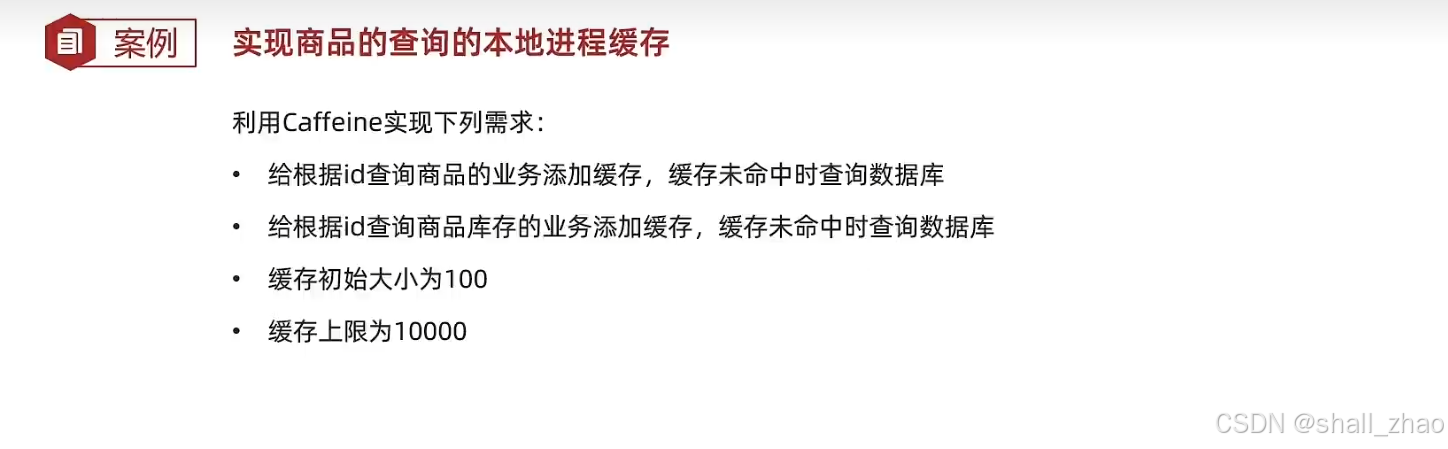

09--Interval Test Dynamic区间检测模块

如果在设定的区间内,则结果为逻辑真,否则为假,与饱和模块比较类似,饱和模块是输出输入值或者输出上下限值

以下2个模块的区别为一个在外部设置范围一个在内部设置范围

10--饱和模块 Saturation Dynamic

饱和模块是输出输入值或者输出上下限值

11--Dead Zone Dynamic死区模块

The Dead Zone Dynamic block generates a region of zero output based on dynamic input signals that specify the upper and lower limit. The block output depends on the input u, and the values of the input signals up and lo.

如果输入值在死区设定的范围内,那么输出值为0,如果不在则输出由输入值减去对应范围限制

12--Merge合并模块

Merge 模块可将多个输入合并为单个输出。输出值始终等于其驱动模块最近计算的输出。通过设置 Number of inputs 参数指定输入的数量。

请将 Merge 模块用于将在不同时间更新的输入信号交叉成一个合并信号,交叉值在合并信号中保留其各自的身份和时间。要将同时更新的信号合并成数组或矩阵信号,请使用 Concatenate 模块。

使用 Merge 模块时,请遵循以下原则:

-

始终使用条件执行子系统来驱动 Merge 模块。

-

确保在任何时间步都最多只有一个驱动条件执行子系统在执行中。

-

确保所有输入信号具有相同的采样时间。

如下,正弦波大于0部分显示1,小于0部分显示0

![[C#学习笔记]接口的特性与用法](https://i-blog.csdnimg.cn/direct/adca07bb3c3e497a960e7f14e92931b4.png)

![[数据集][目标检测]打电话检测数据集VOC+YOLO格式8985张1类别](https://i-blog.csdnimg.cn/direct/0aed1bf0357c4b2fb2eff6e53bad284b.png)