EDA技术

EDA指Electronic Design Automation,翻译为:电子设计自动化,最早发源于美国的影像技术,主要应用于集成电路设计、FPGA应用、IC设计制造、PCB设计上面。

而EDA技术就是指以计算机为工具,设计者在EDA软件平台上,用硬件描述语言Verilog HDL完成设计文件,然后由计算机自动完成逻辑编译、化简、分割、综合、优化、布局布线、仿真。

EDA涵盖了电子设计、仿真、验证、制造全过程的所有技术,诸如:系统设计与仿真,电路设计与仿真,印制电路板(PCB)设计与校验,集成电路(IC)版图设计、验证和测试,数字逻辑电路设计,模拟电路设计,数模混合设计,嵌入式系统设计,软硬件协同设计,芯片上系统(SoC)设计,可编程逻辑器件(PLD)和可编程系统芯片(SOPC)设计,专用集成电路(ASIC)和专用标准产品(ASSP)设计技术等。

EDA技术的出现极大提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

硬件描述语言HDL

HDL指硬件描述语言,即描述数字电路和系统的语言的统称。

例如,要编写FPGA的代码(即:描述FPGA电路结构)肯定得需要一种语言吧,那C/C++、Java、Python等一众软件语言可以吗?那肯定不行啊,软件语言无法描述出清楚的电路结构,也没有办法约定时钟、走线、端口等。简单一句话,它们没这个实力知道吧😎,所以这时候就需要专用的硬件描述语言HDL了。不过不像软件语言那样枝繁叶茂,经过近三十年的发展,只有Verilog HDL和VHDL二者最终脱颖而出,成为了公认的行业标准,两者逻辑相通。

假如要实现计数器的一个逻辑功能,可以通过编写Verilog语言,对计数器的功能进行描述,完成之后,使用Quarter软件对代码进行分析综合、布局布线等一系列操作,将生成的网表文件下载到FPGA开发板中。

那么在FPGA当中呢,就会实际生成一个硬件电路,其功能就是计数器的功能。

常见的HDL主要有以下4种:

| VHDL |

| Verilog HDL |

| System Verilog |

| System C |

其中VHDL和Verilog HDL在EDA设计中使用最多,也得到几乎所有的主流EDA工具的支持。而Syatem Verilog是Verilog的扩展与延伸。

简要介绍一下Verilog语言的发展历史:

1983年,由由GDA(GateWay Design Automation)公司的Phil Moorby首创,用作Verilog-XL仿真器的内部语言。

1989年,GDA公司被Cadence公司收购,Verilog HDL语言成为Cadence公司的私有财产。

1990年,Cadence公司决定公开Verilog HDL语言,于是成立了OVI(Open Verilog International)组织,负责促进Verilog HDL语言的发展。

2001年,IEEE发布了Verilog HDL 1364-2001标准。在这个标准中,加入了Verilog HDL-A标准,使Verilog有了模拟设计描述的能力。

- Verilog对VHDL的优势

相比于VHDL,Verilog有更广泛的设计群体,成熟的资源也远比VHDL丰富。并且Verilog是一种容易掌握的硬件编程语言(而VHDL需要Ada编程基础)。对于硬件语言学习,首选Verilog。

IP核简介

IP核,全称知识产权核(Intellectual Property core),在集成电路设计领域中扮演着重要角色。通俗地解释,IP核就是那些已经设计好、验证过,并可以重复使用的电路功能模块或设计模块。它们就像是构建积木一样,可以被设计师们用来快速搭建出复杂的集成电路系统,从而大大缩短设计周期,提高设计效率。

IP核主要分为3类:软IP(Soft IP Core)、固IP(Firm IP Core)和硬IP(Hard IP Core)。

- 软IP

软IP通常是用硬件描述语言(如VHDL或Verilog)编写的功能描述,它只定义了电路的行为和功能,而不涉及具体的电路实现细节(例如实现加法器功能,软核不在乎其内部是晶体管还是MOS管,设计者可自己选择)。这种形式的IP核具有高度的灵活性和可移植性,但需要在后续的设计过程中进行综合和验证。

- 想象一下,你是一位厨师,想要制作一道复杂的菜肴,比如法式炖鸡。在这道菜中,有许多关键的步骤和成分,比如腌制鸡肉、准备蔬菜、炖煮等。现在,我们来用烹饪的步骤来类比软IP核:

- 软IP核就像是一份详细的食谱。这份食谱用文字(就像硬件描述语言)详细描述了制作法式炖鸡的每一个步骤,包括需要哪些食材(就像电路中的元件)、食材的处理方式(就像元件的连接和配置)、以及烹饪的时间、温度等参数(就像电路的时序和性能要求)。但是,这份食谱并没有直接给你提供已经切好的蔬菜、腌制好的鸡肉或者加热好的锅具——它只是告诉你应该怎么做。

- 当你拿到这份食谱时,你需要自己准备食材、工具,并按照食谱上的指示一步步操作。这个过程中,你可能会根据自己的口味和经验对食谱进行一些调整(就像在设计过程中对软IP核进行一定程度的修改和优化)。

- 最终,当你按照食谱完成所有步骤后,你会得到一道美味的法式炖鸡。同样地,在集成电路设计中,当你使用软IP核并按照其描述完成电路设计后,你会得到一个具有特定功能的电路模块。

- 所以,软IP核就像是一份详细的食谱,它提供了实现某个功能所需的所有“配方”和“步骤”,但具体的“食材”和“烹饪过程”还需要设计者自己去准备和实现。这种方式使得设计过程更加灵活,可以根据不同的需求和条件进行调整和优化。

- 固IP

固IP在软IP的基础上,进一步完成了门电路级综合和时序仿真等设计环节,通常以门电路级网表的形式提供给用户。固IP比软IP更接近于物理实现,但仍然保留了一定的灵活性。

- 固IP就像是半成品菜肴。想象一下,你走进一家餐馆的后厨,发现已经有人为你准备好了法式炖鸡的大部分工作:鸡肉已经腌制好,蔬菜也已经切好并部分烹饪过,甚至连炖锅都已经加热到了适宜的温度,并加入了适量的汤底。你只需要将这些半成品组合起来,继续完成最后的炖煮过程,并可能根据个人口味进行微调,比如添加一些香料或调整火候。

- 固IP核在集成电路设计中,就像是部分预制的电路模块。这些模块已经完成了较为关键的设计,比如核心的逻辑功能已经实现,但可能还留有一些接口或参数供用户根据自己的需求进行配置或调整。这样,用户既可以利用已经完成的设计工作,又可以保持一定的设计灵活性和自定义能力。

- 硬IP

硬IP则提供了设计的最终阶段产品——掩膜(Mask),它经过了完全的布局布线,并已经针对特定工艺或购买商进行了优化。硬IP具有极高的可预见性和可靠性,但相对缺乏灵活性。

- 硬IP就像是即食菜肴或者已经做好的成品菜肴。在烹饪的类比中,这就像是走进一家餐馆,直接点了一份法式炖鸡,餐馆的服务员直接把已经烹饪好的、热气腾腾的菜肴端到你的面前。你不需要再去做任何准备或加工,只需要享受这道菜肴的美味即可。

- 在集成电路设计中,硬IP核就是经过完整设计和验证的、可以直接用于生产的电路模块。这些模块通常已经针对特定的工艺或性能要求进行了优化,用户只需要将它们集成到自己的设计中,并按照既定的接口进行连接即可。硬IP核提供了极高的可靠性和可预测性,但相对而言,设计灵活性较低,不太容易进行大规模的修改或定制。

Verilog模型类型

Verilog的5种模型类型分别代表了电路设计的不同抽象级别,它们分别是系统级(System Level)、算法级(Algorithmic Level)、RTL级(Register Transfer Level)、门级(Gate Level)和开关级(Switch Level)。下面是对这五种模型类型的详细介绍:

- 1. 系统级(System Level)

描述内容:系统级模型使用语言提供的高级结构来实现待设计模块的外部性能。它主要关注系统的整体功能和行为,而不深入到底层的硬件实现细节。

- 系统级模型就像城市规划师制定城市的发展蓝图。他们考虑的是整个城市的布局、交通网络、公共服务设施等宏观层面的设计,而不深入到具体的建筑结构和材料选择。他们关注的是整个系统的功能性和协调性。

- 2. 算法级(Algorithmic Level)

描述内容:算法级模型利用语言提供的高级结构来实现算法的运行。它关注于算法的逻辑和实现方式,而不直接涉及硬件电路的具体实现。

- 算法级模型类似于烹饪食谱。食谱详细说明了制作一道菜所需的步骤和原材料,但它不关注你使用什么样的锅碗瓢盆,也不关心你是用电炉还是煤气灶。它专注于算法的逻辑和流程,即如何达到最终的结果。

- 3. RTL级(Register Transfer Level)

描述内容:RTL级模型描述数据在寄存器之间的流动和如何处理这些数据,以及控制这些数据流动的机制。它是硬件电路设计与行为描述之间的桥梁,与逻辑电路有明确的对应关系。

- RTL级模型就像是组装家具的过程。在这个阶段,你已经有了各个部件(如木板、螺丝、连接件等),并且知道它们是如何通过说明书上的步骤组装在一起的。这类似于在RTL级,你知道了各个寄存器之间的数据流和控制信号,以及如何通过这些寄存器来实现电路的功能。

- 4. 门级(Gate Level)

描述内容:门级模型直接描述逻辑门以及逻辑门之间的连接关系。它关注于电路的基本构建块(如与门、或门、非门等)及其组合方式,与逻辑电路有明确的连接关系。

- 门级模型就像是用积木搭建一个复杂的结构。在这个阶段,你关注的是积木(即逻辑门)之间的连接方式和布局,以构建出你想要的形状和功能。每个积木(逻辑门)都有它特定的功能(如与、或、非等),你需要通过合理的组合来实现你的设计目标。

- 5. 开关级(Switch Level)

描述内容:开关级模型描述器件中三极管和存储节点以及它们之间的连接关系。它深入到电路的物理层面,关注于晶体管级别的电路行为。

- 开关级模型则更像是深入到电子设备内部进行修理。在这个阶段,你需要了解每个元件(如晶体管、电阻、电容等)的物理特性和它们之间的连接方式。你可能需要替换损坏的元件,或者调整电路的连接方式以修复故障。这类似于在开关级,你需要对电路的物理层面有深入的理解,以便进行精确的修复和优化。

HDL综合

HDL综合(Hardware Description Language Synthesis)是电子设计自动化(EDA)中的一个关键步骤,它涉及将硬件描述语言(如Verilog或VHDL)编写的较高层次设计描述自动转化为较低层次的电路描述或网表。(在这个过程中,综合工具会根据设计约束和优化目标,将抽象的设计转化为可实现的硬件电路。)

层次化设计

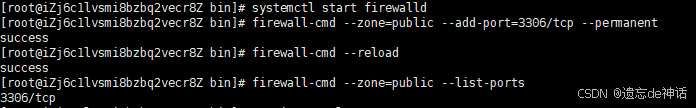

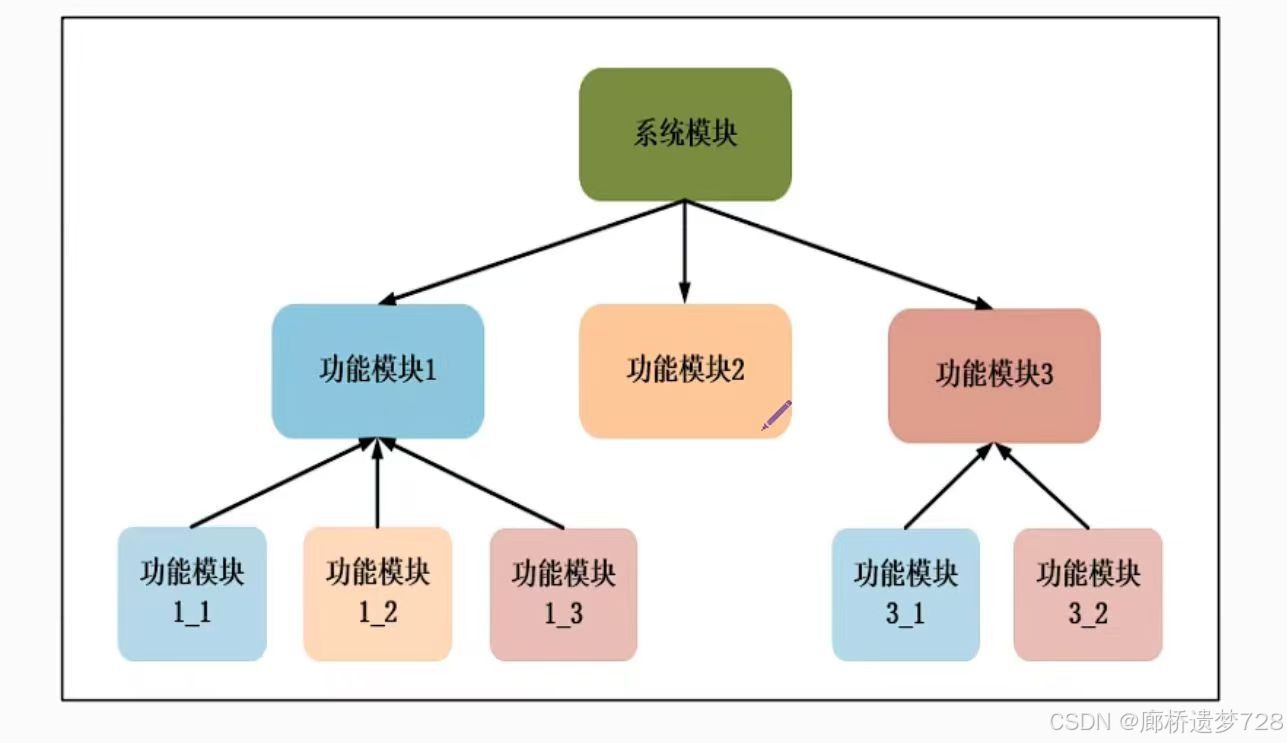

数字电路中根据模块层次不同有两种基本的结构设计方法:自底向上(Bottom-Up)和自顶向下(Top-Down)的设计方法。

- 自底向上

是一种传统的设计方法,对设计进行逐次划分的过程是从存在的基本单元出发的,由基本单元构建高层单元,依次向上,直至构建系统。

- 自顶向下

从系统级开始,把系统分为基本单元,然后再把每个单元划分为下一层次的基本单元,一直这样做下去,直到直接可以用EDA元件库的元件为止。

- 混合使用

在典型的设计方法中,两种方法是混合使用的。

![[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-37 LVDS信号环路测试](https://i-blog.csdnimg.cn/direct/2a06a5aebda54dd1be28ffb6f89d747e.png)