问题描述

设备: xcvm1102-sfva784-2HP-iS

问题:尽管使用 GCIO 引脚作为时钟,但布局器返回 I/O 时钟错误

错误:

<span style="background-color:#f3f3f3"><span style="color:#333333"><code>ERROR: [Place 30-675] Sub-optimal placement for a global clock-capable IO pin and BUFG pair.If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_in_IBUF] >

Clock Rule: rule_gclkio_bufg

Status: FAILED

Rule Description: An IOB driving a BUFG must use a GCIO in the same clock region as the BUFG

clk_in_IBUF_inst (IBUF.O) is locked to IOB_X13Y8

bufg_in (BUFGCE.I) is provisionally placed by clockplacer on BUFGCE_X1Y23

The above error could possibly be related to other connected instances. Following is a list of

all the related clock rules and their respective instances.

Clock Rule: rule_mmcm_bufg

Status: PASS

Rule Description: A MMCM driving a BUFG must be placed in the same clock region of the device as the

BUFG

MMCME5_inst (MMCME5.CLKOUT0) is provisionally placed by clockplacer on MMCM_X0Y0

bufg_out (BUFGCE.I) is provisionally placed by clockplacer on BUFGCE_X0Y0

Clock Rule: rule_bufgce_bufg_conflict

Status: PASS

Rule Description: Only one of the 2 available sites (BUFGCE or BUFGCE_DIV/BUFGCTRL) in a pair can be

used at the same time

bufg_in (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_X1Y23

Clock Rule: rule_io_bufg_mmcm_1load

Status: FAIL

Rule Description: A BUFGCE with I/O driver driving a single MMCM must both be in the same clock region

if CLOCK_DEDICATED_ROUTE=BACKBONE is NOT set

bufg_in (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_X1Y23

MMCME5_inst (MMCME5.CLKIN1) is provisionally placed by clockplacer on MMCM_X0Y0

ERROR: The above is also an illegal clock rule

Workaround: < set_property CLOCK_DEDICATED_ROUTE ANY_CMT_REGION [get_nets clk_in_temp] >

Clock Rule: rule_bufgce_bufg_conflict

Status: PASS

Rule Description: Only one of the 2 available sites (BUFGCE or BUFGCE_DIV/BUFGCTRL) in a pair can be

used at the same time

bufg_out (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_X0Y0

Resolution: A dedicated routing path between the two can be used if: (a) The global clock-capable IO (GCIO) is placed on a GCIO capable site (b) The BUFG is placed in the same bank of the device as the GCIO pin. Both the above conditions must be met at the same time, else it may lead to longer and less predictable clock insertion delays.

ERROR: [Place 30-1971] Sub-optimal placement for a global clock-capable IO pin-BUFGCE-MMCM pair.

Resolution: A dedicated routing path between the pairs can be used if: (a) The global clock-capable IO (GCIO) is placed on a GCIO capable site (b) The BUFGCE and MMCM is placed in the same clock region as the GCIO pin. If the IOB is driving BUFGCE and driving multiple MMCMs, all MMCMs must be placed in the same clock region. Both the above conditions must be met at the same time, else it may lead to longer and less predictable clock insertion delays. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE ANY_CMT_REGION [get_nets clk_in_temp] >

Clock Rule: rule_io_bufg_mmcm_1load

Status: FAILED

Rule Description: A BUFGCE with I/O driver driving a single MMCM must both be in the same clock region if CLOCK_DEDICATED_ROUTE=BACKBONE is NOT set

bufg_in (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_HDIO_X0Y0

MMCME5_inst (MMCME5.CLKIN1) is provisionally placed by clockplacer on MMCM_X0Y0

The above error could possibly be related to other connected instances. Following is a list of

all the related clock rules and their respective instances.

Clock Rule: rule_mmcm_bufg

Status: PASS

Rule Description: A MMCM driving a BUFG must be placed in the same clock region of the device as the

BUFG

MMCME5_inst (MMCME5.CLKOUT0) is provisionally placed by clockplacer on MMCM_X0Y0

bufg_out (BUFGCE.I) is provisionally placed by clockplacer on BUFGCE_X0Y23

Clock Rule: rule_bufgce_bufg_conflict

Status: PASS

Rule Description: Only one of the 2 available sites (BUFGCE or BUFGCE_DIV/BUFGCTRL) in a pair can be

used at the same time

bufg_in (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_HDIO_X0Y0

Clock Rule: rule_bufgce_bufg_conflict

Status: PASS

Rule Description: Only one of the 2 available sites (BUFGCE or BUFGCE_DIV/BUFGCTRL) in a pair can be

used at the same time

bufg_out (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_X0Y23

Clock Rule: rule_gclkio_bufg

Status: PASS

Rule Description: An IOB driving a BUFG must use a GCIO in the same clock region as the BUFG

clk_in_IBUF_inst (IBUF.O) is locked to IOB_X13Y8

bufg_in (BUFGCE.I) is provisionally placed by clockplacer on BUFGCE_HDIO_X0Y0</code></span></span>在这个简单的设计示例中,我们有两个错误,提示两个 CLOCK_DEDICATED_ROUTE 解析指向两个网络。

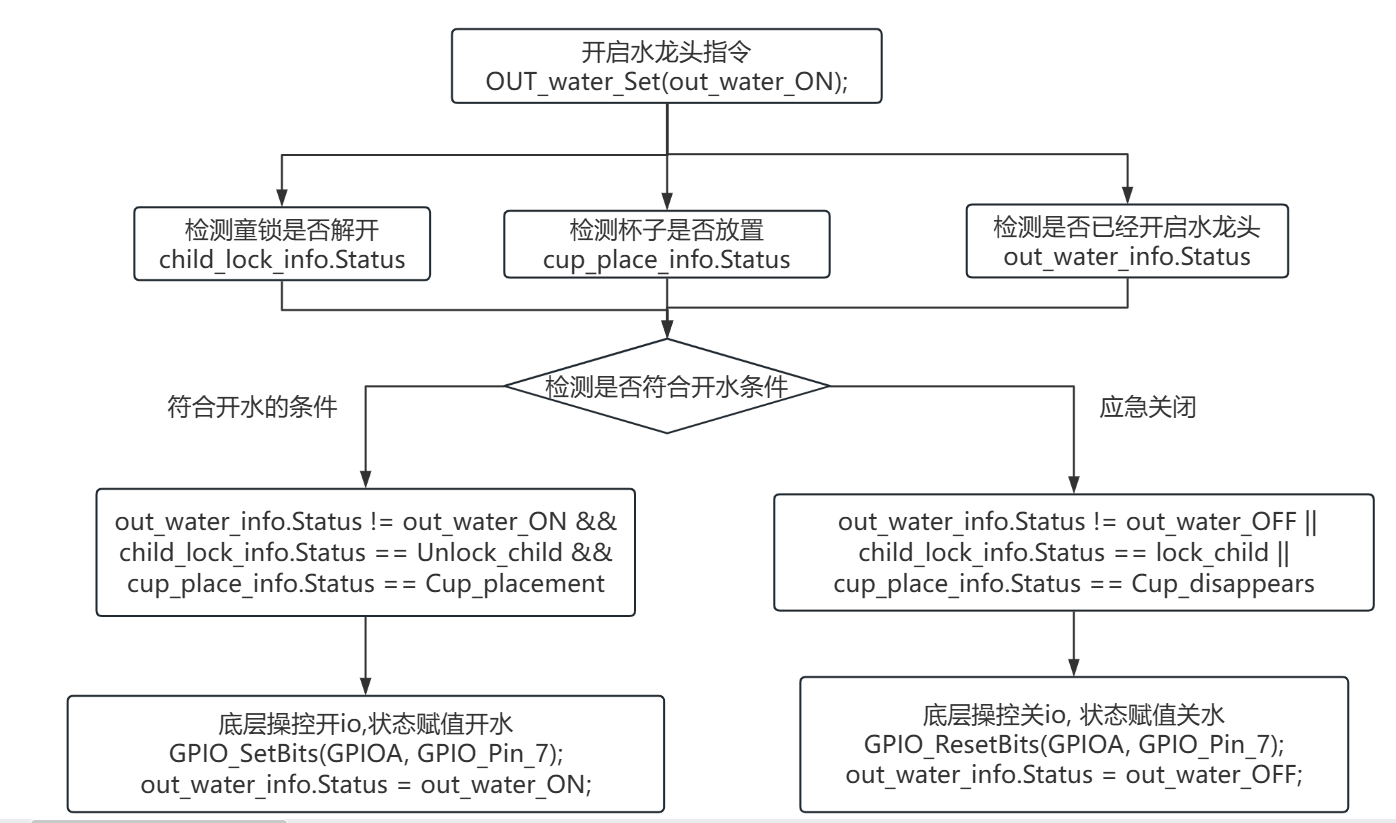

使用错误中提到的网络名称并生成原理图,我们会看到以下时钟结构:。

- 输入缓冲器 → BUFG

- BUFG → MMCM

输入时钟端口使用来自 HDIO 组的 Global Clock Capable Package 引脚 D11。尽管如此,布局器仍会出错,并出现上述 I/O Clock Placer 错误。让我们使用Vivado 实施 - 解决 I/O Clock Placer 错误

中概述的方法调试此问题。

这个时钟结构有两个部分

- 段 1 = IBUF → BUFG

- 段 2 = BUFG → MMCM

通过打开 post opt DCP 并运行place_ports,我们将得到这个错误。

标记输入端口、BUFG 和 MMCM 将突出显示这些单元的临时位置。

根据规则 1,布局器应将输入端口 (粉色)、BUFG (黄色) 和 MMCM (绿色) 放置在同一个时钟区域 X0Y2 中。

让我们检查设备中可用的资源。

由于涉及的组件是 BUFG 和 MMCM,我们在设备中得到了 MMCM (橙色) 和 BUFG (蓝色)。

命令:

<span style="background-color:#f3f3f3"><span style="color:#333333"><code>show_objects -name find_1 [get_sites -filter { SITE_TYPE == "MMCM" } ]

show_objects -name BUFGs [get_sites BUFG*]</code></span></span>使用此信息,很明显,在同一个 CLOCK_REGION X0Y2 中有可用的 BUFG,但没有 MMCM。因此,在没有任何 CLOCK_DEDICATED_ROUTE 约束的情况下,布局器根据其可行性放置了段 1 和 2。

我们可以使用 CLOCK_REGION 将 BUFG 约束到 X0Y2,但是布局器仍然会在段 2 上出错,即 BUFG→MMCM

<span style="background-color:#f3f3f3"><span style="color:#333333"><code>set_property CLOCK_REGION X0Y2 [get_cells bufg_in]</code></span></span>新错误:

<span style="background-color:#f3f3f3"><span style="color:#333333"><code>ERROR: [Place 30-1971] Sub-optimal placement for a global clock-capable IO pin-BUFGCE-MMCM pair.

Resolution: A dedicated routing path between the pairs can be used if: (a) The global clock-capable IO (GCIO) is placed on a GCIO capable site (b) The BUFGCE and MMCM is placed in the same clock region as the GCIO pin. If the IOB is driving BUFGCE and driving multiple MMCMs, all MMCMs must be placed in the same clock region. Both the above conditions must be met at the same time, else it may lead to longer and less predictable clock insertion delays. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE ANY_CMT_REGION [get_nets clk_in_temp] >

Clock Rule: rule_io_bufg_mmcm_1load

Status: FAILED

Rule Description: A BUFGCE with I/O driver driving a single MMCM must both be in the same clock region if CLOCK_DEDICATED_ROUTE=BACKBONE is NOT set

bufg_in (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_HDIO_X0Y0

MMCME5_inst (MMCME5.CLKIN1) is provisionally placed by clockplacer on MMCM_X0Y0

The above error could possibly be related to other connected instances. Following is a list of

all the related clock rules and their respective instances.

Clock Rule: rule_mmcm_bufg

Status: PASS

Rule Description: A MMCM driving a BUFG must be placed in the same clock region of the device as the

BUFG

MMCME5_inst (MMCME5.CLKOUT0) is provisionally placed by clockplacer on MMCM_X0Y0

bufg_out (BUFGCE.I) is provisionally placed by clockplacer on BUFGCE_X0Y23

Clock Rule: rule_bufg_clockregion_prop

Status: PASS

Rule Description: A global clock source buffer with CLOCK_REGION property should get placed in the

clock region specified by the property

bufg_in (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_HDIO_X0Y0

Clock Rule: rule_bufgce_bufg_conflict

Status: PASS

Rule Description: Only one of the 2 available sites (BUFGCE or BUFGCE_DIV/BUFGCTRL) in a pair can be

used at the same time

bufg_in (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_HDIO_X0Y0

Clock Rule: rule_bufgce_bufg_conflict

Status: PASS

Rule Description: Only one of the 2 available sites (BUFGCE or BUFGCE_DIV/BUFGCTRL) in a pair can be

used at the same time

bufg_out (BUFGCE.O) is provisionally placed by clockplacer on BUFGCE_X0Y23

Clock Rule: rule_gclkio_bufg

Status: PASS

Rule Description: An IOB driving a BUFG must use a GCIO in the same clock region as the BUFG

clk_in_IBUF_inst (IBUF.O) is locked to IOB_X13Y8

bufg_in (BUFGCE.I) is provisionally placed by clockplacer on BUFGCE_HDIO_X0Y0</code></span></span>因此,除了将 CLOCK_DEDICATED_ROUTE 设置为 ANY_CMT_REGION 之外,没有其他方法可以放置此时钟结构。

这是因为 CLOCK_REGION X0Y2 中没有适用于段 2 的 MMCM。

<span style="background-color:#f3f3f3"><span style="color:#333333"><code>set_property CLOCK_DEDICATED_ROUTE ANY_CMT_REGION [get_nets clk_in_temp]</code></span></span>在下一次运行中,我们在设计中对段 1 有 CLOCK_REGION 约束,对段 2 有 CLOCK_DEDICATED_ROUTE ANY_CMT_REGION 约束,布局器会按预期放置结构。

因此,结论是,在某些情况下使用 CLOCK_DEDICATED_ROUTE 是不可避免的,但始终建议用户了解使用该过程得出的约束时的影响。

这里还有另一个问题需要考虑;如果时钟来自使用 MMCM 的角落时钟区域 (绿色) 的时钟功能输入,会怎么样?

在这种情况下,布局器将对 MMCM 站点 (绿色) 产生冲突,不知道是将现有 MMCM 放置在那里还是放置新的 MMCM。

始终建议在现有 MMCM 上使用 LOC 约束来指导布局器并考虑设计中的其他时钟。

附上本文所用到的简单例子,以供分析。

![[LeetCode]根据决策树设计代码解决dfs](https://i-blog.csdnimg.cn/direct/33ee3951597a4a588516dd23a21c239a.png)