- AD961同步信号SYNC无法保持高逻辑电

- 现象

- 配置ADF4351时钟芯片使其产生频率为1.6GHz的时钟为AD9161提供工作时钟,JESD的线速率配置为8Gbps,并配置AD9161的寄存器使其工作在2x内插模式以实现IQ信号的模数转换模式。同时根据AD9161芯片手册对ADF4351提供的1.6GHz进行分频,具体计算方式如下,DA_freq为DA的工作频率1.6GHz。

-

数据速率DataRate = DACRate/InterpolationFactor;线速率LaneRate = DateRate*20*M/L;LFMC=LaneRate/10/F/K;Tx_sysref=LFMC/R;R=1,2,3…;DAC_refclk=tx_sysref;JESD_sysref=LaneRate/40。

将工程编译后得到bit文件下载至板卡中,ILA显示AD9161同步信号SYNC无法保持高逻辑电平,即lanes上的数据无法同步。图1是AD9161同步信号高低电平跳变的ila截图,图2是AD9161寄存器0x281的返回值,根据芯片手册得知该返回值的最低位应为1,截图结其

-

图1 AD9161芯片同步异常

图1 AD9161芯片同步异常  图2 AD9161芯片寄存器0x281返回值

图2 AD9161芯片寄存器0x281返回值

-

解决措施

-

当需要使用DAC内部内插模式实现IQ复信号的输出时,数据速率DataRate计算公式中的InterpolationFactor应代入2,否则计算出来的线速率将无法满足AD9161芯片手册中的时钟要求。

-

根据AD9161芯片手册提供的资料,定位问题为线速率与DAC工作频率不适配导致,具体可参考公式1。修改线速率为4Gbps后解决了JESD SYNC信号无法保持为高逻辑电平的问题。

-

排查AD9161寄存器的配置参数,未发现问题;

-

检查AD9508时钟管理芯片的分频结果,未发现问题;

-

检查ADF4351输出时钟的频率,未发现问题;

-

当需要使用DAC内部内插模式实现IQ复信号的输出时,数据速率DataRate计算公式中的InterpolationFactor应代入2,否则计算出来的线速率将无法满足AD9161芯片手册中的时钟要求。

-

- 现象

- 频谱结果出现大量峰值

- 现象

- 使用FPGA的16路DDS产生余弦信号,并将该信号送至JESD的数据接口最终被AD9161输出,然而使用射频线连接AD9161的模拟输出接口与频谱仪输入接口时,后者的频谱分析界面上出现了大量峰值,如图3。

-

解决措施

- 根据AD9161芯片手册核实未使用其内部NCO功能,因此排除该问题是由AD9161寄存器配置不合理导致;

-

当未使用AD9161内部NCO功能时,若其模拟输出信号的结果出现大量峰值,一般是由于数据拼接失误导致。

- 检查FPGA的16路DDS信号生成结果,在ILA中抓取送入至JESD数据接口的数据,并使用matlab进行信号分析,结果表明DDS的信号生成无误;

- 最终将问题定位在数据拼接环节,结合JESD协议与AD9161芯片手册介绍的数据格式,确定该问题是由数据拼接失误导致,修改此处代码后AD9161输出的模拟信号结果正常。

-

当未使用AD9161内部NCO功能时,若其模拟输出信号的结果出现大量峰值,一般是由于数据拼接失误导致。

- 现象

AD9161调试问题

news2026/3/13 23:16:29

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/2076221.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

NoSql数据库 Redis集群详解

目录

一、NoSql数据库简介

1.1 数据库主要分为两大类:关系型数据库与 NoSQL 数据库 1.2 为什么还要用 NoSQL 数据库呢? 1.3 RDBMS和NOSQL的特点及优缺点: 二 Remote Dictionary Server 简介(redis) 2.1 什么是redis …

如何使用ssm实现物资进销存jsp

TOC

ssm263物资进销存jsp

绪论

1.1 研究背景

当前社会各行业领域竞争压力非常大,随着当前时代的信息化,科学化发展,让社会各行业领域都争相使用新的信息技术,对行业内的各种相关数据进行科学化,规范化管理。这样的…

JavaScript学习文档(4):循环结构、初识数组、数组案例、操作数组

目录

一、循环结构

1、for语句

2、for循环案例

3、for循环嵌套及案例

4、while语句

5、continue关键字

6、break关键字

二、初识数组

1、什么是数组

2、为什么要数组

3、数组的基本使用

三、数组案例

1、数组求和及平均值

2、数组求最大值和最小值

四、操作数组…

做集运初期到底要不要上系统?

在集运业务的起步阶段,很多老板都会有这样的疑问:“我的包裹量还不多,真的需要投入资金和时间来上系统吗?”这个问题听起来合理,但实际上却忽视了业务发展中更为重要的几个方面。 1.用户体验:服务的核心

首…

NVIDIA Jetson AGX Orin源码编译安装CV-CUDA

目录

1 下载源码并配置

2 编译安装CV-CUDA

2.1 安装相应依赖包

2.2 升级gcc到gcc-11

2.3 build

2.4 升级cmake

2.5 再次build

2.5.1 报错 /usr/include/c/11/bits/std_function.h:435:145: error: parameter packs not expanded with ‘...’:

3 直接使用安装包

参考…

力扣: 两两交换链表中的节点

文章目录 需求代码代码解释结尾 需求

给你一个链表,两两交换其中相邻的节点,并返回交换后链表的头节点。你必须在不修改节点内部的值的情况下完成本题(即,只能进行节点交换)。

示例 1: 输入:…

jmeter性能测试之CSV 数据文件设置

文章目录 业务场景使用步骤步骤1:准备数据步骤二: 编写csv文件步骤三:添加CSV 数据文件设置步骤四:定义接口,选择文件上传,文件名称通过“浏览”添加即可 业务场景 有一个文件上传的接口,希望每个线程上传不同的文件(比…

FOFA搜索引擎的语法

FOFA 是一款网络空间搜索引擎,允许用户通过自定义查询语法来检索全球范围内的互联网资产。FOFA 提供了丰富的语法,可以帮助用户筛选目标。以下是 FOFA 语法的基本介绍:

1. 基本语法格式

FOFA 的查询语句遵循以下格式:

字段&quo…

前端手写源码系列(二)——手写call、apply、bind

手写源码系列目录 一、作用二、手写call方法三、手写apply方法四、手写bind方法五、三者区别applycallbind小结 一、作用

call、apply、bind作用是改变函数执行时的上下文,简而言之就是改变函数运行时的this指向

那么什么情况下需要改变this的指向呢?下…

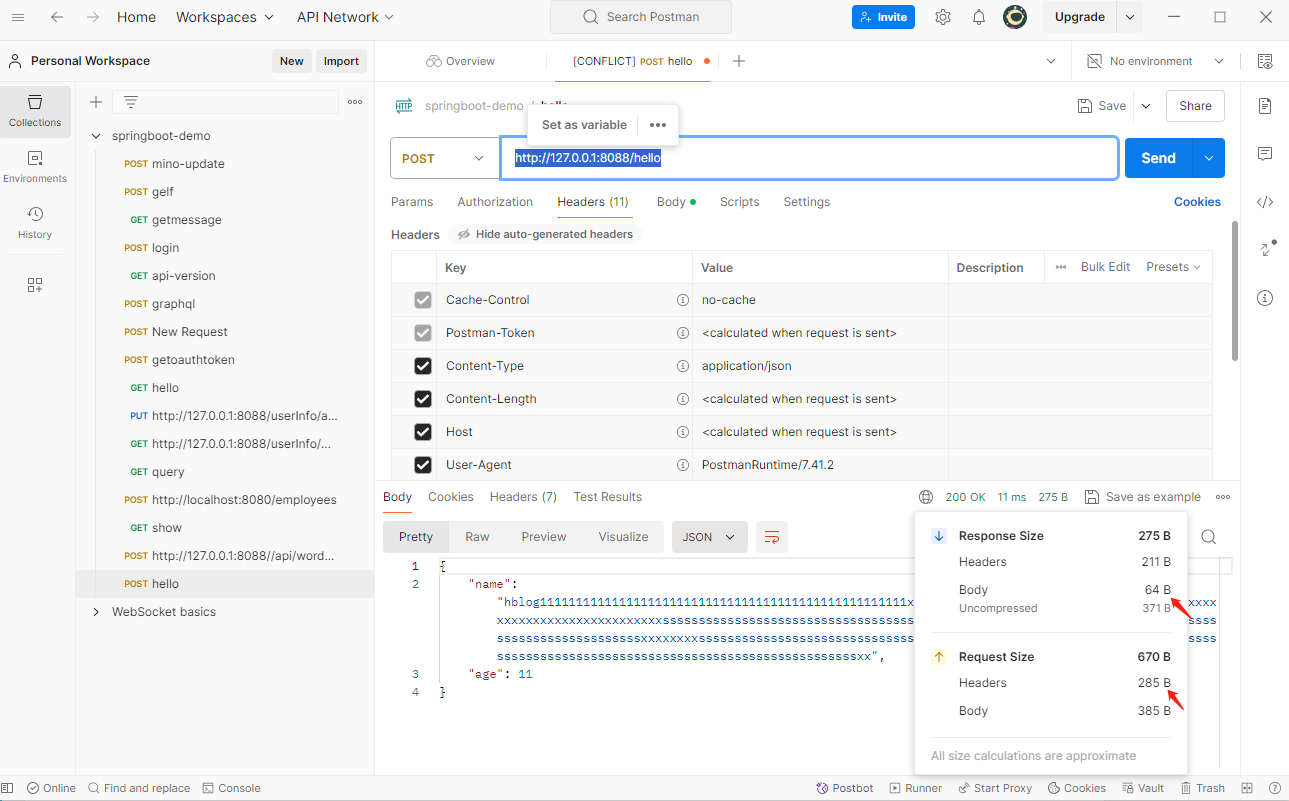

Spring Boot启用GZIP压缩

1.为什么是需要gzip压缩?

经常我们都会与服务端进行大数据量的文本传输,例如 JSON 就是常见的一种格式。通过 REST API 接口进行 GET 和 POST 请求,可能会有大量的文本格式数据提交、返回。然后对于文本,它有很高的压缩率&#x…

systemserver进程监控者--watchdog

戳蓝字“牛晓伟”关注我哦!

用心坚持输出易读、有趣、有深度、高质量、体系化的技术文章,技术文章也可以有温度。

本文摘要

本文同样采用自述的方式来介绍systemserver进程的监控者watchdog,通过本文您将了解watchdog的作用,它…

【机器学习】梯度下降算法

梯度下降算法

这篇博客更加详细,以下只是我个人的理解

梯度下降算法原理讲解——机器学习-CSDN博客

梯度下降算法是一种优化算法,通过梯度下降找到函数最小值时的自变量值。

其基本思想是沿着梯度方向的反方向更新参数,直到逼近函数的极值…

【LLM大模型】生成式人工智能大型语言模型的安全性:概述

生成性AI大型语言模型(LLMs)的安全性:概述

具有生成性AI能力的大型语言模型(如ChatGPT)正面临加速采用和创新。生成性AI(GAI)的日益普及不可避免地引发了对这些模型相关风险和安全性的担忧。本…

Linux 下 gdb 的使用

目录 一、概述1、安装和启动 GDB 二、 GDB 常用命令1、查看源码2、断点2.1 设置断点2.2 查看断点信息2.3 删除断点2.4 激活/禁用断点2.5 观察断点2.6 捕获信号2.7 线程中断 3、查看信息3.1 查看数据3.2 查看内存3.3 查看栈信息3.4 查看栈帧信息 4、运行、调试5、编辑和搜索 一、…

MacOS安装 Python 和 PyCharm

MacOS安装 Python3.12.5 和 PyCharm 小阿呜有话说一、MacOS安装PythonPython官网下载 二、MacOS安装PyCharmPyCharm官网下载 叮嘟!这里是小啊呜的学习课程资料整理。好记性不如烂笔头,今天也是努力进步的一天。一起加油进阶吧! 小阿呜有话说 …

发完朋友圈就“退款”?黑神话的玩家是否都是“忠实粉丝”?

声明:此篇为 ai123.cn 原创文章,转载请标明出处链接:https://ai123.cn/2228.html 《黑神话:悟空》自上线以来,便引发了玩家社区的广泛讨论。游戏的退款现象主要受到了一些技术问题和个人体验差异的影响。部分玩家因遇…

容器的ip地址不稳定问题、联合文件系统、核对时间、制作基础镜像

在docker中部署线上考试系统

1、部署前端服务器 # 上传本地下载的dist文件,因为上传的是目录,加-r选项 scp -r D:\云计算\压缩包\项目\dist root192.168.2.50:/root/ # 创建基础容器 [rootdocker ~]# docker run -it --name c0 centos:latest /bi…

SolidityFoundry BitMap

写合约的时候,记录某个账户的bool状态很常见,例如是否领取空投等,传统的写法mapping(uint256>bool)中一个slot只能存储一个账户的信息,在其他语言中,我们经常会用到bitmap来表示标志位,如果我们可以将bi…