系列文章目录

1.点灯

文章目录

- 系列文章目录

- 前言

- 一、ZYNQ是什么?

- 二、FPGA开发流程

- 1.流程图

- 2.工程管理

- 3.需求分析

- 4.系统框图

- 5.编写RTL代码

- 6.Modelsim 手动仿真

- 7.Vivado工程

- 总结

前言

由于研究生课题组所研制的设备HIGH-POWER SHM SYSTEM是基于ZYNQ的,以下是本人自学ZYNQ的学习记录,所用板卡为:基于 XILINX ZYNQ7000 开发平台的开发板(型号:AX7021B) 2022 款。

一、ZYNQ是什么?

1.FPGA

现场可编程门阵列,是一种以数字电路为主的集成电路芯片,属于可编程逻辑器件。

2.单片机和FPGA

3.Soc

直译是“芯片级系统”,通常简称“片上系统”。,把各种元件整合到一个芯片上。

4.ZYNQ

全可编程片上系统,是一款基于ARM处理器的SoC

二、FPGA开发流程

1.流程图

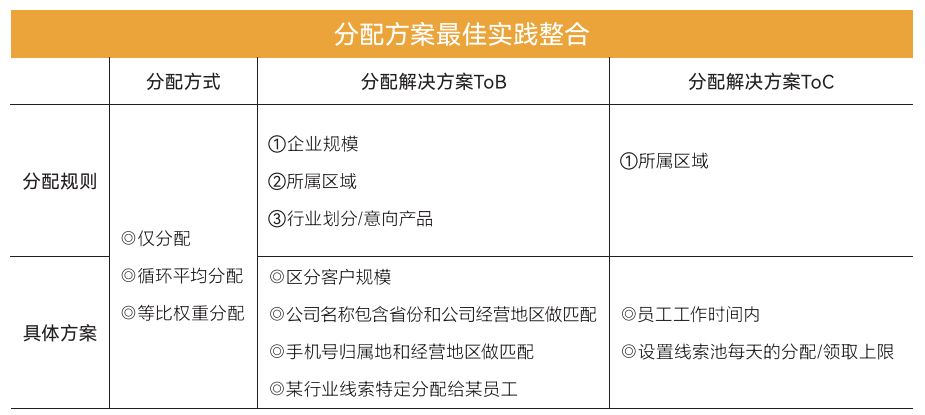

2.工程管理

1.开发过程中使用的辅助文档文件(如绘图软件绘制的波形图文件等),该类文件存放的文件夹我们

命名为 doc;

2.新建工程及产生的文件,该类文件存放的文件夹我们命名为prj;

3.开发过程中的 RTL 代码文件,该类文件存放的文件夹我们命名为 rtl;

4.仿真工程与仿真文件,该类文件存放的文件夹我们命名为sim;

下面我们以点亮 led 灯为例,新建的工程文件管理模板截图如下所示。因为我们使用的 FPGA 开发工具

对工程的路径比较敏感,所以工程路径除了英文、数字以及下划线等,不要出现中文或者其它特殊字符,否则 FPGA 开发工具无法识别工程路径。

3.需求分析

按下按键,灯就亮。

4.系统框图

查阅资料发现,按键KEY2 连接到 ZYNQ 芯片 PL 的 IO 管脚上。按键按下,信号为低, ZYNQ 芯片就是

检测到低电平来判断按键是否按下。

查阅资料发现,当连接用户 LED 灯的 IO电压为高时,用户 LED 灯熄灭,当连接 IO 电压为低时,用户 LED 会被点亮。

于是我们可以得出以下结论:

5.编写RTL代码

led.v

module led(

input key, //输入按键,默认高电平;

//ZYNQ 引脚名:B35_L9_N;ZYNQ 引脚号:A17

output led //输出led,低电平点亮

//ZYNQ 引脚名:B35_L9_P;ZYNQ 引脚号:A16

);

assign led = key;

endmodule

6.Modelsim 手动仿真

编写TestBench,用来验证功能模块的设计是否符合预期:

1.向被测功能模块的输入接口添加激励;

2.例化;

3.判断输出是否满足预期。

`timescale 1ns/1ns //单位/精度

module tb_led();

reg key;

wire led;

initial begin

key <= 1'b1;

#200

key <= 1'b0;

#500

key <= 1'b1;

#1000

key <= 1'b0;

#1000

key <= 1'b1;

end

led u_led(

.key (key),

.led (led)

);

endmodule

一般输入信号定义为寄存器类型(reg),一般输出信号定义为线型(wire)。

编译:

仿真设置:

仿真结果与代码所书写表现一致:

7.Vivado工程

1.新建工程

增添编写好的rtl文件:

器件选型,我使用的板卡为:xc7z020clg484-2

2.分析与综合

I/O分配:

(引脚约束是将FPGA模块的I/O端口与FPGA芯片的物理I/O引脚进行连接的过程。通过引脚约束,可以确保设计在FPGA上的正确实现,避免因引脚分配不当导致的时序问题或功能错误。)

这里根据查阅引脚图,可以看到我使用的板卡key的引脚为A17,led灯的引脚为A16,且两者的供电电压均为3.3V

故配置管脚的电平标准为:LVCMOS33

保存后生成管脚约束文件:

进行综合:

综合后的原理图:

3.设计与实现

可以看见引脚已经有了映射:

4.下载验证

生成比特流文件:

将板卡如下图插入JTAG下载口,并连接到电脑:

点击连接:

烧录:

完结:

(学完车手真的变得好黑)

总结

以上就是今天要讲的内容,本文仅仅简单XILINX ZYNQ7020的使用,如有任何问题请发送邮件至:zelinliu@nuaa.edu.cn