STM使用说明第二篇

- 【1】STM32存储器组织

- 【2】STM32存储器映像

- 【3】嵌入式SRAM

- 【4】STM32位段

- 【5】嵌入式闪存

- 【6】STM32启动配置

【1】STM32存储器组织

程序存储器、数据存储器、寄存器和输入输出端口被组织在同一个4GB的线性地址空间内。

数据字节以小端格式存放在存储器中。一个字里的最低地址字节被认为是该字的最低有效字节,而最高地址字节是最高有效字节。

外设寄存器的映像请参考相关章节。

【可访问的存储器空间被分成8个主要块,每个块为512MB (8*512MB=4096MB=4GB)】。

其他所有没有分配给片上存储器和外设的存储器空间都是保留的地址空间,请参考相应器件的数据手册中的存储器映像图。

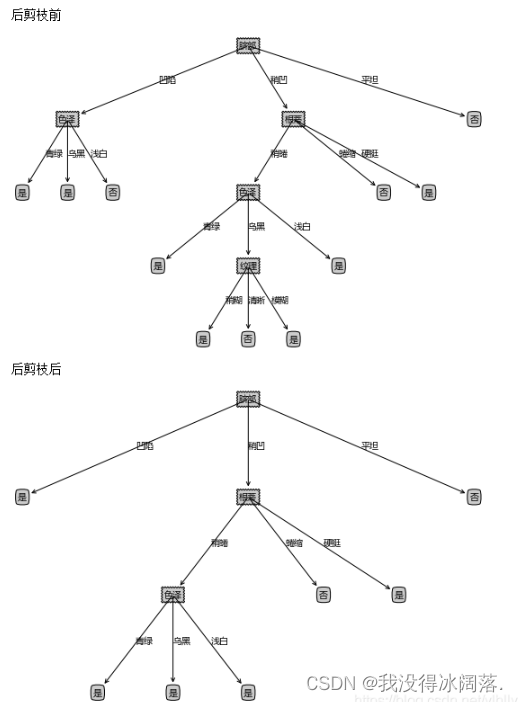

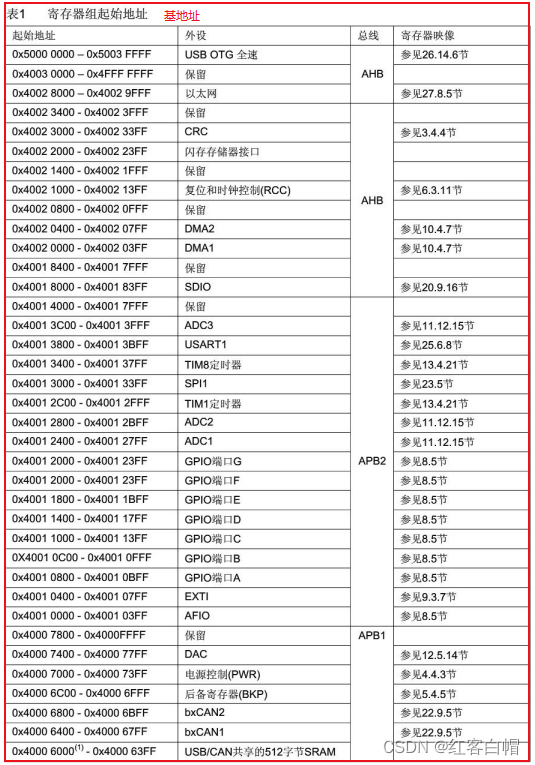

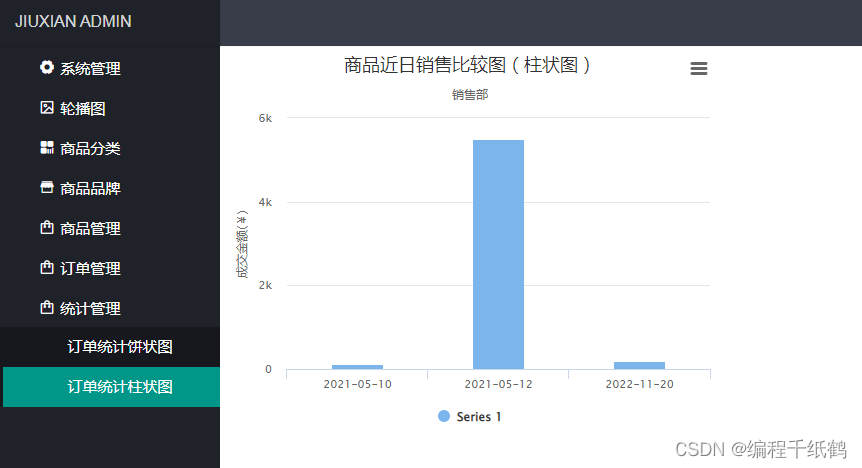

【2】STM32存储器映像

STM32F10xxx中的内置外设的起始地址

【3】嵌入式SRAM

static RAM

STM32F10xxx内置

64K字节的静态SRAM。它可以以字节、半字(16位)或全字(32位)访问。

SRAM的起始地址是0×20000000。

【4】STM32位段

CortexTM-M3存储器映像包括两个位段(bit-band)区。这两个

位段区将别名存储器区中的每个字映射到位段存储器区的一个位,在别名存储区写入一个字具有对位段区的目标位执行读-改-写操作的相同效果。

【在STM32F10xxx里,外设寄存器和SRAM都被映射到一个位段区里,这允许执行单一的位段的写和读操作。】

下面的映射公式给出了别名区中的每个字是如何对应位带区的相应位的:

bit_word_addr = bit_band_base + (byte_offset×32)+ (bit_number× 4)

其中:

`

[1]bit_word_addr是别名存储器区中字的地址,它映射到某个目标位。

[2]bit_band_base是别名区的起始地址。

[3]byte_offset是包含目标位的字节在位段里的序号

[4]bit_number是目标位所在位置(0-31)

`

例子:

下面的例子说明如何映射别名区中SRAM地址为O×20000300的字节中的位2:

0×22006008=0×22000000+(0×300 * 32)+(2*4).

对O×22006008地址的写操作

与对SRAM中地址O×20000300字节的位2执行读-改-写操作有着相同的效果。

读O×22006008地址返回SRAM中地址O×20000300字节的位2的值(OxO1或Ox00)。

【5】嵌入式闪存

高性能的闪存模块有以下的主要特性:

高达512K字节闪存存储器结构:闪存存储器有主存储块和信息块组成:

主存储块容量:

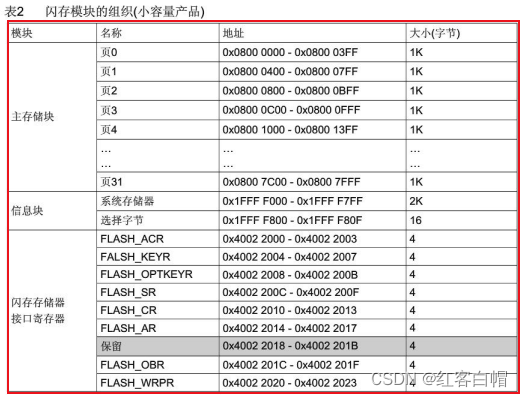

【1】小容量产品主存储块最大为4K×64位,每个存储块划分为32个1K字节的页(见表2)。

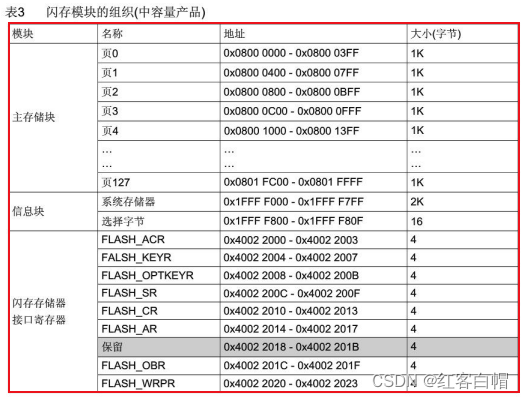

【2】中容量产品主存储块最大为16K×64位,每个存储块划分为128个1K字节的页(见表3)。

【3】大容量产品主存储块最大为64K×64位,每个存储块划分为256个2K字节的页(见表4)。

【4】互联型产品主存储块最大为32K×64位,每个存储块划分为128个2K字节的页(见表5)。

信息块容量:

【1】互联型产品有2360×64位(见表5)。

【2】其它产品有258×64位(见表2、表3、表4)。

表2

表3

表4

表5

闪存读取

闪存的指令和数据访问是通过

AHB总线完成的。

预取模块是用于通过ICode总线读取指令的。

仲裁是作用在flash闪存接口,并且DCode总线上的数据访问优先。

读访问可以有以下配置选项:

【1】等待时间:可以随时更改的用于读取操作的等待状态的数量。

【2】预取缓冲区(2个64位):在每一次复位以后被自动打开,由于每个缓冲区的大小(64位)与闪存的带宽相同,因此只通过需一次读闪存的操作即可更新整个缓冲区的内容。

由于预取缓冲区的存在,CPU可以工作在更高的主频。CPU每次取指最多为32位的字,取一条指令时,下一条指令已经在缓冲区中等待。

【3】半周期:用于功耗优化。

注

1.这些选项应与闪存存储器的访问时间一起使用。等待周期体现了

系统时钟(SYSCLK)频率与闪存访问时间的关系:0等待周期,当0<SYSCLK<24MHz

1等待周期,当24MHz<SYSCLK≤48MHz

2等待周期,当48MHz<SYSCLK≤72MHz

2.

半周期配置不能与使用了预分频器的AHB一起使用,时钟系统应该等于HCLK时钟。该特性只能用在时钟频率为8MHz或低于8MHz时,可以直接使用的内部RC振荡器(HSI)),或者是主振荡器(HSE),但不能用PLL。

3.当

AHB预分频系数不为1时,必须置预取缓冲区处于开启状态。

4.只有在

系统时钟(SYSCLK)小于24MHz并且没有打开AHB的预分频器(即HCLK必须等于SYSHCLK)时,才能执行预取缓冲器的打开和关闭操作。一般而言,在初始化过程中执行预取缓冲器的打开和关闭操作,这时微控制器的时钟由8MHz的内部RC振荡器(HSI))提供。

5.使用DMA:DMA在DCode总线上访问闪存存储器,它的优先级比ICode上的取指高。DMA在每次传送完成后具有一个空余的周期。有些指令可以和DMA传输一起执行。

编程和擦除闪存

【1】 闪存编程一次可以写入16位(半字)。

【2】闪存擦除操作可以按页面擦除或完全擦除(全擦除)。全擦除不影响信息块。

【3】为了确保不发生过度编程,闪存编程和擦除控制器块是由一个固定的时钟控制的。

【4】写操作(编程或擦除)结束时可以触发中断。仅当闪存控制器接口时钟开启时,此中断可以用来从WFI模式退出。

【6】STM32启动配置

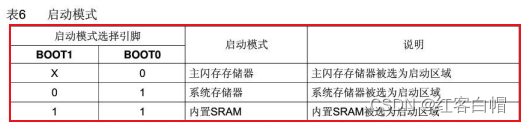

在STM32F10xxx里,可以通过BOOT[1:0]引脚选择三种不同启动模式。

x=0 or 1

在

系统复位后,SYSCLK的第4个上升沿,BOOT引脚的值将被锁存。用户可以通过设置BOOT1和BOOTO引脚的状态,来选择在复位后的启动模式。

在从

待机模式退出时,BOOT引脚的值将被被重新锁存;因此,在待机模式下BOOT引脚应保持为需要的启动配置。

在启动延迟之后,CPU从地址0x00000000获取堆栈顶的地址,并从启动存储器的0x00000004指示的地址开始执行代码。

因为固定的存储器映像,

代码区始终从地址0x00000000开始(通过ICode和DCode总线访问)。

而数据区(SRAM)始终从地址0x2000 0000开始(通过系统总线访问)。

【1】Cortex-M3的CPU始终从ICode总线获取复位向量,即启动仅适合于从代码区开始(典型地从Flash启动)。【2】 STM32F10xxx微控制器实现了一个特殊的机制,

系统可以不仅仅从Flash存储器或系统存储器启动,还可以从内置SRAM启动。

根据选定的启动模式,主闪存存储器、系统存储器或SRAM可以按照以下方式访问:

【1】从主闪存存储器启动:主闪存存储器被映射到启动空间(

0x100000000),但仍然能够在它原有的地址(0x08000000)访问它,即闪存存储器的内容可以在两个地址区域访问,0x00000000或0×08000000。

【2】从系统存储器启动:系统存储器被映射到启动空间(0x00000000),但仍然能够在它原有的地址(互联型产品原有地址为0x1FFFB000,其它产品原有地址为0x1FFFF000)访问它。

【3】从内置SRAM启动:只能在0x20000000开始的地址区访问SRAM。

注意:当从内置SRAM启动,在应用程序的初始化代码中,必须使用NVIC的异常表和偏移寄存器,从新映射向量表之SRAM中。

内嵌的自举程序

内嵌的自举程序存放在系统存储区,由ST在生产线上写入,用于通过可用的串行接口对闪存存储器进行重新编程:

【1】对于小容量、中容量和大容量的产品而言,可以通过

USART1接口启用自举程序。进一步的细节请查询AN2606。

【2】对于互联型产品而言,可以通过以下某个接口启用自举程序:1)USART1、USART2(重映像的)

2)CAN2(重映像的)或USB OTG全速接口的设备模式(通过设备固件更新DFU协议)。

【1】USART接口依靠内部8MHz振荡器(HSI)运行。

【2】CAN和USB OTG接口只能当外部有一个8MHz、14.7456MHz或25MHz时钟(HSE)时运行。进一步的细节请查询AN2606。

下一篇 CRC计算单元

![[Spring MVC 8]高并发实战小Demo](https://img-blog.csdnimg.cn/347f7a828d624a6f8c28f4497d53b483.png)