- Usage

- Description

- physical_block vs. sub_block

- instrument_block

set_design_level 命令的基本内容,以及不同 design level 之间的区分。

Usage

该命令的用法比较简单,主要是区分不同的 design level。

set_design_level {chip | physical_block | sub_block | instrument_block}

Description

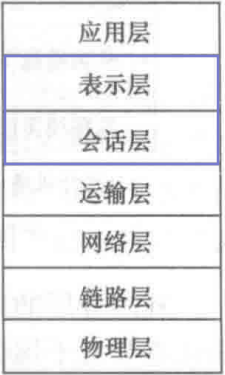

从 dft -rtl 或者 dft -no_rtl context 中进入到 analysis system mode 时候,必须使用该命令指定 design level。

该命令没有默认值,但它会对 create_dft_specification 和 process_dft_specification 两条命令产生影响,所以不许要指定正确的 design level。

使用 process_dft_specification 命令之后立即使用 extract_icl 命令,工具会将 top ICL module 的 tessent_is_physical_module 属性设置为 true。

如果 extract_icl 命令是单独使用的,那么在使用该命令之前,必须设定 design level。

chip

将 design level 设置为 chip 意味着:

- 所有的端口都有一个 pad buffer

- 使用

create_dft_specification命令时会插入一个 TAP

所以,chip 通常指的是芯片的最顶层。此外,根据定义,chip 也算是 physical block。

physical_block vs. sub_block

在标准的 Tessent Shell workflows 中, physical_block 和 sub_block level 用于 child block,chip level 用于 top 。

区分 physical block 和 sub-block 是十分重要的,其不同之处如下所述:

physical block 在 synthesis 和 layout 中是一个独立的个体。

如果 physical block 在另一个 physical block 中实例化,那么在对 parent physical block 进行综合(synthesizing)时,综合工具或者 layout 工具并不会加载 child physical block 的 netlist view,而是使用 child physical block 的 timing model。

也就是说,parent physical block 的 SDC 只能参考 child physical block 的 pins,而不能参考 child physical block 中的 elements。

但是对于 parent physical block 中的 sub-block 而言,-to 或者 -from 不能参考 sub-block 的 pins,可以参考 sub-block 中的 elements。

sub-block 的 netlist 通常只是 parent physical block netlist 的一部分,在对 physical block 进行 scan insertion 的时候带上 sub-block。

但是,如果是 child physical block,可以单独对其进行扫描链的插入,然后将这些扫描链连接到 parent physical block 的扫描链。

【简单来说,在综合之后,sub-block 会融合到 parent physical block,不再有明显的边界,不能对其单独操作,但是 child physical block 会有明显的边界,可以单独对其进行操作。】

在 RTL DFT flow 中,sub-block 经常被当作 physical block。

在使用 read_def 命令提取 memories 的布局信息用于为每个 physical cluster 构建 memoryBIST 控制器时,如果是对 sub-block 进行 mbist 插入,就必须使用 -instance_of_current_design 选项。

因为根据定义,只能得到 physical block 的 DEF 文件,而不能得到 sub-block 的 DEF 文件,因为 sub-block 被综合到 parent physical block 中。只能使用 parent physical block 的 DEF 文件,并使用 -instance_of_current_design 指定 sub-block 在其中的实例路径。

在 signoff 仿真中,test benches 按照 physical block 进行划分,用以优化性能。

对于 sub-block modules,会作为 parent physical block 的一部分,同 parent physical block 一起仿真。因为在 gate-level 仿真的时候,只有 physical block 的 netlist 和 SDF 文件,sub-blocks 被综合到 parent physical block 中。

使用 read_design 命令加载一个 sub-block 到工具中的时候,如果它不是 current_design 并且使用 -rtl context,is_hard_module 属性会被自动推断为 true。

【is_hard_module是 Data Models 中 module 的一个属性,它为 true 意味着该模块不能被编辑。类型为 cell 或者 primitive 的所有模块该属性都会被自定设置为 true。】

在对 current design (不是 sub-block,但其中包含 sub-block)进行 DFT elements 插入的时候,链接关系只能添加到 sub-block 模块的 pins。

如果想要在 sub-block 的内部添加内容,就必须将 sub-block 模块设置为 current design,然后再 sub-block level 进行内容添加(以及 sub-block 对应的 ICL 文件的提取)。

在 parent physical region 提取 ICL 的时候,是要复用 sub-block 的 ICL 描述,并且要从 sub-block 的 pins 向外追踪。

instrument_block

一个特殊的空模块,其中插入了 DFT elements。需要在 parent block 中手动实例化,并手动将其 pins 连接到 parent block。

如果不想要 Tessent Shell 修改 golden RTL,一个常用的 flow 是手动在 design block 中插入 DFT module。然后将该 DFT module 设置为 current_design,将该模块的 design level 设置为 instrument_block,使用 Tessent DFT flow 在其中插入 IjtagNetwork、EDT 控制器、SSN

该 DFT module 包含预先存在的的端口(clock、IJTAG network and SSN ports),需要预先手动将其连接到 parent module。

对该 DFT module 完成 DFT 插入之后,该 block 的 parent ,就好像你在该 level 完成了正常的 DFT flow。添加在 DFT module 的 DFT signals 会存在于 parent level。在 parent module 进行 ICL 提出之后,child DFT block 的 DFT elements 也会存在于 parent block’s TSDB 中。

示例:

首先,一个空的 DFT module ,其中包含了 IJTAG 和 SSN 的端口定义,以及每个功能时钟的输入和输出端口。

也可以为 all_test 和 async_set_reset_dynamic_disable 这两个 DFT 信号创建输出端口,用于在 scan shifting 过程中控制 clock mux 和 disable Async Set Reset signals。

然后,手动实例化并连接该 DFT module 到 parent module 中。

将 golden RTL 中的所有 clk 修改为 clk_occ,这样所有 scannable elements 是时钟都由即将插入到 block 的 OCC 控制。

将该 DFT module 当作普通的模块进行 DFT insertion,但是有两种不同:

在 next level,正常的读取设计并使用 read_design 命令加载 DFT module。定义时钟之后,执行 DRC。

在使用extract_icl命令时,就好像是使用正常的 flow 在当前 level 进行了 DFT element 的差人。ICL 提取完成之后,可以到 DFT context 中验证 RTL 具有可控制的时钟和复位信号。

![[oeasy]python0028_女性程序员_Eniac_girls_bug_Grace](https://img-blog.csdnimg.cn/img_convert/770518fc71098e60a5f0cba350d42c8c.png)