目录

一、前言

二、VCD文件格式

2.1 头部

2.2 变量定义

2.3 值打印

2.4 值变化部分

2.5 VCD文件示例

三、VCD文件生成

3.1 工程代码

3.2 modelsim操作

3.3 VCD结果查看

3.4 VCD类型2

四、参考资料

一、前言

VCD(Value change dump)是一个ASCII文件,里面有关于给定设计的头信息,变量的定义,以及指定的变量或所有变量的值变化信息,变量的值变化可以是标量或矢量格式。VCD文件一般是由EDA仿真工具生成。

二、VCD文件格式

VCD文件由头部,变量定义,打印变量,值变化四个部分组成。每一条语句内容都以关键字"$"开头,后面跟着命令名,以关键字“$end”结束,所有的VCD标记以空格,并且字母严格区分大小写。

VCD keywords are marked by a leading $; in general every keyword starts a command which is terminated by an explicit $end. Variable identifiers may also start with a $, but these may be distinguished by context.

All VCD tokens are delineated by whitespace. Data in the VCD file is case sensitive.

2.1 头部

头部包含了时间戳,仿真器版本,时间精度(用于指定在值变化部分中映射时间增量的仿真时间单元)

2.2 变量定义

变量定义包含了在给定范围内的信号初始化信息。每个变量赋值了一个随机值标识,标识是由一个或多个ASCII字符(从!到~,对应的十进制范围为33-126),通常是一个或两个字符。如果仿真器确定多个变量有相同的值,则可以共用一个标识。

每一行变量定义以"$var"开头,后面紧跟的是变量类型,数据宽度,标识符,变量名。

上述中的给定范围中范围类型定义和verilog中的定义一致,类型包括模块,任务,函数,fork块。

2.3 值打印

该部分以$dumpvars或$dumpports开头,主要是变量的初始值

2.4 值变化部分

值变化部分包含了仿真模型中信号随时间的变化值信息,变量所处的时间通过“#”加时间值。对于标量信号,信号的值用0或1表示,对于矢量信号(多比特信号),信号值格式用“b”或“B”,后面紧跟二进制值,然后是信号标识。对于实数变量用“r”或“R”开头,数据用%标识

2.5 VCD文件示例

###头部###

$date

Date text. For example: November 11, 2009.

$end

$version

VCD generator tool version info text.

$end

$comment

Any comment text.

$end

$timescale 1ps $end

###变量定义,范围为module模块级####

$scope module logic $end ###表示变量属于哪一个类型,此处为模块级###

$var wire 8 # data $end ###此处变量类型为wire,宽度为8,标识符为#,变量名为data

$var wire 1 $ data_valid $end

$var wire 1 % en $end

$var wire 1 & rx_en $end

$var wire 1 ' tx_en $end

$var wire 1 ( empty $end

$var wire 1 ) underrun $end

$upscope $end

$enddefinitions $end ###表示头信息和变量定义部分的结束

###值打印部分###

$dumpvars

bxxxxxxxx #

x$

0%

x&

x'

1(

0)

$end

#0

b10000001 #

0$

1%

0&

1'

0(

0)

#2211

0'

#2296

b0 #

1$

#2302

0$

#2303

三、VCD文件生成

下面将展示以4种触发器的verilog代码,使用modelsim生成vcd为例

3.1 工程代码

module FF(clk,d,rst,cls,out_syn_clear,out_syn_set,out_asyn_clear,out_asyn_set);

input clk,d,rst,cls;

output out_syn_clear,out_syn_set,out_asyn_clear,out_asyn_set;

//同步清零

always@(posedge clk ,posedge rst )

begin

if(rst)

out_syn_clear<=1'b0;

else

if (cls)

out_syn_clear<=1'b0;

else

out_syn_clear<=d;

end

//同步置位

always@(posedge clk,posedge cls)

begin

if(rst)

out_syn_set<=1'b1;

else if (cls)

out_syn_set<=1'b0;

else

out_syn_set<=d;

end

//异步清零

always@(posedge clk or posedge cls)

begin

if(cls)

out_asyn_clear<=1'b0;

else

out_asyn_clear<=d;

end

//异步置位

always@(posedge clk or posedge rst)

begin

if(rst)

out_asyn_set<=1'b1;

else

out_asyn_set<=d;

end

endmodule3.2 modelsim操作

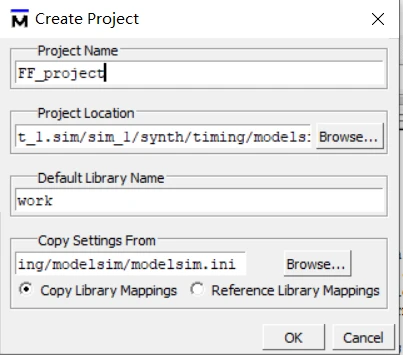

modelsim版本为Modelsim SE-64 2020.4,在File->New->Project 新建一个工程

在Project Name中输入工程名,此处以FF_project示例,其他选择默认即可

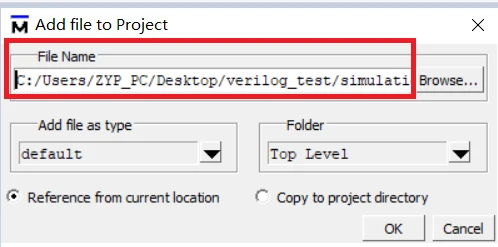

因为源文件FF.v已存在,所以选择Add Existing File

File Name中选择FF.v的路径

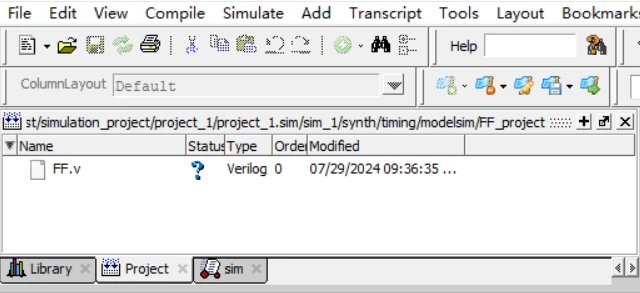

project窗口中添加成功的显示

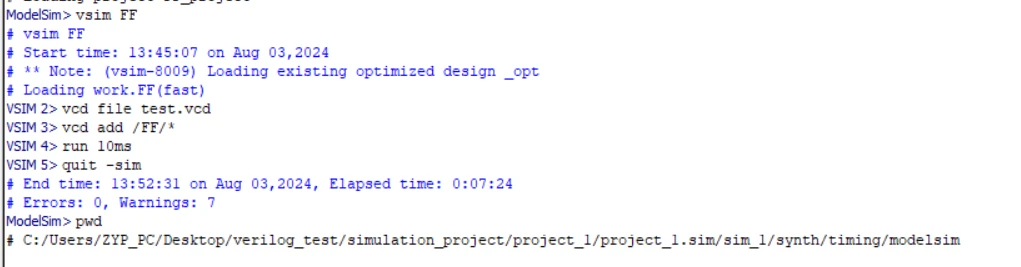

在modelsim的Transcript窗口依次执行如下命令

>Vsim FF #对FF.v文件进行仿真

>vcd file test.vcd #创建名称为test的vcd文件

>vcd add /FF/* #将FF中的所有信号添加到vcd文件中

>run 10ms #运行仿真,时间为10ms

>quit -sim #停止仿真

>pwd #查看vcd文件的生成路径使用pwd命令

3.3 VCD结果查看

$date

Sat Aug 03 13:52:16 2024

$end

$version

ModelSim Version 2020.4

$end

$timescale

1fs

$end

$scope module FF $end

$var wire 1 ! clk $end

$var wire 1 " d $end

$var wire 1 # rst $end

$var wire 1 $ cls $end

$var reg 1 % out_syn_clear $end

$var reg 1 & out_syn_set $end

$var reg 1 ' out_asyn_clear $end

$var reg 1 ( out_asyn_set $end

$upscope $end

$enddefinitions $end

#0

$dumpvars

x%

x&

x'

x(

z!

z"

z#

z$

$end3.4 VCD类型2

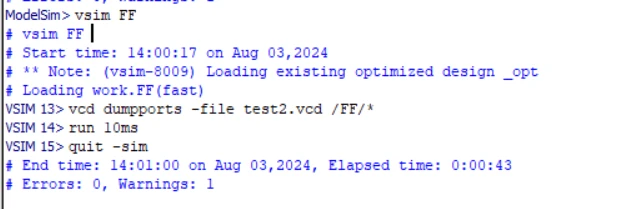

上述方式生成的vcd文件只有四种状态0,1,X,Z,还有一种方式可以生成更多信息,包含参数的全部变化状态,信号强度和端口驱动数据。

命令如下

>Vsim FF #对FF.v文件进行仿真

>vcd dumpports -file test2.vcd /FF/* #创建名称为test2的vcd文件,同时使用dumpports打印

>run 10ms #运行仿真,时间为10ms

>quit -sim #停止仿真

vcd结果如下图,和之前的vcd文件区别是后面的dumpvars变成了dumpports,也包含端口的变化

$comment

File created using the following command:

vcd file test2.vcd -dumpports

$end

$date

Sat Aug 03 14:00:39 2024

$end

$version

dumpports ModelSim Version 2020.4

$end

$timescale

1fs

$end

$scope module FF $end

$var port 1 <0 clk $end

$var port 1 <1 d $end

$var port 1 <2 rst $end

$var port 1 <3 cls $end

$var port 1 <4 out_syn_clear $end

$var port 1 <5 out_syn_set $end

$var port 1 <6 out_asyn_clear $end

$var port 1 <7 out_asyn_set $end

$upscope $end

$enddefinitions $end

#0

$dumpports

pZ 0 0 <0

pZ 0 0 <1

pZ 0 0 <2

pZ 0 0 <3

pX 6 6 <4

pX 6 6 <5

pX 6 6 <6

pX 6 6 <7

$end

$vcdclose

#10000000000000

$end四、参考资料

https://en.wikipedia.org/wiki/Value_change_dump