目录

微信公众号获取更多FPGA相关源码,且微信公众号为首发,第一时间获取最新文章:

计数器是一种典型的时序器件,常用于对时钟脉冲的个数进行计数,还用于定时、分频、产生同步脉冲等

按触发方式分:同步计数器和异步计数器

在使用硬件描述语言设计计数器时,不需要专门设计触发器,而是直接对寄存器变量进行操作

module mod5cnt(input rst, input clk, output reg [2:0]q);

always@(posedge clk, posedge rst)

begin

if(rst==1)

q<=0;

else if(q==4)

q<=0;

else

q<=q + 1;

end

endmodule

N位计数器:

计数器基本引脚:

- 时钟输入端:clk

- 复位端: rst

- 计数输出端:cnt

module cnt_en (rst,clk,cnt)

#(parameter N = 8);

input rst,clk;

output [N -1:0] cnt;

reg [N -1:0] cnt;

always@(posedge clk , posedge rst)

begin

if(rst==1’b1)

cnt<=8’b00000000;

else

cnt<=cnt + 1;

end

endmodule

实现16位的计数器:(例化cnt_cn模块)

cnt_en #(.N(16)) cnt16(.rst(clr),.clk(clk),.cnt(q));

例:10进制计数器

module counter(clk, clr, out, cout);

input clk, clr;

output[4:1] out;

output cout;

reg[4:1] out;

always @(posedge clk or negedge clr)

begin

if(!clr) out = 0;

else out = (out == 4‘h9) ? 0 : (out + 1);

end

assign cout = (out == 4'h9) ? 1 : 0;

endmodule

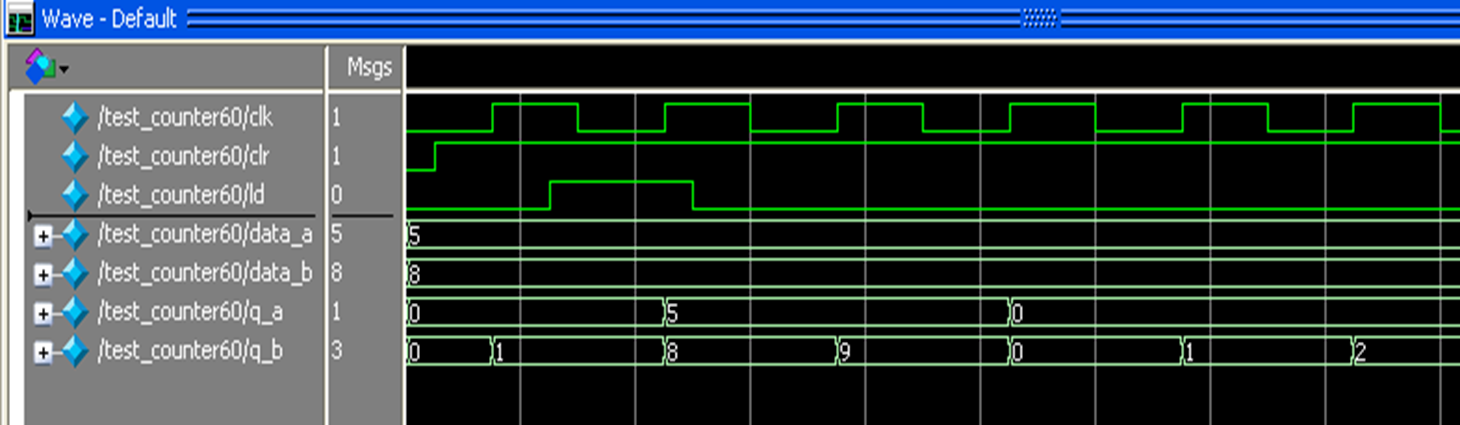

例:60进制计数器设计

60进制计数器的显示需要两个数码管。其中一个数码管显示计数低位0-9,另一个数码管显示计数高位0-5。为了与两个数码管相连,可以设计两个4位寄存器变量:一个寄存器变量为0-9的变化;另一个寄存器变量为0-5的变化。

always @(posedge clk or negedge clr)

begin

if(!clr) {temp_a,temp_b} = 0

else

if(ld == 1) {temp_a,temp_b} = {data_a, data_b};

else begin

if({temp_a,temp_b} = = 8'h59) {temp_a,temp_b} = 0

else if(temp_b = = 9)

begin

temp_b = 0;

temp_a = temp_a + 1;

end

else temp_b = temp_b + 1;

end

end

计数器可以去看之前的文章,封好为IP核可以直接使用:FPGA搭积木之计数器

链接:https://mp.weixin.qq.com/s/YGLIwpxsCxuMrUC-zXGYoQ

微信公众号获取更多FPGA相关源码,且微信公众号为首发,第一时间获取最新文章: