首先,用primetime 抽 timing model 的指令如下。

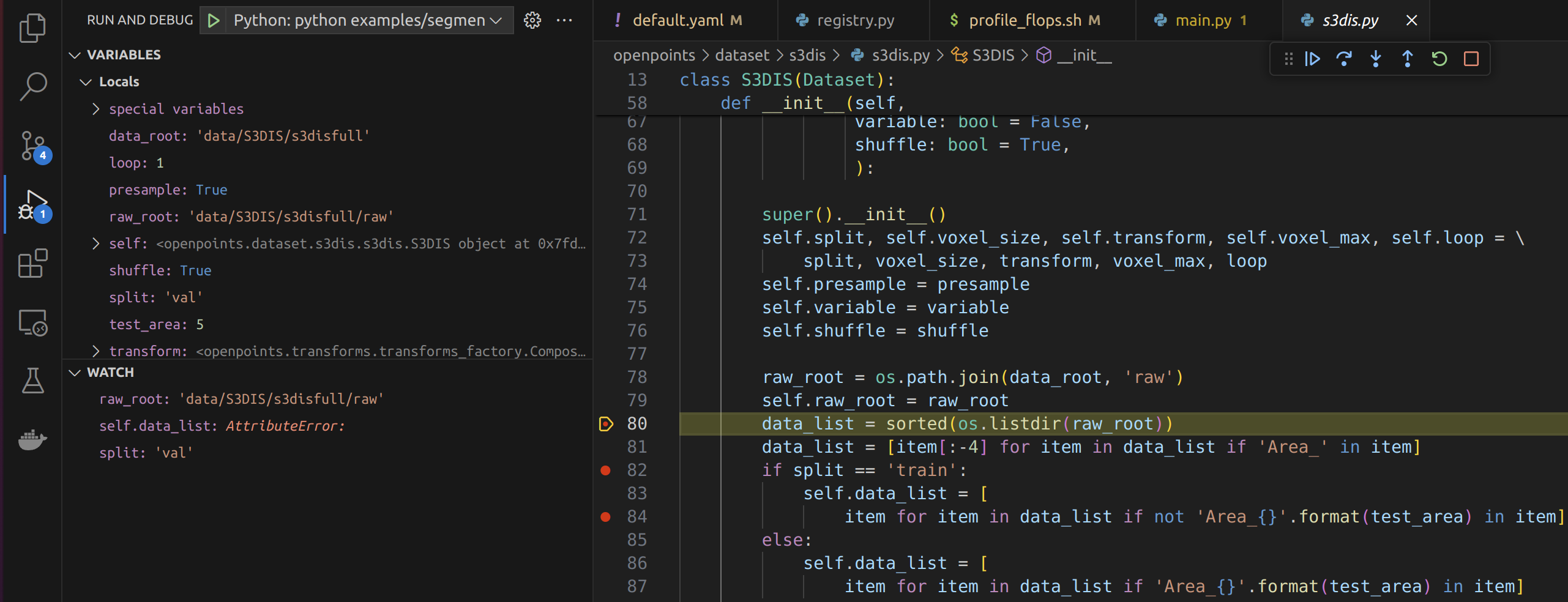

代码如下(示例):

#抽lib时留一些margin, setup -max/hold -min

set_extract_model_margin -port [get_ports -filter "!defined(clocks)"] -max 0.1

#抽lib

extract_model -noise -test_design -format {lib} -output top_func_setup_ssgnp0p675vm40c

#压缩lib

sh gzip top_func_setup_ssgnp0p675vm40c.lib

The extract_model command generates a static timing model for the current design from its gate-level netlist. The generated model exhibits the same timing characteristics as the original design and therefore is used instead of the gate-level netlist for timing analysis

at a higher level of the design hierarchy. To also generate noise or power information in the model, use the -noise or -power option.

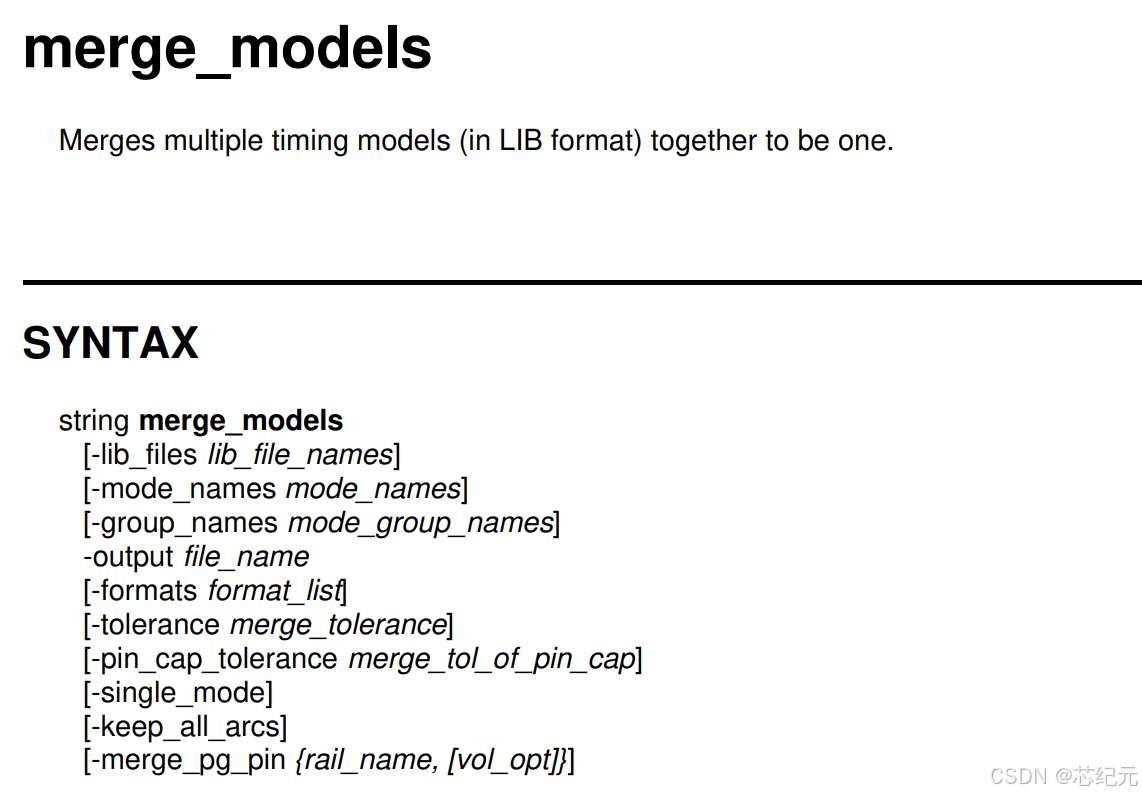

在抽完lib之后,如果想要合并不同modes的libs到一个lib文件需要用merge_models。This command can merge multiple timing models together to be one. The timing models must be in Synopsys internal library (.lib) format. This command reads in all the specified files to generate a list of timing models. These timing models are processed, matched, compared, and merged to create a single timing model. This model has moded timing arcs such that, in any given mode, the static timing behavior of the merge model is equivalent to one of the models merged. The final merged model is saved on disk in the specified files and requested formats. PrimeTime and Design Compiler recognize the merged model with moded timing arcs for performing timing analysis.

代码如下(示例):

set modes {func at_speed scan_shift scan_capture}

set libs {top_func_setup_ssgnp0p675vm40c.lib.gz top_at_speed_setup_ssgnp0p675vm40c.lib.gz top_scan_shift_setup_ssgnp0p675vm40c.lib.gz top_scan_capture_setup_ssgnp0p675vm40c.lib.gz}

merge_models -lib_files "$libs" -mode_names "$modes" -format {lib} -output top_setup_ssgnp0p675vm40c

另外,如果想要把lib转成db,可以使用下面的指令。

#启动library compiler

lc_shell -f ./lib2db.lc

#lib2db.lc内容

read_lib top_setup_ssgnp0p675vm40c.lib >> lc_shell.log

write_lib top_setup_ssgnp0p675vm40c -format {db} -output top_setup_ssgnp0p675vm40c.db >> lc_shell.log