1、ARM v7寄存器

1.1 通用寄存器

V7 V8开始 FIQ个IRQ优先级一样,

通用寄存器:31个

1.2 程序状态寄存器

CPSR是程序状态毒存器,保存条件标志位,中断禁止位,当前处理器模式等控制和状态位。每种异常模式下还存在SPSR,保存进入异常模式前的CPSR寄存器值,用于异常处理完成后恢复CPSR的状态。User和Sys不属于异常模式,没有CPSR寄存器,在User模式下,受限的CPSR存器称谓APSR(Application Program Status Register)。ARMV7-A中CPSR寄存器的信息如下图所示。

| Field | 作用 |

|---|---|

| N | ALU返回运算结果是否为负数 |

| Z | ALU返回运算结果是否为0 |

| C | ALU运算是否发生进位 |

| V | ALU运算是否发生溢出 |

| Q | cumulative saturation |

| J | ARM是否处于 Jazelle 状态 |

| E | 控制load/store字节序 |

| A | disables asynchronous aborts,User模式不能操作 |

| I | 使能/去使能IRQ,User模式不能操作 |

| F | 使能/去使能FIQ,User模式不能操作 |

| T | ARM和Thumb状态标志位 |

| GE | 用于某些SIMD(Single Instruction, Multiple Data)指令 |

| M[4:0] | 处理器模式:FIQ,IRQ,ABT,SVC,UND,MON,HYP。User模式不能操作 |

1.3 Coprocessor 15(CP15)寄存器

在ARM v7 上所有的系统寄存器都是按CP15寄存器操作,使用MRC 和MCR指令操作。【ARM V8和ARM V9之后可以直接操作系统寄存器,通过MRS指令操作。】

————————————————————————————————————————————————

MRC p15,0,r0,c1,c0,0; Read System Contril Register configuration data 读协处理器到通用寄存器

ORR r0,r0,#(1<<2) ;set C bit

ORR r0,r0,#(1<<12) ;set I bit

ORR r0,r0,#(1<<11) ;set Z bit

MCR p15 ,0, r0,c1,c0,0 ; Write System Contril Register configuration data 从通用寄存器写回到协处理器

————————————————————————————————————————————————

思考:

1.协处理器是做什么的?

它是Core中,专门用来操作系统寄存器的,所有系统寄存器通过co-processor操作的。

2.aarch64中有没有协处理器?

没有了,后面V8,V9架构之后直接对系统寄存器进行操作。

1.4 系统控制寄存器(cp15.sctlr)

系统控制寄存器SCTLR(System Control Register )用于控制内存,系统功能以及提供状态信息。

2 ARM v8 & ARMv9寄存器介绍

本节内容来自网上

这里介绍的都是AArch64的寄存器。

寄存器分类:

1.general purpose

2.PSTATE Special

3.Other(如sctlr)

4.ID

5.Memory

6.Cache,Address,TLB

7. pmu

8. Exception,Reset

9. Root

10.Secure

11.Virt

12.Timer

13.Thread

14.IMP DEF

15.Debug

16.Trace

17.CTI

18.Float

19.Legacy

20.RAS

21.MPAM

22.Pointer authentication

23.AMU

24.GIC,GICD,GICR,GICC,GICV.GICH,GITS

2.1 AArch64 general-purpose registers

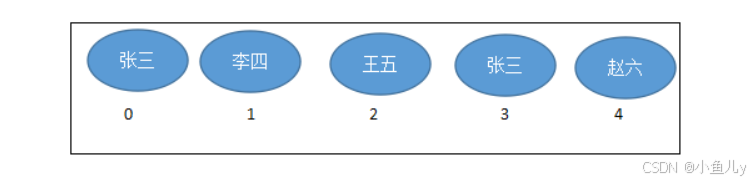

AArch64执行状态提供了32个在任何时间任何特权级下都可访问的64位的通用寄存器每个寄存器都有64位宽,它们通常被称为寄存器X0-X30。

每个AArch64 64位通用寄存器(X0-X30)也具有32位(W0-W30)形式。

32位W寄存器取自相应的64位X寄存器的低32位。也就是说,W0映射到X0的低32位,W1映射到X1的低32位。

从W寄存器读取时,忽略相应X寄存器高32位,并保持其它不变。写入W寄存器时,将X寄存器的高32位设置为零。

eg:将0xFFFFFFFF写入W0会将X0设置为0x00000000FFFFFFFF。

2.2 AArch64 special registers

除了31个核心寄存器外,还有几个特殊的寄存器。

注意:没有被称为X31或W31的寄存器。许多指令被编码,例如:31代表零寄存器ZR(WZR/XZR)。还有一组受限制的指令,其中对一个或多个参数进行编码,使数字31表示堆栈指针(SP)。

当访问零寄存器时,所有写操作都被忽略,所有读操作返回0。请注意,64位形式的SP寄存器不使用X前缀。

在ARMv8体系结构中,当CPU运行在AArch64状态时,异常返回状态保存在每个异常级别的以下专用寄存器中:

- Exception Link Register (ELR).

- Saved Processor State Register (SPSR).

每个异常级别都有一个专用的SP寄存器,但它不用于保存返回状态

2.2.1 零寄存器

零寄存器当用作源寄存器时读操作的结果为零,当用作目标寄存器时则将结果丢弃。你可以在大多数指令中但不是所有指令中使用零寄存器。

2.2.2 栈指针

在ARMv8体系结构中,要使用的栈指针的选择在一定程度上与异常级别是分开的。默认情况下,发生异常时会选择目标异常级别的SPELn作为栈指针。例如,当触发到EL1的异常时,就会选择SP_EL1作为栈指针。每个异常级别都有自己的栈指针,SP_EL0、SP_EL1、SP EL2和SP _EL3。

当AArch64处于ELO以外的异常级别时,处理器可以使用:

- 与该异常级别相关联的一个专用的64位栈指针(SP_ELn)

- 与ELO关联的栈指针(SP_EL0)

ELO永远只能访问SP ELO.

t后缀表示选择了SP_EL0栈指针。h后缀表示选择了SP_ELn栈指针。

虽然大多数指令都无法使用SP寄存器。但是有一些形式的算术指令可以操作SP。

eg:ADD指令可以读写当前的栈指针以调整函数中的栈指针。

ADD SP,SP, #x10 // Adjust sp to be x10 bytes before its current value

2.2.3 程序计数器

原来的ARMv7指令集的一个特性是R15作为程序计数器(PC),并作为一个通用寄存器使用。PC寄存器的使用带来了一些编程技巧,但它为编译器和复杂的流水线的设计引入了复杂性。在ARMv8中删除了对PC的直接访问,使返回预测更容易,并简化了ABI规范。

PC永远不能作为一个命名的寄存器来访问。但是,可以在某些指令中隐式的使用PC,如PC相对加载和地址生成。PC不能被指定为数据处理或加载指令的目的操作数。

2.2.4 异常链接寄存器(ELR)

异常链接寄存器保存异常返回地址。

2.2.5程序状态保存寄存器(SPSR)

当异常发生时,CPSR中的处理器状态将保存在相关的程序状态保存寄存器(SPSR)中,其方式类似于ARMV7。SPSR保存着异常发生之前的PSTATE的值,用于在异常返回时恢复PSTATE的值。

AArch64下各bit的含义:

| bit | 含义 |

|---|---|

| N | 负数标志位,如果结果为负数,则N=1;如果结果为非负数,则N=0。 |

| Z | 零标志位,如果结果为零,Z=1,否则Z=0。 |

| C | 进位标志位 |

| V | 溢出标志位 |

| SS | 软件步进标志位,表示当一个异常发生时,软件步进是否开启 |

| IL | 非法执行状态位 |

| D | 程序状态调试掩码,在异常发生时的异常级别下,来自监视点、断点和软件单步调试事件中的调试异常是否被屏蔽。 |

| A | SError(系统错误)掩码位 |

| I | IRQ掩码位! |

| F | FIQ掩码位 |

| M[4] | 异常发生时的执行状态,0表示AArch64 |

| M[3:0] | 异常发生时的mode或异常级别 |

2.3 Processor State处理器状态

AArch64没有直接与ARMv7当前程序状态寄存器(CPSR)等价的寄存器。在AArch64中,传统CPSR的组件作为可以独立访问的字段提供。这些状态被统称为处理器状态(PSTATE)。

AArch64的处理器状态或PSTATE字段有以下定义:

| bit | Description |

|---|---|

| N | Negative condition flag |

| Z | Zero condition flag |

| C | Carry condition flag |

| V | oVerflow condition flag |

| D | Debug mask bit. |

| A | SError mask bit. |

| I | IRO mask bit. |

| F | FlO mask bit. |

| SS | FlO mask bit. |

| IL | Illegal execution state bit. |

| EL(2) | Exception level. |

| nRW | Execution state:0=64-bit 1 =32-bit |

| SP | Stack Pointer selector:0=SP ELO1=SP ELn |

在AArch64中,你可以通过执行ERET指令从一个异常中返回,这将导致SPSRELn被复制到PSTATE中。这将恢复ALU标志、执行状态、异常级别和处理器分支。从这里开始,将继续从ELR ELn中的地址开始执行。

PSTATE.N,Z.C,V字段可以在EL0级别访问。 其他的字段可以在EL1或更高级别访问,但是这些字段在ELO级别未定义。

2.3.1 Processor State 使用示例

| Operand | PSTATEfields | Notes |

|---|---|---|

| DAIFSet | D,A,I,F | Directly sets any of the PSTATE.(D A L E} bits to 1 |

| DAIFCIr | D,A,I,F | Directly clears any of the PSTATE.(D, A, I, F} bits to 0 |

Switch to the runtime stack i.e. SP ELO

ldr x2,[sp,#CTX EL3STATE OFFSET + CTX RUNTIME SP]

MoV x20,sp

msr spsle , #MODE SP ELO

mov sp,x2

2.4 系统寄存器

在AArch64中,系统配置通过系统寄存器进行控制,并使用MSR和MRS指令进行访问。这与ARMV7-A形成了鲜明对比,在ARMV7-A中,这些寄存器通常通过协处理器15(CP15)操作来访问。寄存器的名称会告诉你可以访问它的最低异常级别。

eg:

- TTBRO EL1可以从EL1、EL2和EL3访问,

- TTBRO EL2可以从EL2和EL3访问

可以采用以下形式来访问系统寄存器

MRS xO,TTBRO EL1//Move TTBRO EL1 into x8

MSR TTBRO EL1,x0// Move xe into TTBRO EL1

下表来自网上

ARM架构的之前版本使用协处理器来进行系统配置。 但是,AArch64不支持协处理器。

下表显示了异常级别,这些异常级别具有每个寄存器的单独副本。 例如,单独的辅助控制寄存器(ACTLR)以ACTLR_EL1,ACTLR_EL2和ACTLR_EL3的形式存在。

| 名称 | 寄存器 | 说明 | n的允许值 |

|---|---|---|---|

| ACTLR_ELn | 辅助控制寄存器 | 控制处理器特定的功能。 | 1,2,3 |

| CCSIDR_ELn | 当前缓存大小ID寄存器 | 提供有关当前所选缓存的体系结构的信息。 | 1 |

| CLIDR_ELn | 缓存级别ID寄存器 | 在每个级别上实现的单个或多个高速缓存的类型缓存层次结构的一致性级别和统一级别。 | 1,2,3 |

| CNTFRQ_ELn | 计数器频率寄存器 | 报告系统计时器的频率。 | 0 |

| CNTPCT_ELn | 计数器物理计数寄存器 | 保持64位的当前计数值。 | 0 |

| CNTKCTL_ELn | 计数器内核控制寄存器 | 控制从虚拟计数器生成事件流。还控制从EL0访问物理计数器,虚拟计数器,EL1物理计时器和虚拟计时器。 | 1 |

| CNTP_CVAL_ELn | 计数器物理计时器比较值寄存器 | 保存EL1物理计时器的比较值。 | 0 |

| CPACR_ELn | 协处理器访问控制寄存器 | 控制对跟踪,浮点和SIMD功能的访问。 | 1 |

| CSSELR_ELn | 缓存大小选择寄存器 | 通过指定所需的缓存级别和缓存类型(指令或数据缓存),选择当前的缓存大小ID寄存器CCSIDR_EL1。 | 1 |

| CNTP_CTL_ELn | 计数器物理控制寄存器 | 控制EL1物理计时器的寄存器。 | 0 |

| CTR_ELn | 缓存类型寄存器 | 有关集成缓存体系结构的信息。 | 0 |

| DCZID_ELn | 数据缓存零ID寄存器 | 指示数据缓存零根据虚拟地址(DCZVA)系统指令写入字节值为0的块大小。 | 0 |

| ELR_ELn | 异常链接寄存器 | 保存导致异常的指令的地址。 | 1,2,3 |

| ESR_ELn | 异常综合特征寄存器 | 包括有关异常原因的信息。 | 1,2,3 |

| FAR_ELn | 故障地址寄存器 | 保存虚拟错误地址。 | 1,2,3 |

| FPCR | 浮点控制寄存器 | 控制浮点扩展行为。该寄存器中的字段映射到AArch32 FPSCR中的等效字段。 . | |

| FPSR | 浮点状态寄存器 | 提供浮点系统状态信息。该寄存器中的字段映射到AArch32 FPSCR中的等效字段。 . | |

| HCR_ELn | Hypervisor 配置寄存器 | 控制虚拟化设置,并将异常情况捕获到EL2。 | 2 |

| MAIR_ELn | 存储器属性间接寄存器 | 在ELn的阶段1翻译的Long-descriptor格式转换表项中,提供对应于可能值的存储器属性编码。 | 1,2,3 |

| MIDR_ELn | 主ID寄存器 | 代码运行的处理器类型(部件号和版本)。 | 1 |

| MPIDR_ELn | 多处理器密切关系的寄存器 | 处理器和群集ID,在多核或群集系统中。 | 1 |

| RVBAR_ELn | 基于地址寄存器的重置向量 | 保存重置向量的基地址,以便发送给ELn的任何异常。 | 1,2,3 |

| SCR_ELn | 安全配置寄存器 | 控制安全状态和EL3的异常情况。 | 3 |

| SCTLR_ELn | 系统控制寄存器 | 控制架构功能,例如MMU,缓存和对齐检查。 | 0,1,2,3 |

| SPSR_ELn | 保存的程序状态寄存器 | 当发生异常时,保持已保存的处理器状态。 | abt,fiq,irq,und,1,2,3 |

| TCR_ELn | 转换控制寄存器 | 确定哪个转换表基地寄存器定义了转换表行走(translation table walk)的基地址,该基地址是ELn中,内存访问阶段1转换所需要的。还控制转换表格式并保存可缓存和可共享的信息。 | 1,2,3 |

| TPIDR_ELn | 用户读/写线程ID寄存器 | 为了操作系统管理的目的,提供一个在ELn上执行的软件可以存储线程标识信息的位置。 | 0,1,2,3 |

| TPIDRRO_ELn | 用户只读线程ID寄存器 | 提供在EL1或更高版本上执行的软件可以存储线程标识信息的位置。为了操作系统管理的目的,在EL0上执行的软件可以看到这些信息。 | 0 |

| TTBR0_ELn | 转换表基址寄存器0 | 保存转换表0的基地址,以及它占用的内存的信息。这是ELn内,内存访问阶段1转换的转换表之一。 | 1,2,3 |

| TTBR1_ELn | 转换表基址寄存器1 | 保存转换表1的基地址,以及它占据的存储器的信息。这是在EL0和EL1内,内存访问阶段1转换的转换表之一 | 1 |

| VBAR_ELn | 基于向量的地址寄存器 | 保存异常基地址,以便发送到ELn的任何异常 | 1,2,3 |

| VTCR_ELn | 虚拟化转换控制寄存器 | 控制来自非安全EL0和EL1的内存访问阶段2转换所需的转换表步行。还保存访问的可缓存和可共享信息。 | 2 |

| VTTBR_ELn | 虚拟化转换表基址寄存器 | 保存来自非安全EL0和EL1的内存访问阶段2转换的转换表的基地址。 | 2 |

2.5 其他寄存器(如sctlR)

系统控制寄存器(SCTLR)是一个用来控制标准内存、配置系统能力、提高处理器核状态信息的寄存器。

并不是所有bit在EL1都可用,各bit的含义如下:

- UCI设置此位后,在AArch64中为DCCVAU、DCCIVAC、DCCVAC和ICIVAU指令启用ELO访问,

- EE 异常字节顺序:0 小端;1大端

- EOE ELO显式数据访问的字节序:0 小端;1 大端

- WXN 写权限不可执行nTWE不陷入WFE,此标志为1表示WFE作为普通指令执行

- nTWI不陷入WFI,此标志为1表示WFI作为普通指令执行

- UCT 此标志为1时,开启AArch64的EL0下访问CTR_ELO存器

- DNE ELO 下访问 DC AVA指令,0 禁止执行,1 允许执行

- I开启指令缓存,这是在EL0和EL1下的指令缓存的启用位。对可缓存的正常内存的指令访问被缓存。

- UMA 用户屏蔽访问。当EL0使用AArch64,控制从EL0的中断屏蔽访问。

- SED 禁止SETEND。在ELO使用AArch32禁ISETEND指令。0 使能;1 禁止

- ITD 禁止IT指令:0 IT指令有效; 1IT指令被当作16位指令。仅另外16位指令或32位指令的头16位可以使用,这依赖于实现

- CP15BEN CP15 barrier使能。如果实现了,它是AArch32 CP15DMB,DSB和ISB barrier操作的使能位

- SAO ELO的栈对齐检查使能位

- SA栈对齐检查使能位

- C数据cache使能。EL0和EL1的数据访问使能位。对cacheable普通内存的数据访问都被缓存

- A 对齐检查使能位

- M 使能MMU

为访问SCTLR ELn,使用:

MRS <Xt>,SCTLR ELn // Read SCTLR ELn into xt

MSR SCTLR ELn,<Xt>//write xt to SCTLR ELn

3. A64指令集介绍

1、ISA :Instruction System ArchitectureA

- AArch64:指的是架构

- A64:指的是指令集

- arm64:指的是Linux Kernel中的aarch64体系

2、AArch64的指令集架构

3.1.指令集总结

![C#知识|账号管理系统-账号信息管理界面[2]:提交查询按钮事件的编写](https://i-blog.csdnimg.cn/direct/410ae9c50ef64a998f8839b927261964.gif)