实习日志与总结

日期:2024 年 7 月 10 日 星期三 姓名:XXX

一、实习日志

上午

9:00 - 9:30 按时到达工位,参加部门早会,了解了今天的实习任务和目标,即初步学习 FPGA 简介和 Verilog 基础语法知识。

9:30 - 10:30 阅读相关的技术文档和教材,对 FPGA(现场可编程门阵列)的基本概念和工作原理有了初步的认识。了解到 FPGA 是一种可以通过编程来实现特定逻辑功能的集成电路,具有灵活性高、开发周期短等优点,广泛应用于通信、图像处理、工业控制等领域。

10:30 - 12:00 观看了几个关于 FPGA 应用的视频案例,更加直观地感受了 FPGA 在实际项目中的作用和优势。同时,做了详细的笔记,记录了一些关键的知识点和疑问点。

中午

12:00 - 14:00 午餐和休息时间。

下午

14:30 - 15:30 开始学习 Verilog 基础语法知识。首先了解了 Verilog 的模块结构、端口声明、数据类型等基本概念。通过示例代码,理解了如何使用 Verilog 描述简单的逻辑电路,如与门、或门、非门等。

15:30 - 16:30 进行了一些简单的 Verilog 代码编写练习,实现了基本的逻辑运算和组合逻辑电路。在编写过程中,遇到了一些语法错误和逻辑错误,通过仔细检查代码和参考教材,逐步解决了问题。

16:30 - 17:00 与同事交流讨论,分享了自己在学习过程中的心得和体会,同时也向同事请教了一些疑惑的问题,得到了很多有用的建议和指导。

17:00 - 17:30 对今天学习的内容进行总结和整理,回顾了 FPGA 的概念和 Verilog 语法的重点知识,并对自己的学习效果进行了评估。

二、实习总结

通过今天一天的实习,我对 FPGA 和 Verilog 有了初步的了解和认识。 在学习 FPGA 简介的过程中,我明白了 FPGA 的灵活性和可重构性为数字电路设计带来了极大的便利,能够满足不同应用场景的需求。同时,也感受到了 FPGA 技术在现代电子系统中的重要地位和广阔的发展前景。 在学习 Verilog 基础语法知识时,我掌握了 Verilog 语言的基本结构和语法规则,能够编写简单的逻辑电路代码。但是,我也意识到自己在代码编写的规范性和逻辑思维的严谨性方面还有待提高。在今后的学习中,我将加强练习,不断提高自己的编程能力。 总的来说,今天的实习收获颇丰,为我后续深入学习 FPGA 技术和 Verilog 语言奠定了良好的基础。我将继续努力,不断提升自己的专业水平,为今后的工作做好充分的准备。

三、实习内容

1.FPGA简介

1.1 FPGA是什么

FPGA(全称:Field Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。FPGA是一种完成通用功能的可编程逻辑芯片,即可以对其进行编程实现某种逻辑处理功能。

在专用集成电路(ASIC)领域中,FPGA作为一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。同时FPGA可用于实现硬件灵活定制,能够高效地实现算法加速、数据处理,从而提高系统的性能。

| FPGA制造商 | FPGA的优势 |

| •Intel ( Altera) •AMD(Xilinx) •Lattice(莱迪思) •紫光同创 •771所 •772所 | •高密度集成以创建复杂的逻辑功能 •高性能、低成本 •许多可用的I/O标准和功能 •包含大量IP核,方便开发 •设计灵活、可重复编程 |

FPGA更偏向于硬件电路,是用来设计芯片的芯片(FPGA),通过硬件编程语言在FPGA芯片上自定义集成电路的过程;单片机偏向于软件,是在已有的固化电路的芯片(单片机)上设计开发,通过软件编程语言描述软件指令在硬件芯片上的执行。

1.2 FPGA应用领域和前景

FPGA应用领域——高速接口设计

FPGA拥有优秀的高速处理能力、多达成百上千的I/O引脚并且支持各种不同的电平标准,这就决定了它在高速接口领域必然有一席之地。比如FPGA在和PC通信时,可选择:ISA、PCI、PCI Express、USB、UART等多种接口。

传统做法是使用专用的接口芯片,而使用FPGA则可以把各种不同的接口逻辑放在FPGA 内部去实现,再配合存储器使用,能使高速接口数据的传输、处理变得更加得心应手。

FPGA座用领域——人工智能

传统计算架构已经无法支撑深度学习大规模并行计算需求。FPGA可以帮助人工智能(AI)系统架构师灵活设计,同时也支持差异化定制极具竞争力的深度学习硬件加速器。

例如自动驾驶系统需要用到多种传感器对行驶路线、红绿灯、路障和行驶速度等各种交通信号进行采集,同时需要对这些传感器进行驱动、信息融合处理,就可以使用 FPGA。

2.Verilog HDL介绍

2.1 硬件描述语言介绍

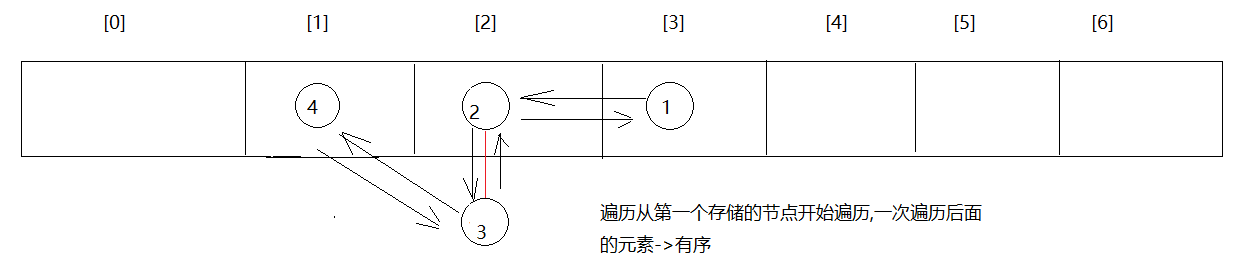

硬件描述语言(Hardware Description Language, HDL)是电子系统硬件行为描述、结构描述、数据流描述的语言。利用这种语言,数字电路系统的设计可以从顶层到底层(从抽象到具体)逐层描述设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设计自动化(EDA)工具进行仿真验证,再把其中需要变实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下来,再用专用集成电路(ASIC)或现场可编程门阵列(FPGA)自动布局布线工具,把网表转换要实现的具体电路布线结构.

硬件描述语言主要包括:Verilog、VHDL、System Verilog。

Verilog HDL: 拥有广泛的设计群体,成熟的资源也比 VHDL 丰富,从C编程语言中继承了多种操作符和结构,易于学习和理解。

VHDL: 超高速集成电路硬件描述语言是一种标准化程度较高的硬件描述语言,其具有语法严谨、结构规范、移植性强、数据类型丰富等特点。除此之外VHDL支持层次结构设计,独立于器件和设计平台,程序复用性强。

System Verilog: 结合了来自 Verilog、VHDL、C++的概念,将硬件描述语言与现代的高层级验证语言结合了起来。所以System Verilog有上述两种语言和计算机高级语言的特征。

2.2 Verilog模块基本结构

2.3 数值表示

2.3.1 四种数值

2.3.2 整数的数值表现方式