(1)ROM IP核简介:

ROM是只读存储器,是一种只能读出事先锁存的固态半导体存储器。其特性是一旦存储资料就无法再将之改变或删除,并且资料也不会因为电源关闭而消失。(掉电不丢失)

FPGA使用内部RAM实现ROM、RAM ip核的功能,Xilinx使用coe文件填充ROM和RAM。

(2)ROM的配置:

ROM关键词:block

PLL关键词:clk

- 配置单端口rom流程:

初始文件coe文件格式如下:

- 配置双端口rom流程:

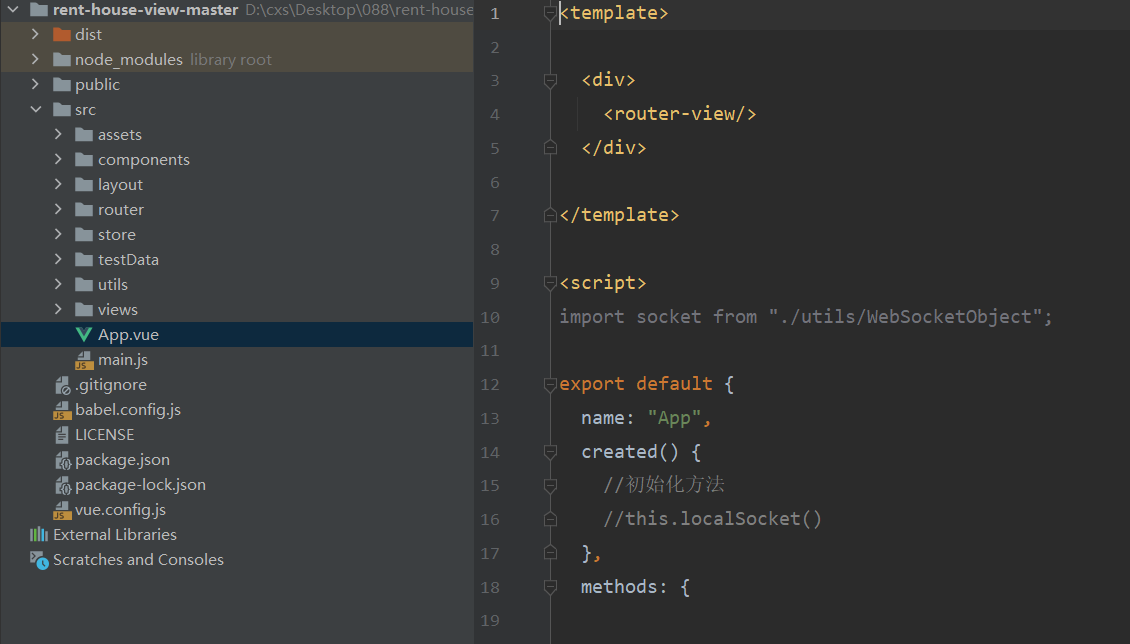

(3)ROM的调用:单端口ROM为例

module rom(clk,add,dout);

input clk;

input [7:0]add;

output [7:0]dout;

rom_8x256 rom_8x256_inst(

.clka(clk), // input wire clka

.addra(add), // input wire [7 : 0] addra

.douta(dout) // output wire [7 : 0] douta

);

endmodule(4)仿真文件代码:

`timescale 1ns / 1ps

module rom_tb;

reg clk ;

reg reset_n;

reg [7:0]add ;

wire [7:0]dout;

rom rom_inst(

.clk (clk ),

.add (add ),

.dout (dout)

);

initial clk = 1'b1;

always #10 clk = ~clk;

initial begin

reset_n <= 1'd0;

#15;

reset_n <= 1'd1;

#50000;

$stop;

end

always@(posedge clk or negedge reset_n)

if(!reset_n)

add <= 8'd0;

else if(add == 8'd255)

add <= 8'd0;

else

add <= add + 8'd1;

endmodule(5)仿真波形: