(1)Verilog代码:

module divider_n(clk,reset_n,clk_out);

input clk;

input reset_n;

output clk_out;

wire clk_out1;

wire clk_out2;

wire [9:0]n;

wire m;

assign n = 9;

assign m = n % 2;

divider_even divider_even_inst(

.clk(clk),

.reset_n(reset_n),

.n(n),

.en(!m),

.clk_out(clk_out1)

);

divider_odd divider_odd_inst(

.clk(clk),

.reset_n(reset_n),

.n(n),

.en(m),

.clk_out(clk_out2)

);

assign clk_out = m ? clk_out2 : clk_out1;

endmodule

module divider_even(clk,reset_n,n,en,clk_out);

input clk;

input reset_n;

input [9:0]n; //分频数

input en;

output reg clk_out;

reg [9:0]cnt;

wire [9:0]MCNT;

assign MCNT = (n >> 1) - 10'd1;

//计数器模块设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

cnt <= 10'd0;

else if ((cnt == MCNT)&&(en))

cnt <= 10'd0;

else if(en)

cnt <= cnt + 10'd1;

else

cnt <= 10'd0;

//clk_out信号设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

clk_out <= 1'd0;

else if (cnt == MCNT)

clk_out <= ~clk_out;

else

clk_out <= clk_out;

endmodule

module divider_odd(clk,reset_n,n,en,clk_out);

input clk;

input reset_n;

input [9:0]n; //分频数

input en;

output clk_out;

reg [9:0]cnt;

reg clk_1;

reg clk_2;

wire [9:0]MCNT;

wire [9:0]Mid;

assign MCNT = n - 10'd1;

assign Mid = (n >> 1);

//计数器模块设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

cnt <= 10'd0;

else if((cnt == MCNT)&&(en))

cnt <= 10'd0;

else if(en)

cnt <= cnt + 10'd1;

else

cnt <= 10'd0;

//clk_1信号设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

clk_1 <= 1'd0;

else if(cnt == Mid)

clk_1 <= 1'd1;

else if(cnt == MCNT)

clk_1 <= 1'd0;

else

clk_1 <= clk_1;

//clk_2信号设计

always@(negedge clk or negedge reset_n)

if(!reset_n)

clk_2 <= 1'd0;

else if(cnt == Mid)

clk_2 <= 1'd1;

else if(cnt == MCNT)

clk_2 <= 1'd0;

else

clk_2 <= clk_2;

assign clk_out = (clk_1 | clk_2);

endmodule

(2)代码层次:

(3)仿真代码:

`timescale 1ns / 1ps

module divider_n_tb;

reg clk;

reg reset_n;

wire clk_out;

divider_n divider_n_inst(

.clk(clk),

.reset_n(reset_n),

.clk_out(clk_out)

);

initial clk = 1'd1;

always #10 clk = ~clk;

initial begin

reset_n = 1'd0;

#15;

reset_n = 1'd1;

#2000

$stop;

end

endmodule

(4)仿真波形

(5)将顶层模块的n改成10,重新进行仿真

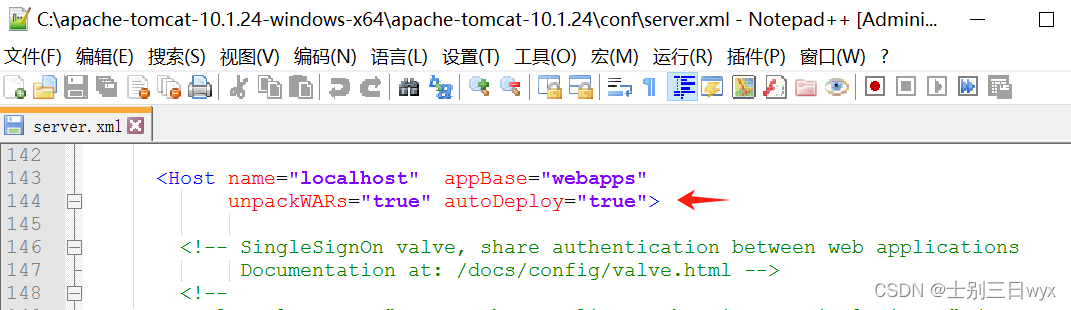

(6)引脚绑定:

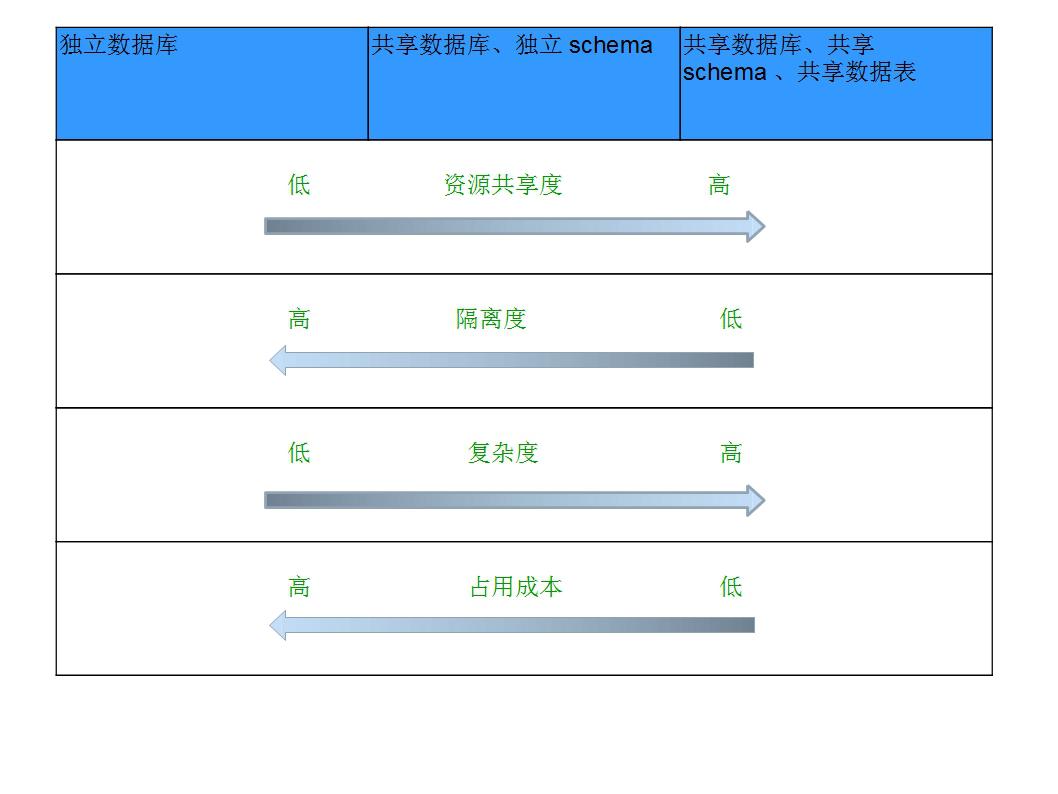

(7)以下分别是n=10和n=25时的示波器实验现象,时钟频率为50MHz

![[工具类]Java 合并、拆分PPT幻灯片](https://i-blog.csdnimg.cn/direct/9dd18249d2fe49a18698df3a32612b4d.png)