(1)设计一段代码,实现led灯在一秒内由完全熄灭到完全点亮,在第二秒由完全点亮转为完全熄灭,循环往复。

(2)Verilog代码:

module breath_led(clk,reset_n,led);

input clk;

input reset_n;

output led;

// 1 us = 1000 ns = 20ns *50;

reg [5:0] cnt_1us;

// 1 ms = 1000 us < 2 ^ 11 us

reg [9:0] cnt_1ms;

// 1s = 1000 ms < 2 ^ 11 ms

reg [9:0] cnt_1s;

reg overturn; //翻转信号

parameter MCNT_1us = 6'd49;

parameter MCNT_1ms = 10'd999;

parameter MCNT_1s = 10'd999;

//1us计数器模块设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

cnt_1us <= 6'd0;

else if(cnt_1us == MCNT_1us)

cnt_1us <= 6'd0;

else

cnt_1us <= cnt_1us + 6'd1;

//1ms计数器模块设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

cnt_1ms <= 10'd0;

else if((cnt_1ms == MCNT_1ms)&&(cnt_1us == MCNT_1us))

cnt_1ms <= 10'd0;

else if(cnt_1us == MCNT_1us)

cnt_1ms <= cnt_1ms + 10'd1;

else

cnt_1ms <= cnt_1ms;

//1s计数器模块设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

cnt_1s <= 10'd0;

else if((cnt_1s == MCNT_1s)&&(cnt_1ms == MCNT_1ms)&&(cnt_1us == MCNT_1us))

cnt_1s <= 10'd0;

else if((cnt_1ms == MCNT_1ms)&&(cnt_1us == MCNT_1us))

cnt_1s <= cnt_1s + 10'd1;

else

cnt_1s <= cnt_1s;

//翻转逻辑设计overturn

always@(posedge clk or negedge reset_n)

if(!reset_n)

overturn <= 1'd0;

else if((cnt_1s == MCNT_1s)&&(cnt_1ms == MCNT_1ms)&&(cnt_1us == MCNT_1us))

overturn <= ~overturn;

else

overturn <= overturn;

//led主程序设计

assign led = (((overturn == 0)&&(cnt_1ms <= cnt_1s)) ||((overturn == 1)&&(cnt_1ms <= MCNT_1s - cnt_1s)));

endmodule

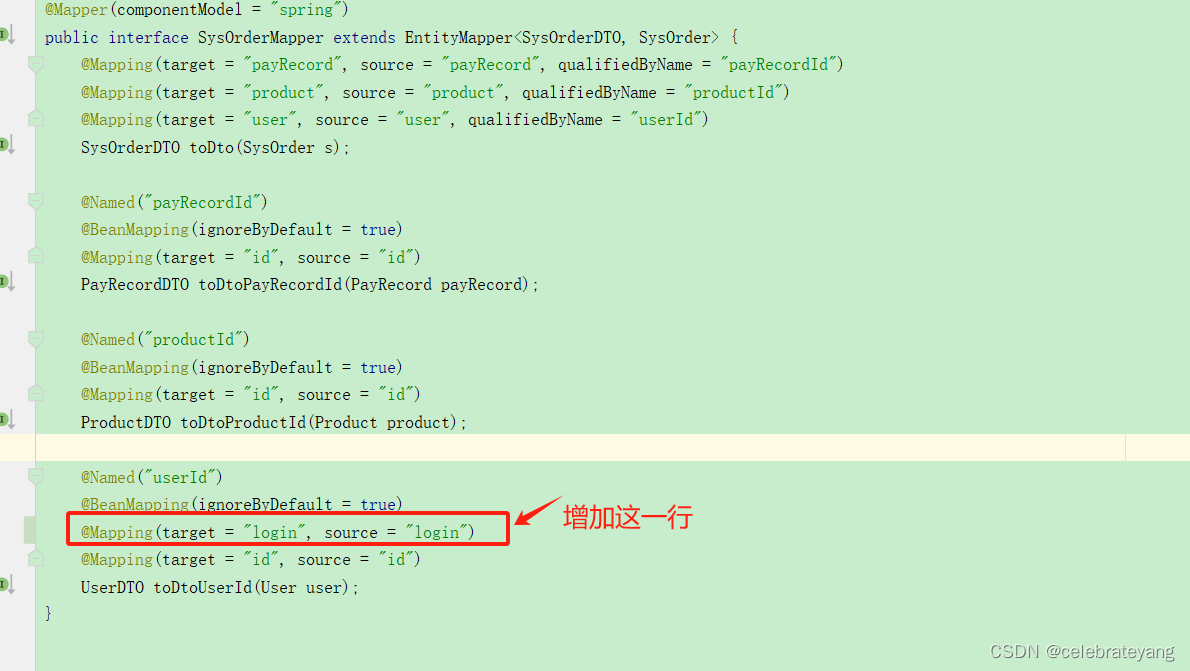

(3)仿真文件代码:

`timescale 1ns / 1ps

module breath_led_tb;

reg clk;

reg reset_n;

wire led;

breath_led breath_led_inst(

.clk(clk),

.reset_n(reset_n),

.led(led)

);

defparam breath_led_inst.MCNT_1us = 4;

defparam breath_led_inst.MCNT_1ms = 9;

defparam breath_led_inst.MCNT_1s = 9;

initial clk = 1'd1;

always #10 clk = ~clk;

initial begin

reset_n <= 1'd0;

#15;

reset_n <= 1'd1;

#50000;

$stop;

end

endmodule

(4)仿真波形:

(5)引脚绑定: