因最近想学习AGX orin和FPGA实现数据高速通信,借此机会和大家一起学习AGX orin和FPGA

制作不易,记得三连哦,给我动力,持续更新!!!

完整工程文件下载:AGX orin与FPGA实现PCIE完整工程 提取码:985w

在现代高速数据传输领域,PCIe(Peripheral Component Interconnect Express)已经成为了一种广泛应用的技术标准。它不仅提供了高带宽和低延迟的数据传输能力,还在多种应用场景中表现出色。本文将深入探讨如何利用NVIDIA的AGX ORIN平台与Xilinx的FPGA K7,通过PCIe接口实现高速数据通信。

AGX ORIN与FPGA A7的概述

AGX ORIN是NVIDIA最新一代的AI计算平台,具有强大的计算能力和广泛的应用前景,特别是在自动驾驶、机器人和高性能计算等领域。而Xilinx FPGA A7则是FPGA领域的一个重要产品,因其灵活的硬件配置和高效的数据处理能力,广泛应用于信号处理和嵌入式系统中。

本文将详细介绍如何使用他们,并提供具体的技术实现方案,包括:

- 硬件设计与配置:如何配置AGX ORIN和FPGA A7的硬件接口,使其能够通过PCIe进行高速数据通信。

- 驱动程序开发:开发并优化PCIe驱动程序,以支持高效的数据传输。

- 数据传输协议:设计高效的数据传输协议,确保数据传输的高效性和可靠。

一、硬件介绍

FPGA:

本次设计采用的是xilinx家的K7 325T(全称xc7k325tffg900-2L),采用我们自己设计的开发板进行开发,如果芯片一样的读者,也可以直接使用你自己的开发板来设计。下面是325T官方的PCIE资源介绍:

XC7K325TFFG900 的 PCIe 资源

-

内置 PCIe 硬核 (PCIe Hard IP)

- PCIe Gen2 支持: XC7K325TFFG900 支持 PCIe Gen2 标准,提供高达 5 GT/s 的数据传输速率。

- 支持的通道数: 支持 x1、x2、x4 和 x8 通道配置,根据应用需求灵活选择不同的带宽。

-

灵活的配置选项

- 可编程端点和根端口: 支持将 FPGA 配置为 PCIe 端点 (Endpoint) 或根端口 (Root Port),适用于不同的应用场景。

- 多功能支持: 允许实现多功能设备,使单个 PCIe 端点能够支持多个独立功能。

-

高性能 SerDes

- 高达 16 个高速串行解串行器 (SerDes) 通道: 每个通道支持高达 6.6 Gb/s 的数据传输速率,确保了 PCIe 通道的高性能传输能力。

- 集成时钟和数据恢复 (CDR) 电路: 提供稳定的高速数据传输,减少信号抖动和误码率

AGX ORIN:

本次设计的Orin为 JETSON AGX Orin 64G,同理32G的版本也是一样的,下面是总结的AGX Orin的PCIE资源介绍:

AGX Orin 的 PCIe 资源

-

PCIe 版本和速率

- PCIe Gen4 支持: AGX Orin 支持 PCIe 4.0 标准,提供高达 16 GT/s 的数据传输速率,比 PCIe 3.0 的带宽翻倍,适合高带宽需求的应用。

-

PCIe 通道数

- 多达 16 条 PCIe 通道: 允许配置为多种通道组合(如 x16、x8、x4、x2 和 x1),以满足不同设备和应用的带宽需求。

-

灵活的接口配置

- 多功能支持: 支持多种 PCIe 配置和设备树设计,灵活配置端点和根端口角色,适用于多种系统架构和应用需求。

- 多主机支持: 能够配置多个独立的 PCIe 控制器,使其可以同时连接多个 PCIe 设备,提升系统扩展性。

-

高性能和低延迟

- 高吞吐量和低延迟: PCIe 4.0 提供了高吞吐量和低延迟的特点,能够满足实时应用和数据密集型计算的需求。

- 内存访问: 支持直接内存访问 (DMA) 和远程直接内存访问 (RDMA),提高数据传输效率和系统性能。

二、FPGA设计

设计工具

设计开发vivado版本:vivado2019.2

设计语言:verilog、block design

设计需求:

完成 FPGA 与 AGX Orin 的数据交互,并通过 PCIe 接口实现高速数据传输,同时测量和评估通信速度及其性能表现。

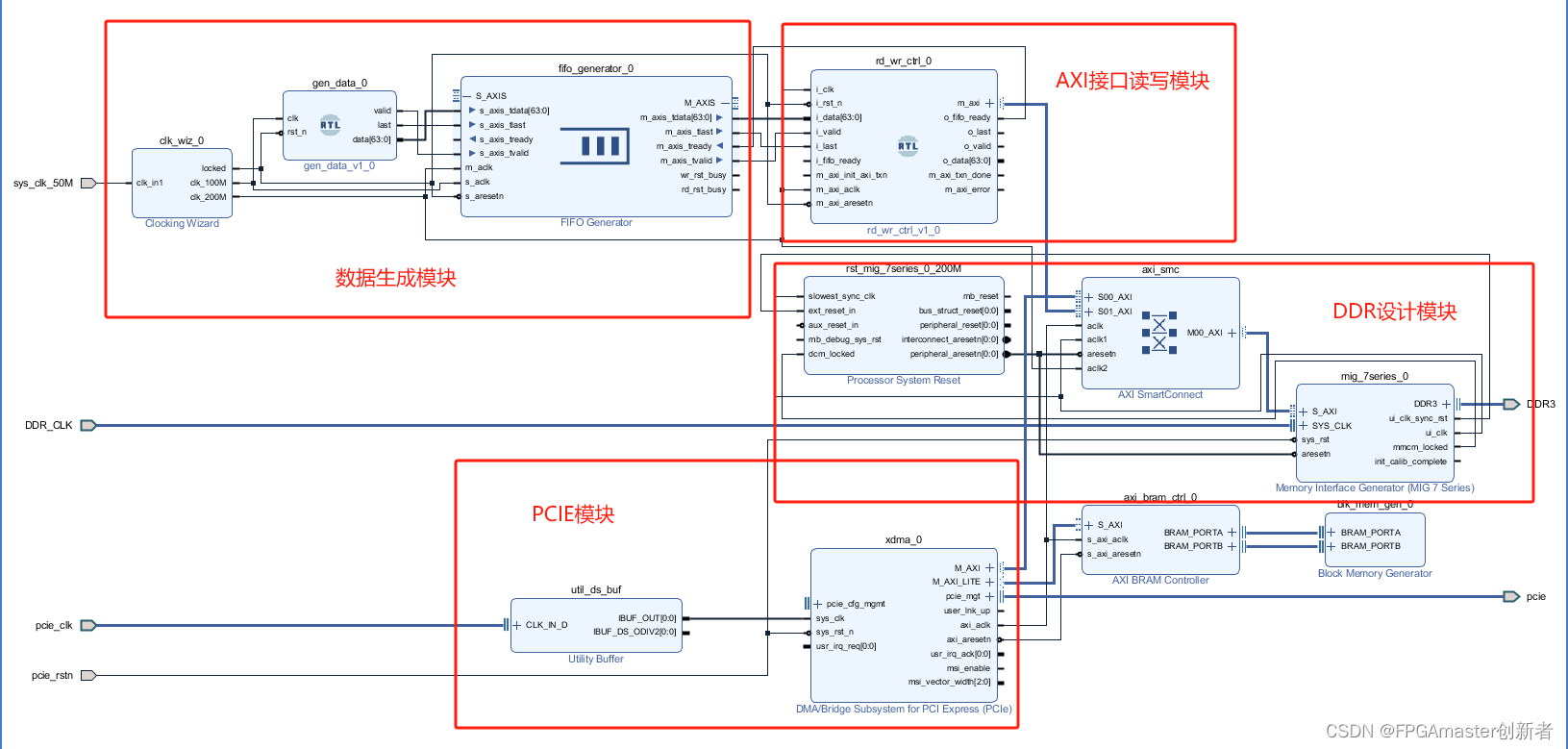

本设计主要是采用vivado中的block design设计,然后其中还添加了自己设计的一些代码:AXI接口读写模块和模拟数据产生模块。整体设计如下所示:

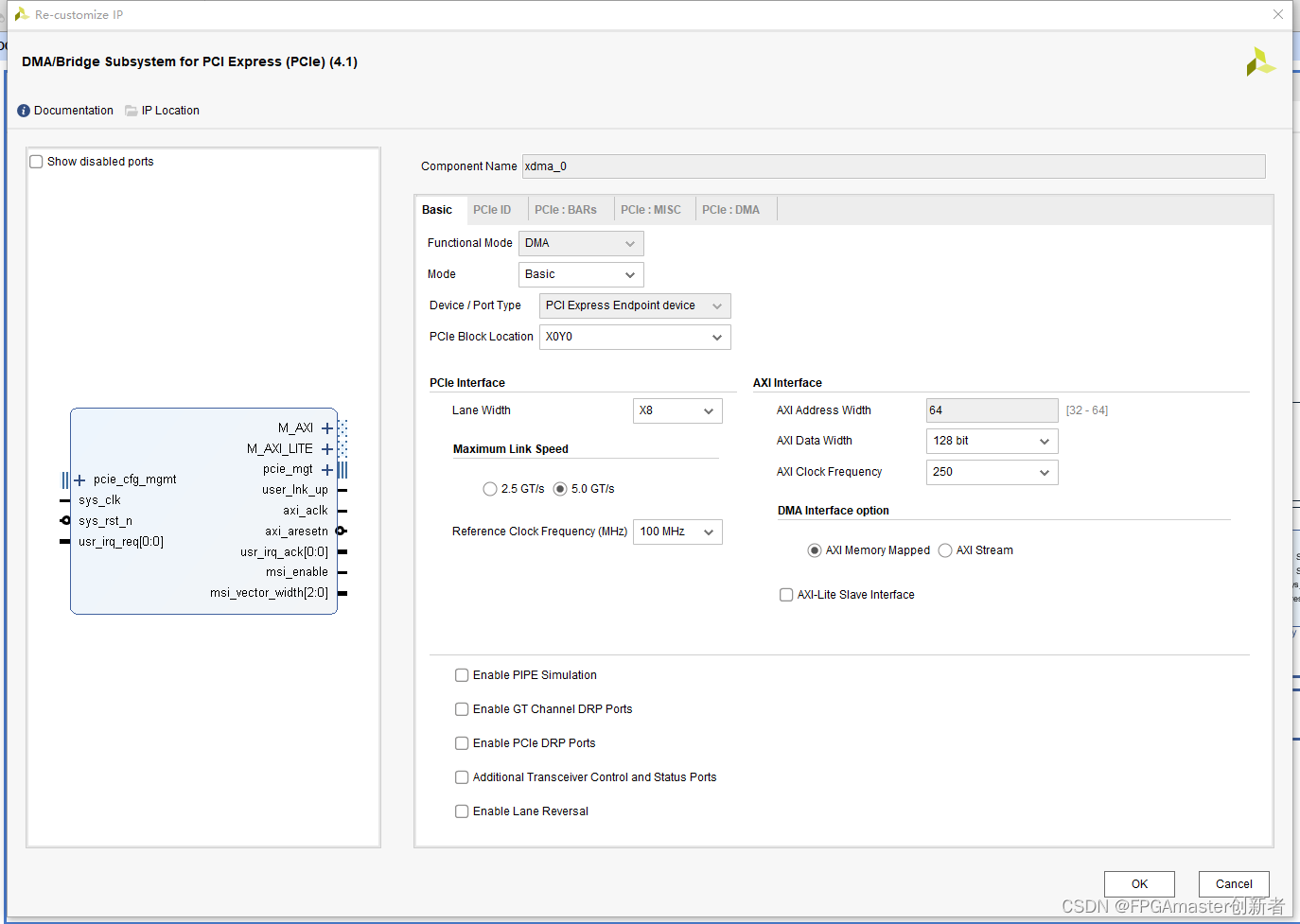

PCIE采用的是xilinx官方的XDMA IP:

主要配置为:PCIE 2.0 x8工作模式 (此芯片的最高配)

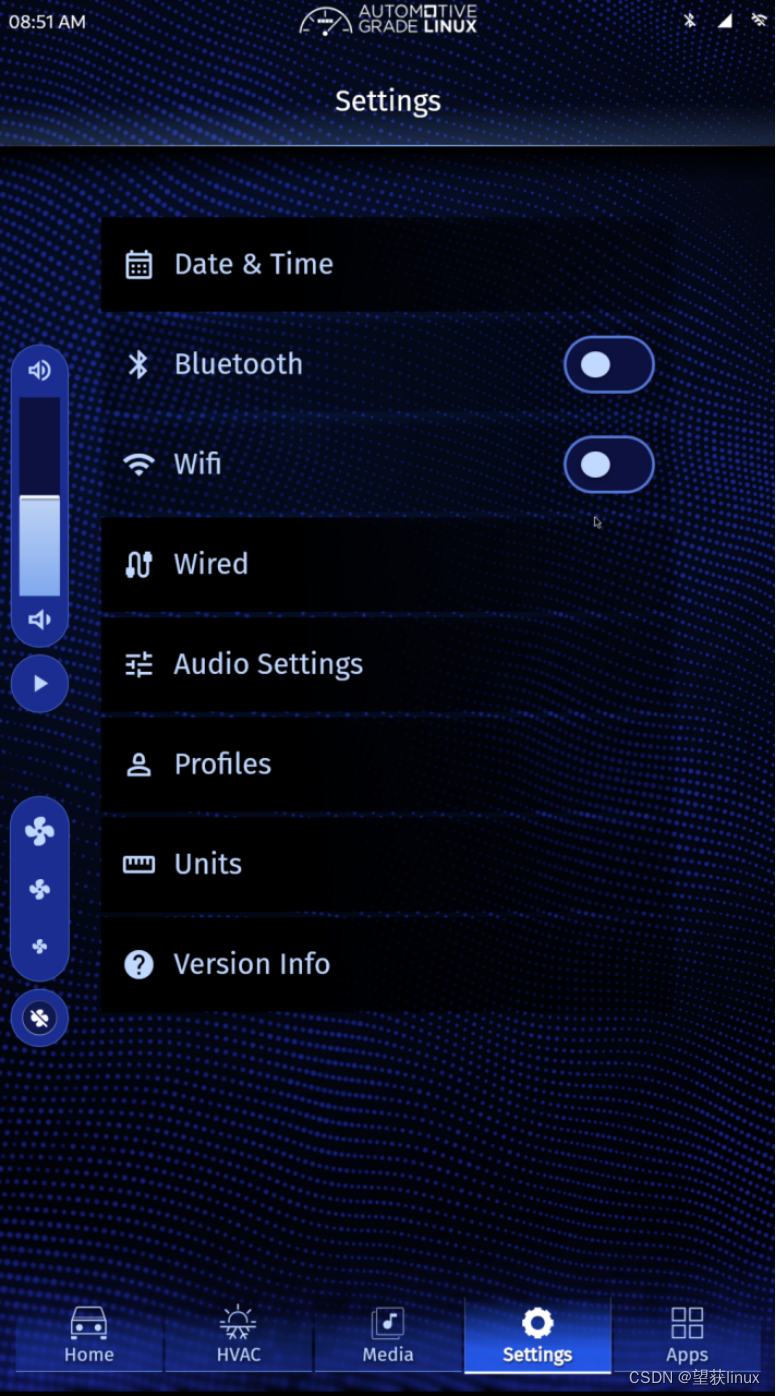

三、AGX Orin平台配置

开机:

首先拿到设备之后,根据官方的提示和步骤完成开机步骤,默认安装的ubuntu系统,开机之后就和正常的linux虚机没什么区别了

参考文献:AGX Orin官方开机测试指南

安装xdma驱动(linux版)

驱动下载

可以从官方下载驱动,也可以从我这里下载我使用的版本

官方驱动下载:GitHub - Xilinx/dma_ip_drivers: Xilinx QDMA IP Drivers

本设计使用的驱动:xdma_linux驱动下载

驱动安装

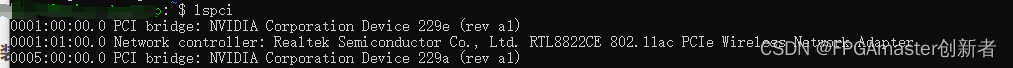

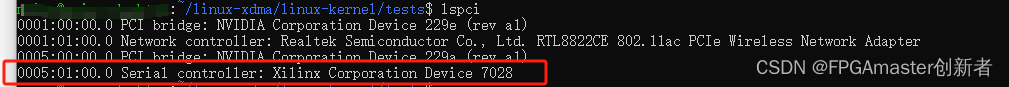

1、检查pci驱动

打开 Linux 终端,输入“lspci”命令并执行, 如下图所示:

可以看到,没有 Xilinx 相关的信息,这是因为没有安装 XDMA 的 Linux 系统驱动。

2、驱动安装

下载好的驱动,存放到AGX orin上面

由于提供的都是源码,需要编译安装然后才能使用。打开终端,输入如下命令:

cd ./dma_ip_drivers/XDMA/linux-kernel/xdma/

sudo apt install build-essential #(如果之前没有安装过 build-essential,需要安装)

sudo make install驱动安装完成后,重启 Linux 系统主机。

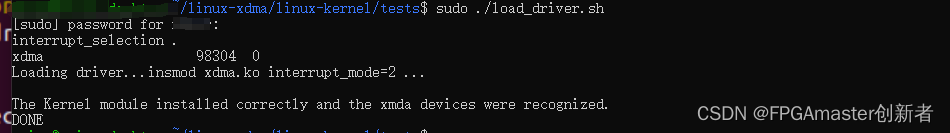

3、加载驱动

现在打开终端,输入如下命令进入 xdma 驱动目录下的 tests 目录:

cd ./dma_ip_drivers/XDMA/linux-kernel/tests该目录提供了驱动加载脚本及应用测试脚本,其中的 load_driver.sh 即为 XDMA 的驱动加载脚

本。执行该脚本前需要先给该脚本赋予可执行权限,然后以 root 身份执行,命令如下:

chmod +x load_driver.sh

sudo ./load_driver.sh

可以看到 XDMA 驱动已正确加载。

4、检测XDMA设备

在终端中输入“lspci”命令

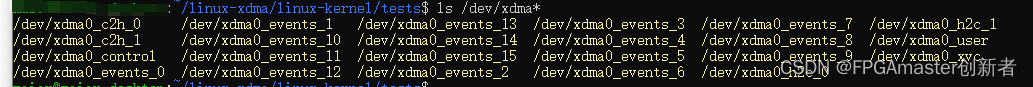

在终端中输入“ls /dev”命令并执行,可以在/dev 目录下看到以 xdma0 开头的设备文件,如下图所示:

以下是每个设备文件的简要说明:

/dev/xdma0_control:用于控制和配置DMA设备。/dev/xdma0_user:用于用户自定义用途。/dev/xdma0_xvc:用于虚拟JTAG功能。/dev/xdma0_events_*:用于处理DMA事件(中断)。/dev/xdma0_c2h_*:用于从卡到主机(Card to Host,简称C2H)的DMA数据传输。/dev/xdma0_h2c_*:用于从主机到卡(Host to Card,简称H2C)的DMA数据传输。

这表明 AGX orin系统已正确安装 XDMA 驱动并检测到了 XDMA 设备。

四、下板测试

把第三章的vivado工程生成的bit文件,烧录到FPGA开发板的FLASH,然后重启AGX orin

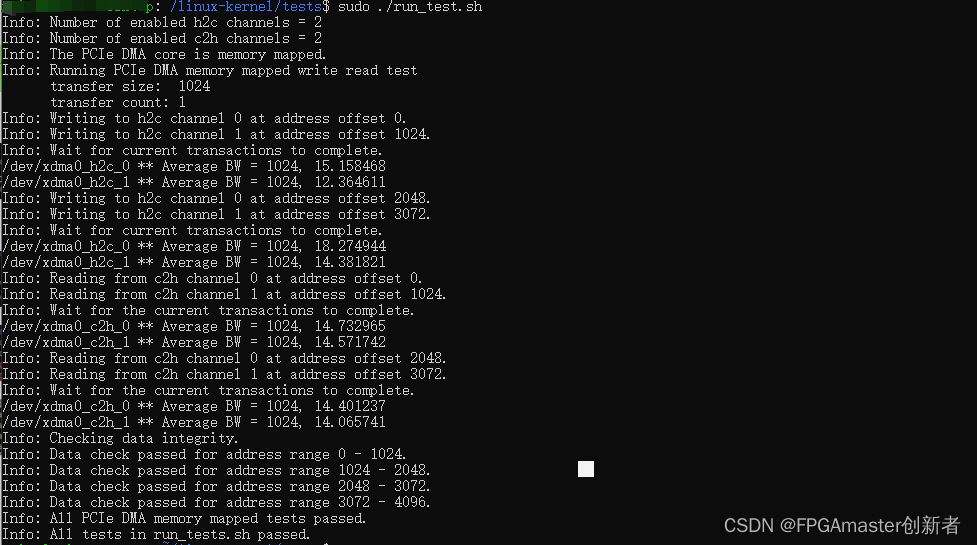

1、应用测试

打开终端,输入如下命令进入 xdma 目录下的tests 目录:

cd ./dma_ip_drivers/XDMA/linux-kernel/

cd tests/需要给他们添加可执行权限:

输入如下命令以执行 run_test.sh 脚本:

chmod +x run_test.sh

chmod +x dma_memory_mapped_test.sh

sudo ./run_test.shrun_test.sh 脚本用于测试基本的 XDMA 传输,并具有如下功能:

✓ 检测设计是基于 AXI-MM 接口还是 AXI_ST 接口,并查看启用了多少个通道;

✓ 对所有启用的通道进行基本传输测试;

✓ 检查数据完整性;

✓ 报告通过或失败

测试结果的最后两行 passed 表明我们搭建的基于 XDMA 的 PCIe 通信子系统正确,且 XDMA 驱动安装和驱动示例程序运行正常。

2、PCIE的读和写

Linux 的 XDMA 测试应用是源码提供的,需要先编译。打开终端,输入如下命令进入 xdma 目录下的tools 目录并编译:

cd ./dma_ip_drivers/XDMA/linux-kernel/

cd tools/

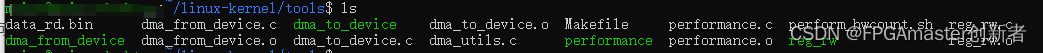

make编译后, tools 目录下有四个 XDMA 相关的测试应用,如下图所示:(第一次进来没有data_rd.bin文件)

dma_to_device

- 这是一个可执行文件,用于将数据从主机内存写入到 FPGA 设备。

dma_from_device

- 这是一个可执行文件,用于从 FPGA 设备读取数据到主机内存。

performance

- 这是一个可执行文件,可能用于测试和评估 DMA 性能

reg_rw

- 这是一个可执行文件,可能用于读取和写入 FPGA 寄存器

测试写入

打开终端,进入tools目录,然后输入以下指令(首先准备好一个测试数据datafile4K.bin):

sudo ./dma_to_device -d /dev/xdma0_h2c_0 -a 0x00000000 -s 2048 -f datafile4K.bin

这个命令将 data_to_write.bin 文件中的数据写入到 /dev/xdma0_h2c_0 设备的地址 0x00000000,长度为 2048 字节。

![]()

表示写入完成!!!

测试读取

打开终端,进入tools目录,然后输入以下指令

sudo ./dma_from_device -d /dev/xdma0_c2h_0 -a 0x00000000 -s 2048 -f data_rd.bin

这个命令从 /dev/xdma0_c2h_0 设备开始的地址 0x00000000 读取 2048 字节的数据,并保存到 data_rd.bin 文件中。

![]()

表示读取完成!!!

验证读写

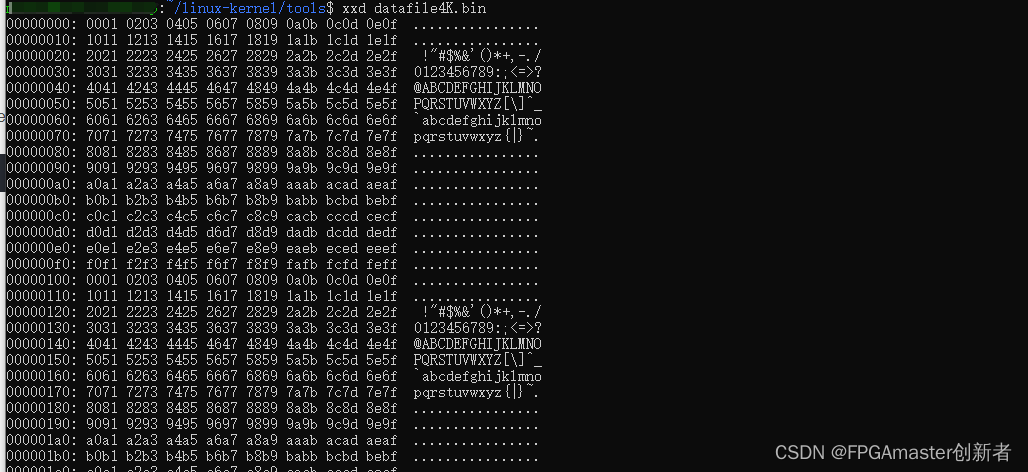

通过xxd命令来打开.bin文件:

首先打开写入的数据文件datafile4K.bin,输入以下指令

xxd datafile4K.bin

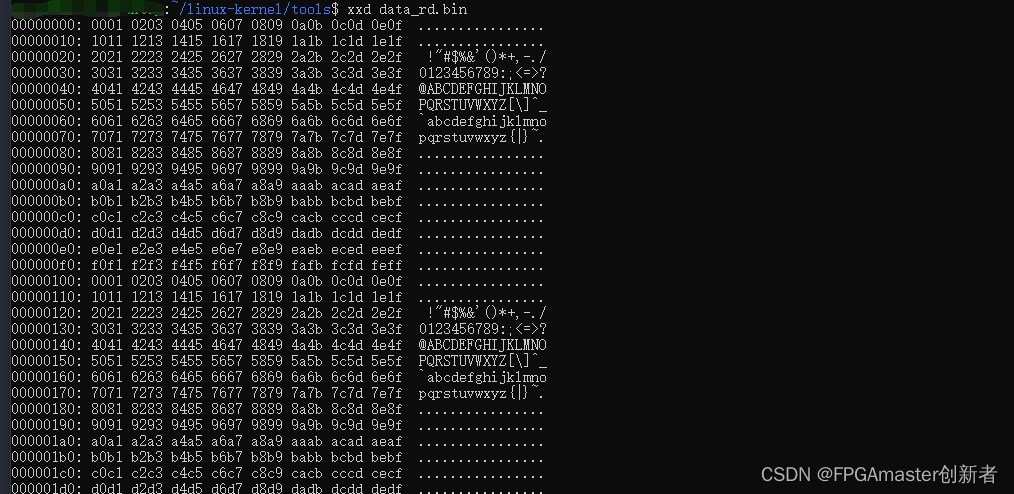

然后再读取从PCIE读取出来的数据data_rd.bin,输入以下指令

xxd data_rd.bin

可以看见写入数据和读出的数据一样

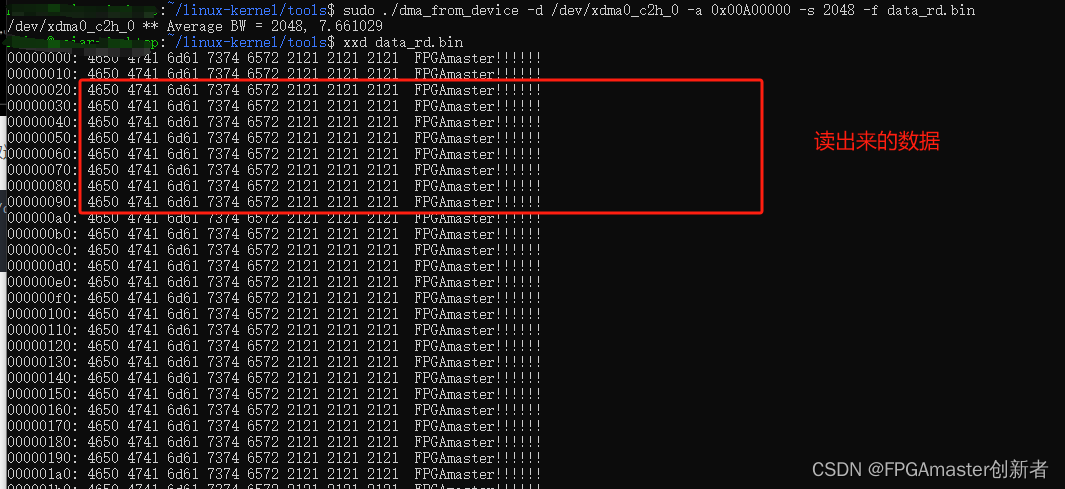

3、读取FPGA写入的数据

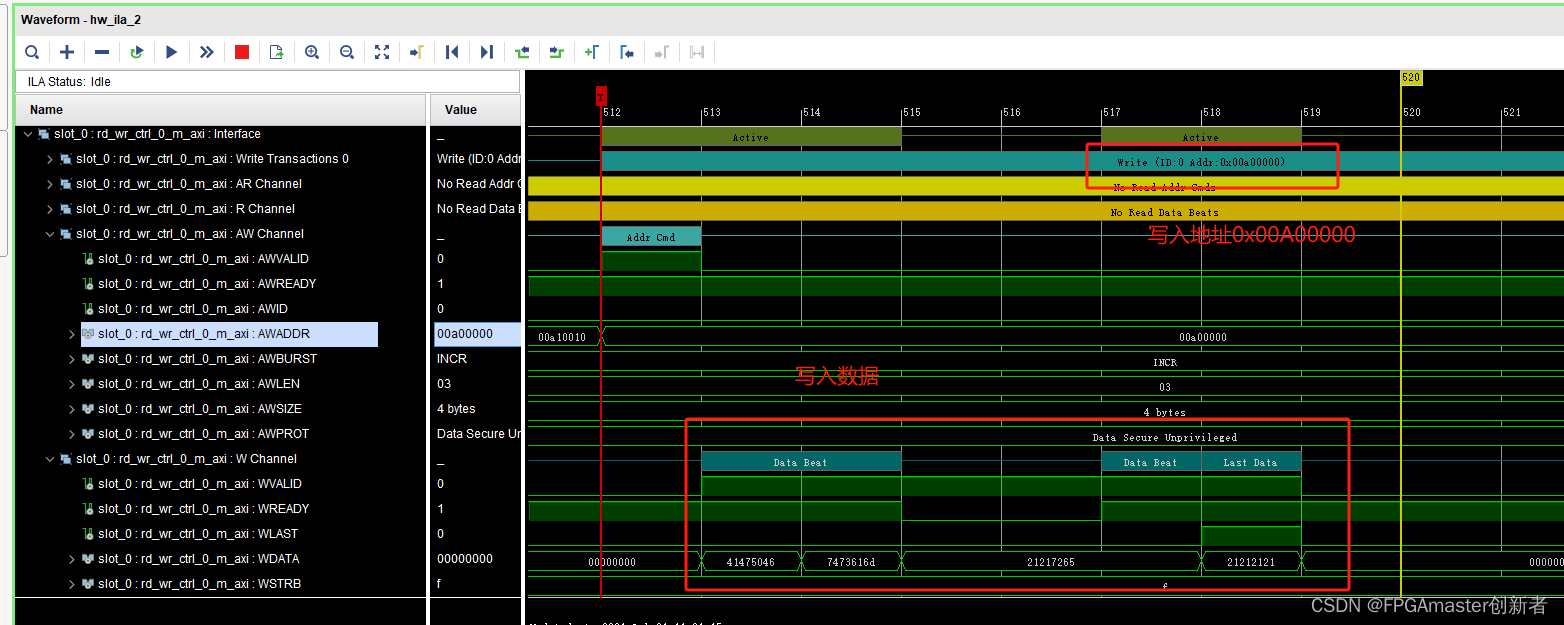

由第二章设计的FPGA工程可以得到,我们通过FPGA端向PCIE不停地写数据,我们先通过vivado的ila来查看写入的数据:

然后我们通过读取指令,来读取这个地址的数据,并通过xxd查看

sudo ./dma_from_device -d /dev/xdma0_c2h_0 -a 0x00A00000 -s 2048 -f data_rd.bin

xxd data_rd.bin

因大小端的问题,这个数据应该和ila的按字节取反即可

可见和ila抓的完全相同。说明FPGA写入,PCIE读取没问题!!!

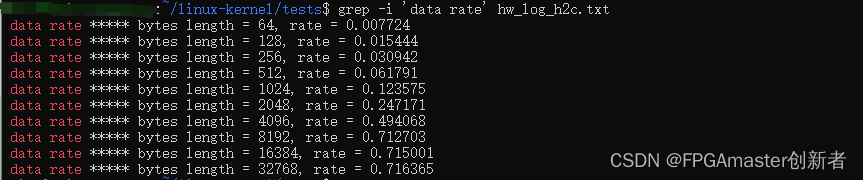

五、测试板卡速度

perform_hwcount.sh 脚本用于测试 XDMA 的硬件性能(读写速率),并将测试结果复制到hw_log_h2c.txt和 hw_log_c2h.txt 文本文件。 hw_log_h2c.txt 为写测试结果, hw_log_c2h.txt 为读测试结果。

打开终端,进入tests目录,然后输入以下指令

chmod +x perform_hwcount.sh

sudo ./perform_hwcount.sh 1 1参数 1 1 是指要测试的读写通道数。

然后输入以下命令查看写速度:

grep -i 'data rate' hw_log_h2c.txt

可以看到,对与写速率, 开始时传输长度越大,相应的传输速率 rate 也越大,当传输长度达到一定值时,对传输速率的影响就不大了。

由此可以验证本次设计整体没问题!!,终于大功告成啦!!!

完整工程文件下载:AGX orin与FPGA实现PCIE完整工程 提取码:985w

如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!

![[数据集][目标检测]护目镜检测数据集VOC+YOLO格式888张1类别](https://i-blog.csdnimg.cn/direct/d6080a535512487b9765fb484c64d538.png)