目录

描述

输入描述:

输出描述:

参考代码

描述

请用Moore型状态机实现序列“1101”从左至右的不重叠检测。

电路的接口如下图所示。当检测到“1101”,Y输出一个时钟周期的高电平脉冲。

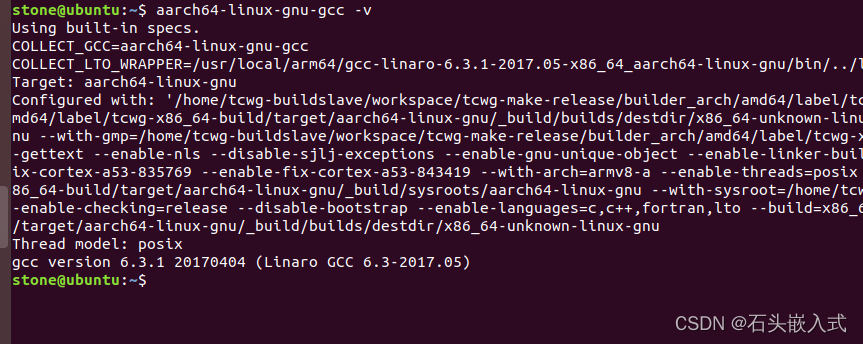

接口电路图如下:

输入描述:

input clk ,

input rst_n ,

input din ,

输出描述:

output reg Y

参考代码

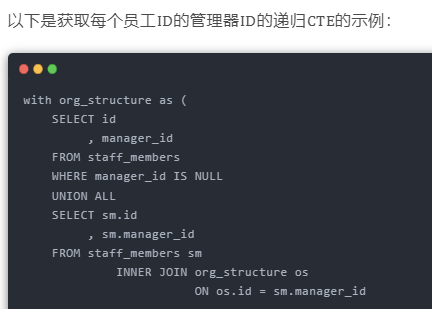

`timescale 1ns/1ns

module det_moore(

input clk ,

input rst_n ,

input din ,

output reg Y

);

reg [4:0] state, next_state;

parameter S0 = 5'b00001,

S1 = 5'b00010,

S2 = 5'b00100,

S3 = 5'b01000,

S4 = 5'b10000;

always@(posedge clk or negedge rst_n)

if(!rst_n)

state <= S0;

else

state <= next_state;

always@(*)

case(state)

S0: next_state <= din ? S1 : S0;

S1: next_state <= din ? S2 : S0;

S2: next_state <= ~din ? S3 : S2;

S3: next_state <= din ? S4 : S0;

S4: next_state <= din ? S1 : S0;

default: next_state <= S0;

endcase

always@(posedge clk or negedge rst_n)

if(!rst_n)

Y <= 1'b0;

else if(state == S4)

Y <= 1'b1;

else

Y <= 1'b0;

endmodule