计算机的底层逻辑很简单,它们被定义为完成一些简单的事情。计算机是一个复杂系统,复杂的是如何规划好处理这些简单的事情的时间和步骤。本节就可以了解到计算机的时间刻度和步进器的构成,帮助我们进一步理解计算机的底层工作原理。

时钟是什么?

上节我们介绍了要在适当的时间打开和关闭适当的控制位。本节我们就介绍一下合适的时间是怎么控制的。这是一种新的绘图,我们称之为图形。它显示了一个bit是如何随时间变换的。从左边开始,向右前进。图形上的线有两个可能的位置,向上表示位打开,向下表示位关闭。

![]()

该图显示了位“X”的开和关、开和关的规律。底部可能会有一个时间刻度来显示这种情况发生的速度。如果页面的整个宽度代表一秒,那么位“X”将每秒打开和关闭大约八次。但我们不需要这些图中的时间刻度,因为我们只关心两个或更多比特之间的相对时间。实际计算机的速度会非常快,比如每秒十亿次的bit开关操作。

当某物有规律地重复某个动作时,其中一个动作单独地被称为循环。上图显示了大约八个循环。 “circle”一词来源于’ Cycle’,根据规律,所以当bit变化了一个全周期时候,就是一个循环。德国科学家Heinrich Hertz(海因里希·赫兹)引导了无线电的发展,还研究了快速通断的电,所以人们决定用他的名字来描述电的开和关速度,或者每秒发生多少次循环。因此,一赫兹(或简称Hz)意味着电流每秒通断一次。500 Hz表示每秒500次,每秒一千次被称为千赫(kHz)。每秒上下一百万次称为兆赫(mHz),十亿次称为千兆赫兹(gHz)。

每台计算机都有一个特殊的比特。计算机中的所有其他位都来自某个地方,它们由其他位或开关设置。这一个特殊的位可以自行打开和关闭。但它并没有什么神秘之处,它只是非常有规律地、非常迅速地进行着。如下图,右边是更精简的版本。

![]()

本质上是一个非门组成,将非门的输出连接回其输入。这个门会尽可能快地打开和关闭。这实际上太快了,不能用于任何事情,所以只要延长形成环路的导线就可以减缓速度。

![]()

这个特殊的比特有一个名字:时钟。这有点不像我们平常见到的时钟,但作为计算机的计时单位,这是一致的。如果我们想谈论告诉你现在是什么时间的时钟类型,我们会称它为“一天中的时间钟”,简称“TOD clock”。

这个时钟开的有多快,如今,它的频率远远超过每秒十亿次,或几十亿赫兹。这是计算机公司告诉你的一个主要特征,用来向你展示他们的计算机有多棒。当你看到电脑在出售时,他们宣传的速度就是它的时钟速度。计算机速度越快,价格就越高,因为它可以在一秒钟内完成更多的事情。正是这一位的速度决定了整个计算机的节奏。

如何通过设置时钟获取寄存器数据呢?

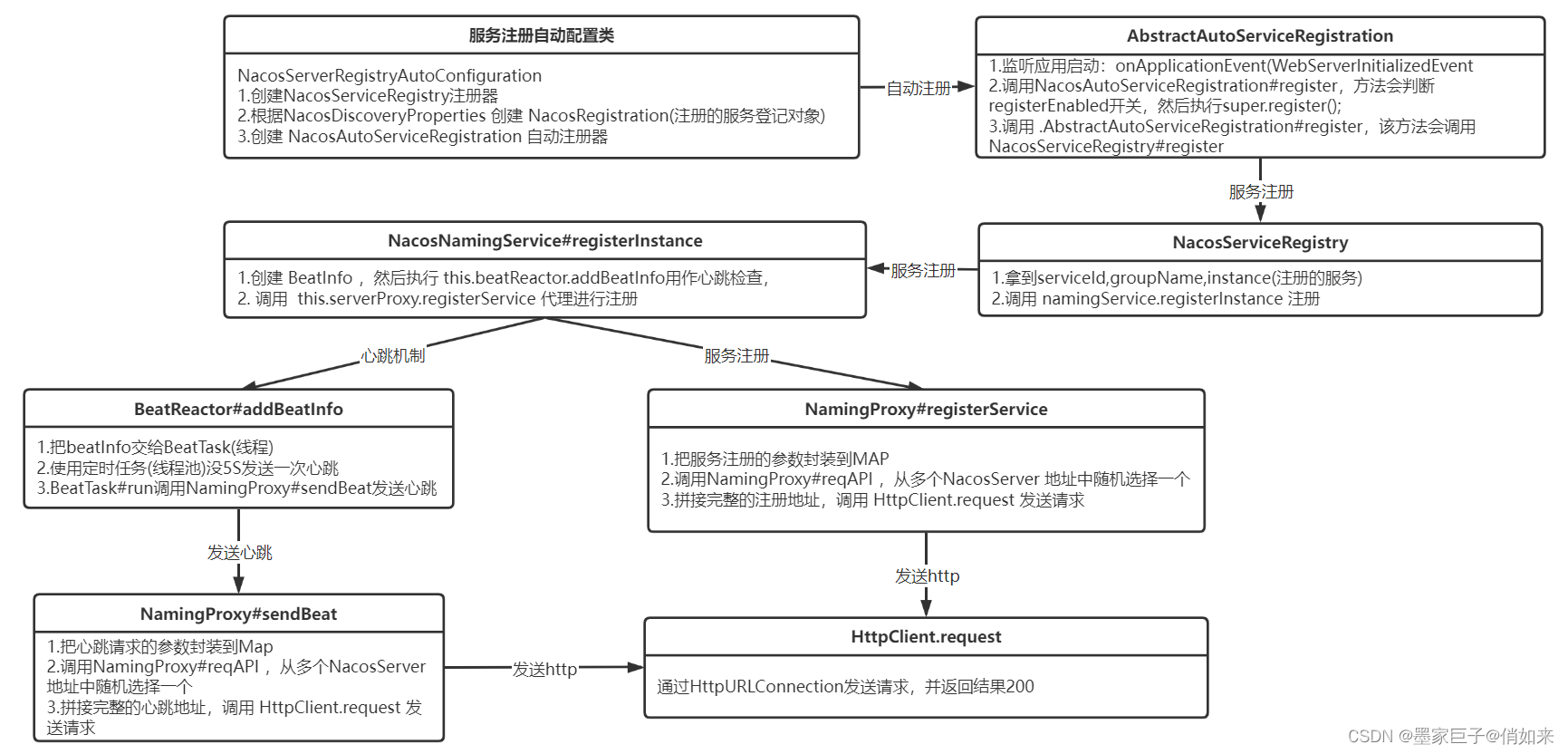

还记得我们之前介绍过的每个寄存器自带的一个set,enable两个状态位吗?要通过总线移动数据,我们首先需要启用一个且仅启用一个寄存器的输出,以便其电能通过总线传输到其他寄存器的输入。然后,当数据在总线上时,我们希望打开和关闭目标寄存器的设置位。由于目标寄存器在设置位关闭的瞬间捕获总线的状态,我们希望在关闭第一个寄存器的启用位之前确保它关闭,以确保没有问题.

让我们先将一段导线连接到时钟的输出端。这会稍微延迟供电。我们希望它延迟大约四分之一个周期.

![]()

如果我们在图上显示原始时钟输出(clk)和延迟时钟输出(clk d),它们将如下所示:

现在我们要做一些相当简单的事情。我们将使用原始时钟和延迟时钟,并使用and和OR来创建两个新bit,如下所示

当“clk”或“clk d”打开时,其中一个新bit打开,只有当“clk”和“clk d”都打开时,另一个新bit才打开。此处显示了与门和或门的输入和输出的图表。它们仍然定期开关,但其中一个打开的时间比关闭的时间长,另一个关闭的时间比打开的时间长。且第二个的打开时间正好在第一个的打开的时间中间。

你是否注意到,它们有名称“clk e”,代表时钟启用,“clk s”代表时钟设置。你知道吗,这两个bit有完美的时间通过总线将一个字节的数据从一个寄存器移动到另一个寄存器。只需将“clk e”连接到“from”寄存器的启用位,并将“clk-s”连接到到“to”寄存器的设置位。这是这两个位的单个开/关周期。

正是在这样的时钟周期里,把一个寄存器的数据传递到了另一个寄存器里。当然,这些时钟位不能直接连接到每个寄存器。在这两者之间必须有其他门,确保它们在任何时候都只允许一个寄存器获得使能,并且只允许所需的寄存器接收集合。但所有启用和设置最终都来自这两个bit,因为它们具有正确的时间。以后我们将使用以下图表来显示时钟:

步进器

如果我们想让计算机做一个加法,这需要一个以上的时钟周期才能完成。

- 在第二个循环中,我们可以在总线上启用R0,将ALU设置为ADD,并将答案设置为ACC。

- 在第三个循环中,我们可以在总线上启用ACC,并将其设置为R0。

- 在第一个时钟周期中,我们可以在总线上启用R1,并将其设置为TMP。

我们现在有R0的旧值,加上R0中的R1。也许这看起来不是很有用,但这就是计算机所做的一种小步骤。许多这样的小步骤使计算机看起来能够做非常复杂的事情。

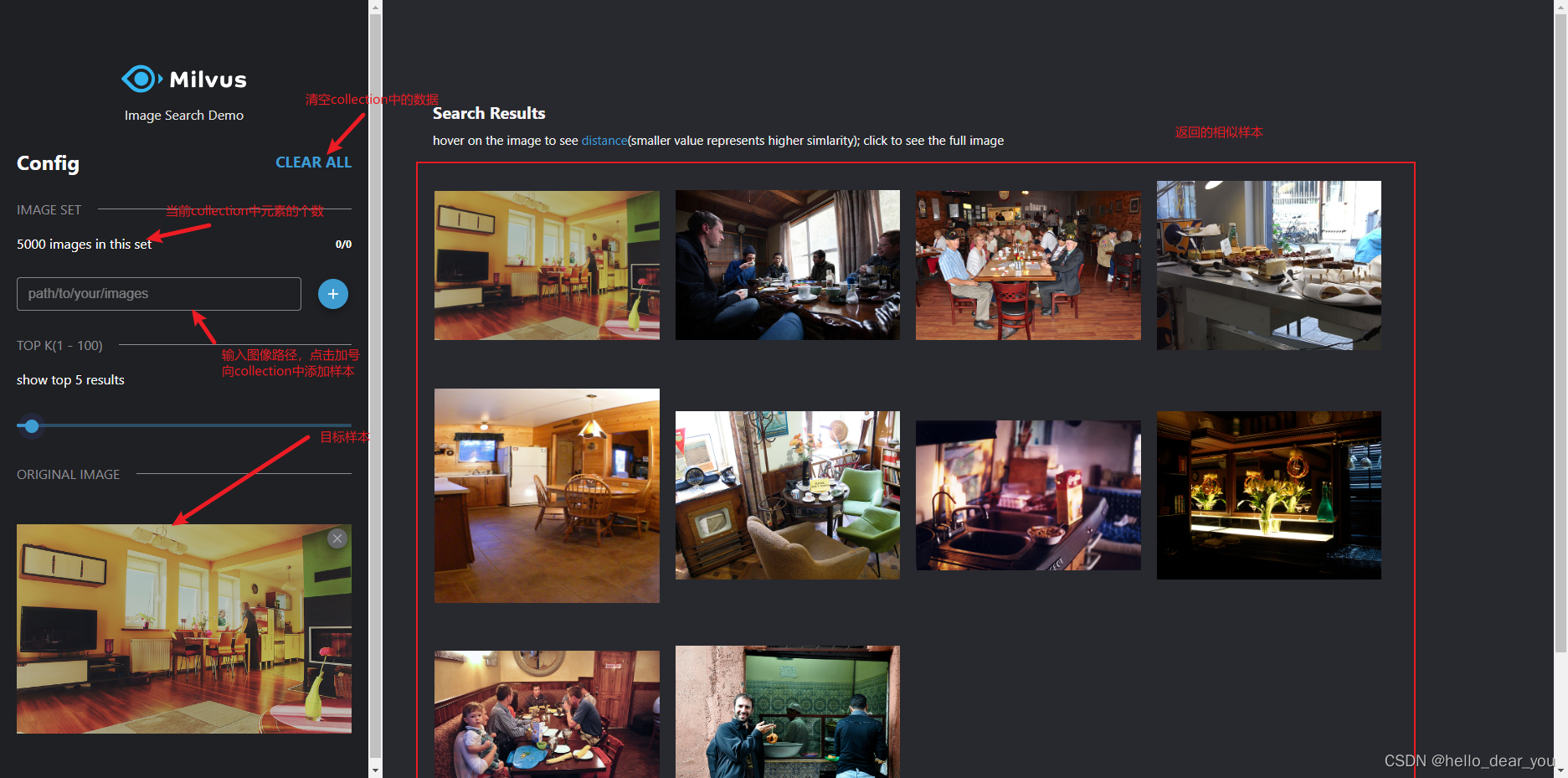

因此,我们看到处理器要做一些有用的事情,需要几个步骤。它需要能够按顺序执行操作。我们需要在“控制区”里添加另一个叫做“步进器”的部件。这是一个完整的步进器。

它有两个输入,其中一个被称为“clk”,因为这是连接一个开关位的地方,比如原来的时钟位。另一个输入被称为“复位”,用于将步进器返回到第一步。对于输出,它有许多位,每个位将在一个完整的时钟周期内打开,然后依次关闭。标有“步骤1”的输出在一个时钟周期内开启,然后在下一个时钟循环内开启“步骤2”,等等

可以构建为具有您想要执行的任何特定任务所需的任意步骤。就我们正在建造的这台计算机而言,七个步骤就足够了。当最后一个步骤(7)打开时,它保持打开,步进器不做任何其他事情,直到重置位被短暂打开,此时步骤从“步骤1”开始重新开始。这里是输入“clk”位和七步步进器输出的图表

这是步进器的构造。步进器由几个连接在一串的存储器位组成,其中一个的输出连接到下一个的输入。下面是一张图,显示了大部分步进器:

“M”就是Memory的意思,在这张图中,有十二个连接在一起,其中一个的输出端连接到下一个的输入端,一直沿着线路往下。左边第一位的输入连接到一个总是通电的地方,所以当“M”的set位接通时,“M”将接收该接通状态,并将其传递到其输出端。

仔细看这些M的设置位,你会发现偶数M的设置位连接到clk,奇数M的设定比特在经过非门后连接到同一个时钟。这个通过非门传递clk而产生的新比特可以称为“NOT clk”,我们可以在这个图上显示这两个比特

当“clk”首次打开时,什么都不会发生,因为第一个“M”的设置位连接到“not clk”,当“clk”打开时,“not clk”关闭。当“clk’关闭时,“not clk’打开,第一个“M”将打开,但第二个“M’不会发生任何事情,因为它的“设置”位连接到现在关闭的“clk‘。当“clk”重新打开时,第二个“M”现在将亮起。随着时钟的滴答声,进入第一个存储位的“on”将沿行递减,时钟打开运行一个bit,时钟关闭运行一个bit。因此,每个时钟周期有两bit作用。

现在,转到下面的全步进图,步骤1来自连接到第二个“M”的输出的非门,由于所有的“M”都开始了,步骤1将一直持续到第二个“M”开始,此时步骤1将结束。对于剩余的步骤,每个步骤将从其左侧“M”打开的时间一直持续到其右侧“M”开启的时间。当左侧“M’打开,右侧“M’关闭时,步骤2-6的“与”门的两个输入都打开。如果我们将一个“M”的输出和一个“M”的输出的“非”连接两个空格,它的输出将开启一个完整的时钟周期。每一个位在其左输入端开启时开启,但其右输入端尚未开启。这给了我们一系列位,每个位开启一个时钟周期,然后关闭。

这里唯一缺少的是“M”位开始并保持。一旦它们全部打开,尽管时钟继续滴答作响,但没有更多的动作。因此,我们需要一种方法将它们全部重置,以便重新开始。我们必须有一种方法来关闭第一个“M”的输入,然后同时打开所有设置位。当这种情况发生时,第一个“M”输入端的“off”将以最快的速度穿过所有“M”。我们将添加一个名为“重置”的新输入,它将完成这些任务。

当我们打开“重置”时,它会使第一个“M”位的输入为零,并同时打开所有“集合”,这样零可以很快地沿着“M”的线移动。复位也与步骤1进行“或”运算,以便步骤1立即打开。现在所有的位都关闭了,我们开始了另一个新序列。重置只需要在一个时钟周期的一小部分时间内打开

总而言之,这是一台步进器。它有两个输入:时钟和复位。对于输出,它有许多位,每个位将在一个时钟周期内开启。事实上,我们可以根据需要延长更多步骤,但就本书而言,七级步进机就足够了。我们的计算机中只有一个步进器,我们将用这个简化图来表示

我们将重置位重新定位到图的右侧,并将其连接到最后一步(7),以便步进器自动重置。然而,第7步不会持续很长时间,因为只要零能够通过M的字符串,它就会自动关闭。这意味着步骤7的持续时间不够长,无法用于总线上的数据传输。我们想要完成的所有事情都将在步骤1到6中完成。

![[附源码]计算机毕业设计JAVA基于JAVAWEB的高校实训管理系统](https://img-blog.csdnimg.cn/d29653e2c314477782ca7bb36b202557.png)