目录

- 从一个设计错误谈起

- Dropout压降

- 从芯片内部电路结构理解dropout压降

- MOS管 => 低dropout压降的LDO

- 进一步降低dropout压降的方法

在系统设计中,电源管理是不可或缺的,而LDO(线性稳压器)是电源管理器件中及其重要的一类器件。其应用电路简单,易于设计,得到了广泛地应用,但使用时有些技术要点应注意,避免设计上的漏洞,本文就dropout这一参数做一些介绍,从LDO内部电路结构出发,带您一起了解LDO的dropout压降。

从一个设计错误谈起

在某多电源的一个系统设计中,工程师希望得到一个4V的直流电压,为此采用了图1所示的电路:

电阻数值参见博文:《LM317 电阻表格 电阻计算》https://blog.csdn.net/mzldxf/article/details/103319162,然而实测输出端电压并不是4V而是3V多,电阻的数值也没有错都是对的,为什么输出电压不对呢?

Dropout压降

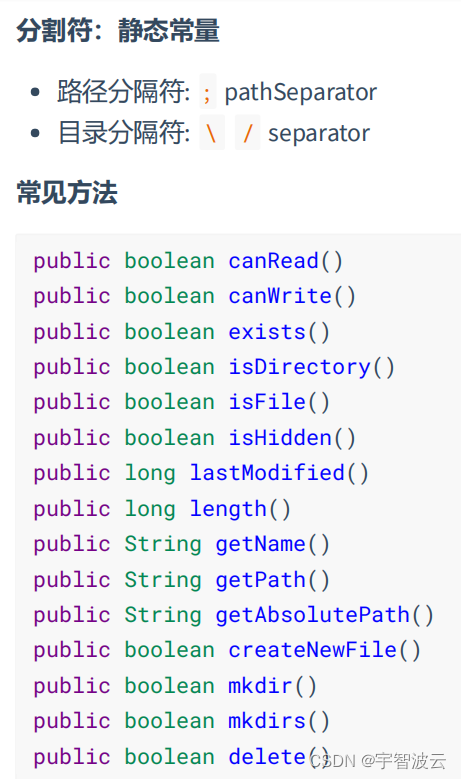

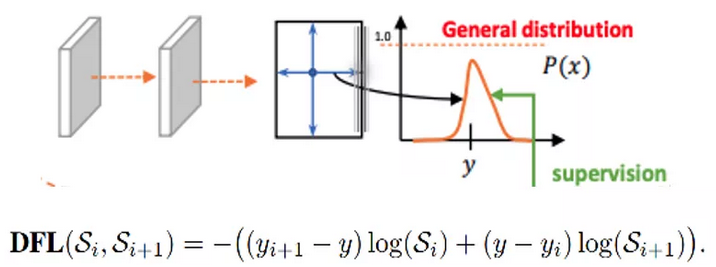

Dropout压降是LDO的一个重要指标,图2展示了LM317的dropout压降的数值:

从芯片内部电路结构理解dropout压降

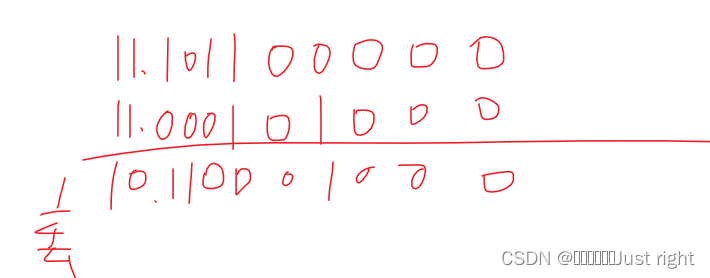

图3是LM317的内部电路结构,从图中可见,输入和输出隔了一个达林顿管和电阻,之所以要预留电压空间是因为达林顿管的集电极和发射极之间有压降,并且图中的电阻上也有压降。

电流乘以达林顿管的电阻Rce,再加上电流乘以电阻,就构成了LM317的dropout压降。

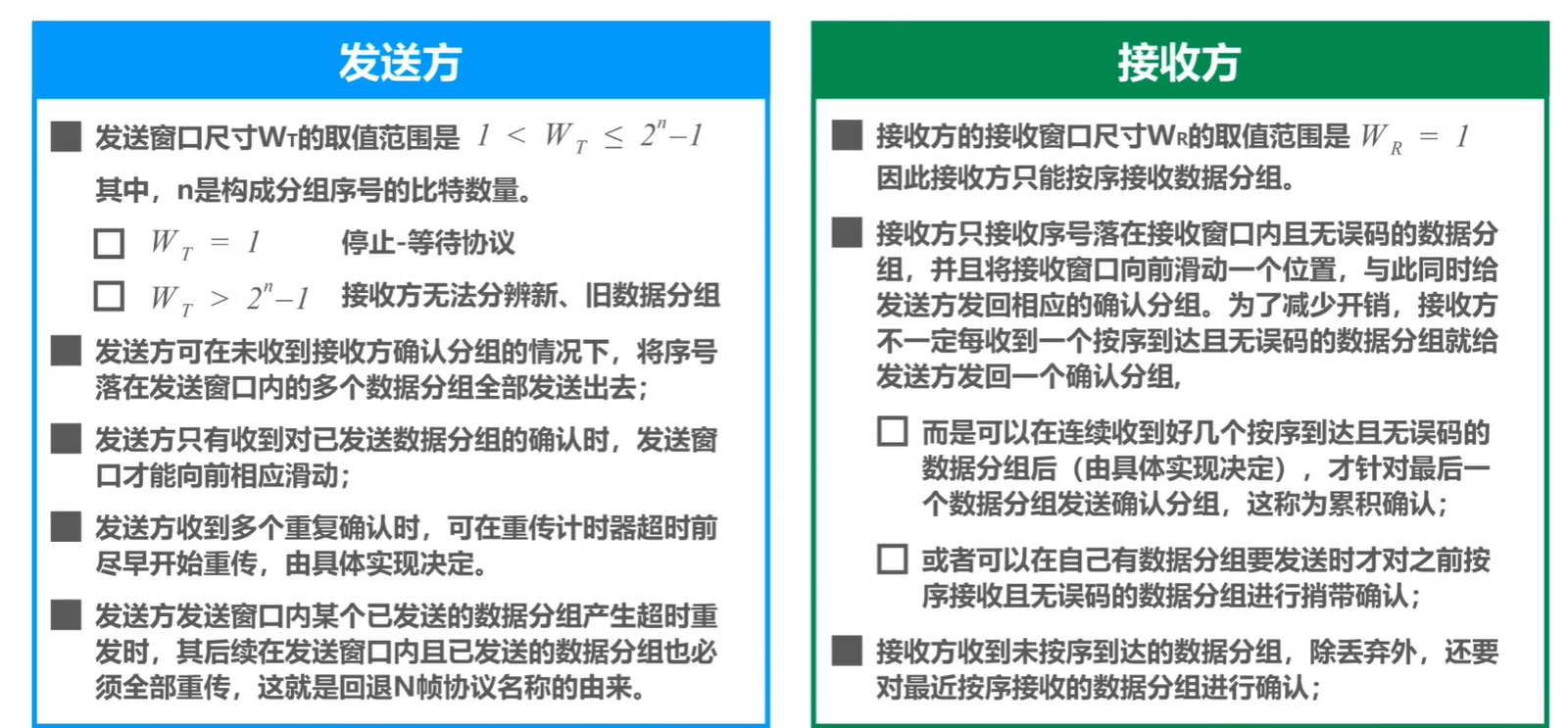

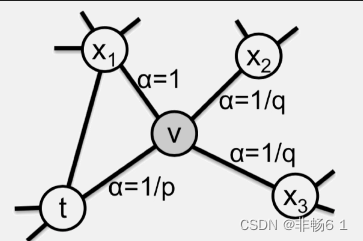

MOS管 => 低dropout压降的LDO

LM317属于比较早的LDO型号,现在的LDO的dropout压降并没有这么大了,可以做到200mV以内,之所以会做的比较小的一个原因是现在LDO采用了MOS管,如图4所示:

由于MOS管的Vds < 达林顿管的Vce,从而降低了dropout压降。另外,需要注意的是dropout压降和负载电流也有关系,大电流会导致dropout压降增大。

进一步降低dropout压降的方法

增加电路的复杂度,可以进一步地降低dropout压降,如图5所示,增加一个电压

V

B

I

A

S

V_{BIAS}

VBIAS,使NMOS的栅极电压可以高于输入电压,这样就可以增大Vgs从而减小Vds,即降低dropout压降。

作者:潇洒的电磁波(专业:射频芯片设计、雷达系统、嵌入式。欢迎大家项目合作交流。)

引用:

[1]:Texes instrument, LM317 datasheet

[2]:Texes instrument, LDO Basics

![vue老项目增加提交格式化功能[eslint+prettier+husky+lint-staged]](https://img-blog.csdnimg.cn/72865cbeb7f94ff0b43276a432a6baf1.png)