目录

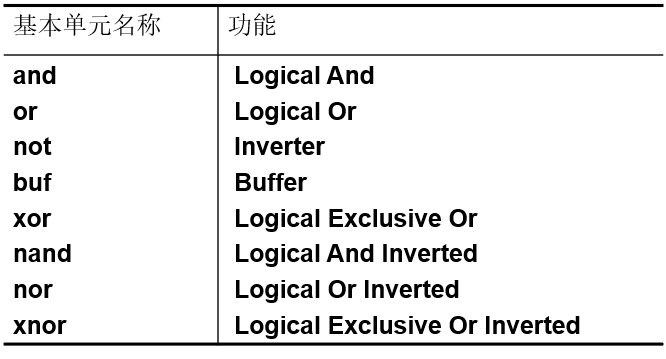

- 1.Verilog基本单元

- 2.基本单元的引脚 (pin)的可扩展性

- 3.带条件的基本单元

- 4.基本单元实例化

微信公众号获取更多FPGA相关源码:

1.Verilog基本单元

Verilog基本单元提供基本的逻辑功能,也就是说这些逻辑功能是预定义的,用户不需要再定义这些基本功能。

基本单元是Verilog开发库的一部分。大多数ASIC和FPGA元件库是用这些基本单元开发的。基本单元库是自下而上的设计方法的一部分。

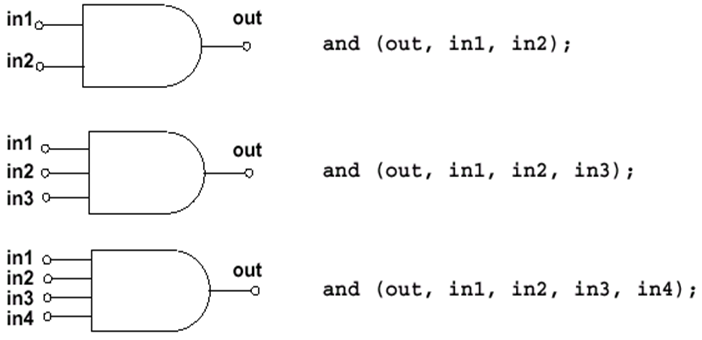

2.基本单元的引脚 (pin)的可扩展性

基本单元引脚的数目由连接到门上的net的数量决定。因此当基本单元输入或输出的数量变化时用户不需要重定义一个新的逻辑功能。

- 所有门(除了not和buf)可以有多个输入,但只能有一个输出。

- not和buf门可以有多个输出,但只能有一个输入。

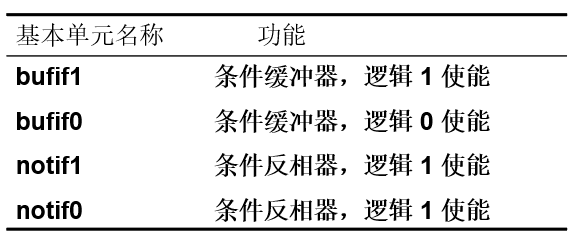

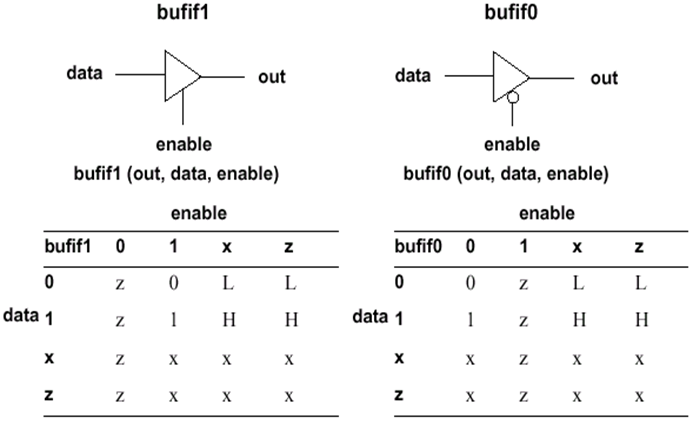

3.带条件的基本单元

- Verilog有四种不同类型的条件基本单元

- 这四种基本单元只能有三个引脚:output, input, enable

- 这些单元由enable引脚使能。

- 当条件基本单元使能信号无效时,输出高阻态。

条件基本单元有三个端口:输出、数据输入、使能输入

4.基本单元实例化

- 在端口列表中,先说明输出端口,然后是输入端口

- 实例化时实例的名字是可选项

and (out, in1, in2, in3, in4); // unnamed instance

buf b1 (out1, out2, in); // named instance

- 延时说明是可选项。所说明的延时是固有延时。输出信号经过所说明的延时才变化。没有说明时延时为0。

notif0 #3.1 n1 (out, in, cntrl); // delay specified

- 信号强度说明是可选项

not (strong1, weak0) n1 (inv, bit); // strength specified

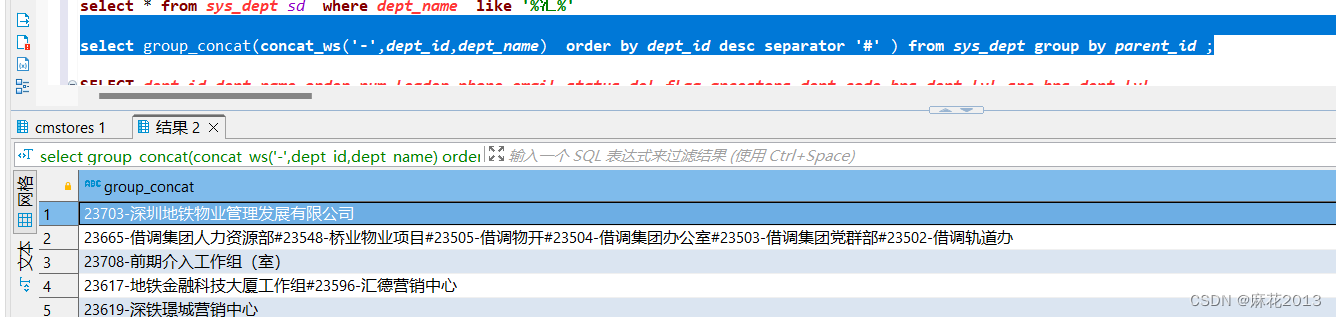

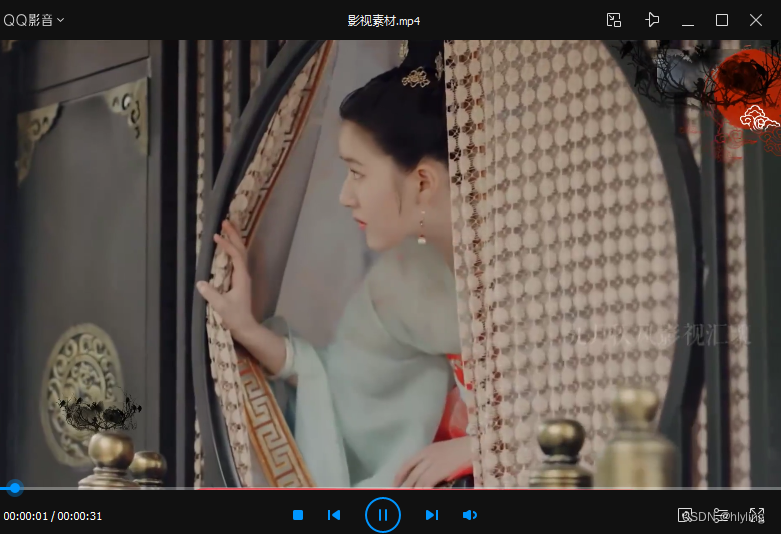

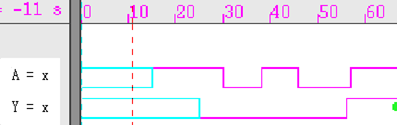

- 实例

module intr_sample;

reg A; wire Y;

not #10 intrinsic (Y, A);

initial begin

A = 0;

#15 A = 1; #15 A = 0; #8 A = 1;

#8 A = 0; #11 A = 1; #10 $finish;

end

endmodule

- 仿真波形

微信公众号获取更多FPGA相关源码: