文章目录

- 前言

- 1. AES加密原理

- 2.xilinx的AES方案

- 3.加密流程

- 3.1生成加密的bit流

- 3.2将密钥写入eFUSE寄存器

- 4.验证结论

- 5.传送门

前言

在FPGA的项目发布的时候需要考虑项目工程加密的问题,一方面防止自己的心血被盗,另一方面也保护公司资产,保护知识产权。Xilinx的器件大概有两种加密方案,一种是本文介绍的AES加密算法,另一种则是利用multiboot配置和Device DNA,其大概是流程是,xilinx提供了读取Device DNA的原语,用户逻辑通过原语读取Device DNA然后与用户逻辑的加密模块做运算得到一个数字串,将该数字串与存放在Flash特定区域的密文做对比,如果一致证明该FPGA通过授权可以启动用户逻辑,如果失败则可设置不启动。存放在Flash特定区域的密文也是通过Device DNA与用户逻辑中的加密算法提前计算得到的。因为Flash不仅要存储密文还要存储bit流,因此需要用到multiboot配置。Xilinx7系列支持AES256加密算法,可以防止程序回读和逆向,杜绝用抄板的方式窃取劳动成果。 本文介绍AES加密算法的原理,加密操作的流程以及加密的作用。

1. AES加密原理

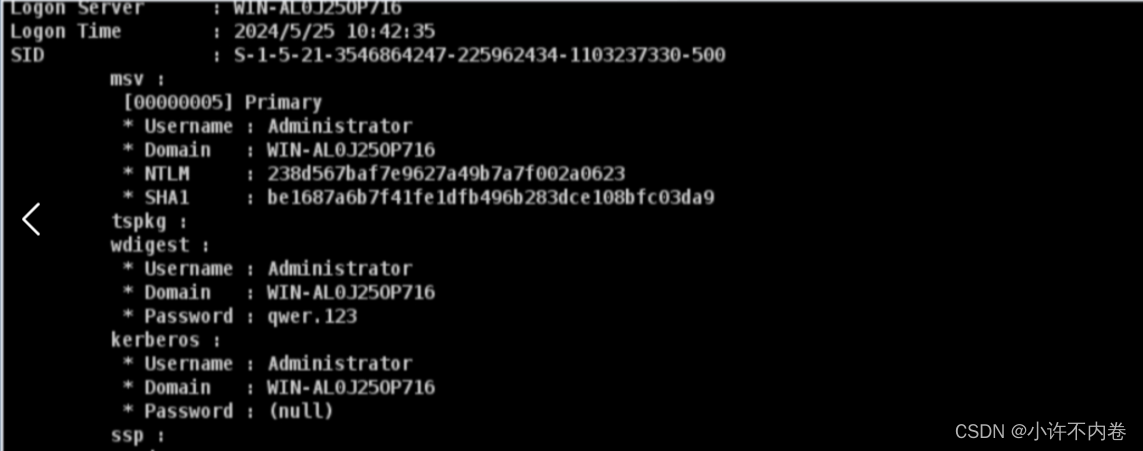

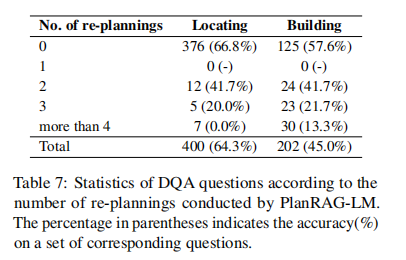

AES加密算法是一种对称加密算法,用于保证私密信息不被泄露,对称是指加密法和解密方使用的密钥是一致的。AES的Key支持三种长度:AES128,AES192,AES256 。xilinx采用AES256,使用密码块链接模式(Cipher Block Chaining mode,CBC mode)(AES有五种模式CBC是其中的一种)。 AES256的加密原理是把明文按照256bit拆分成若干个明文块,如果最后有数据不足256bit按照一定的方式来填充最后一个明文块。每一个明文块利用AES加密器和密钥,加密成密文块。拼接所有的密文块,成为最终的密文结果。从图中可以看出,CBC模式在每一个明文块加密前会让明文块和一个值先做异或操作。IV作为初始化变量,参与第一个明文块的异或,后续的每一个明文块和它前一个明文块所加密出的密文块相异或。由下图可以看到,实现AES256加密算法需要提供密钥、初始向量IV以及256bit-HMAC。HMAC是为了避免bit被篡改,HMAC(Hash-based Message Authentication Code,基于散列函数的消息认证码)是一种用于验证数据完整性和真实性的认证方法。它通过将数据与密钥进行散列处理,生成固定长度的认证码,然后将认证码与数据一起发送给接收方。接收方在接收到数据后使用相同的密钥和散列函数进行计算,然后比较生成的认证码是否一致,从而可以判断数据是否被篡改或伪造。HMAC认证可以有效防止数据在传输过程中被篡改或伪造,以确保数据的完整性和真实性。

2.xilinx的AES方案

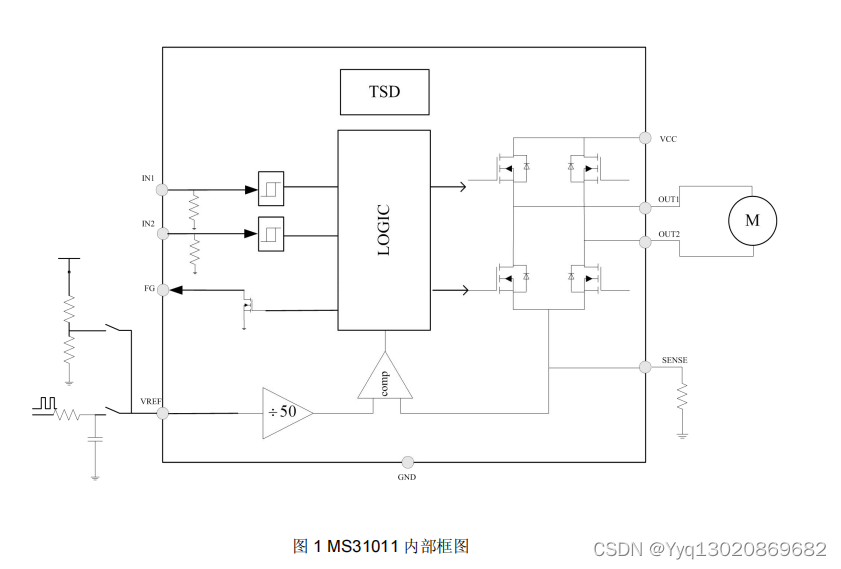

以上介绍的是AES加密算法本身的原理,xilinx是如何利用这个加密算法的呢?

Xilinx可通过JTAG接口将用户指定的密钥(或者软件生成的,这里包括上一节提到的三个密钥)写入eFUSE寄存器(采用熔断丝技术一生只能写一次,且写且珍惜~),同时Vivado工具负责根据用户指定的密钥对bit流进行 AES加密。FPGA在加载加密后的bit流时,会根据用户设置的密钥通过片上的 AES解密逻辑电路进行 AES解密,从而还原得到器件可以识别的未加密bit流,从而被正确加载。具体的操作流程见下一节。

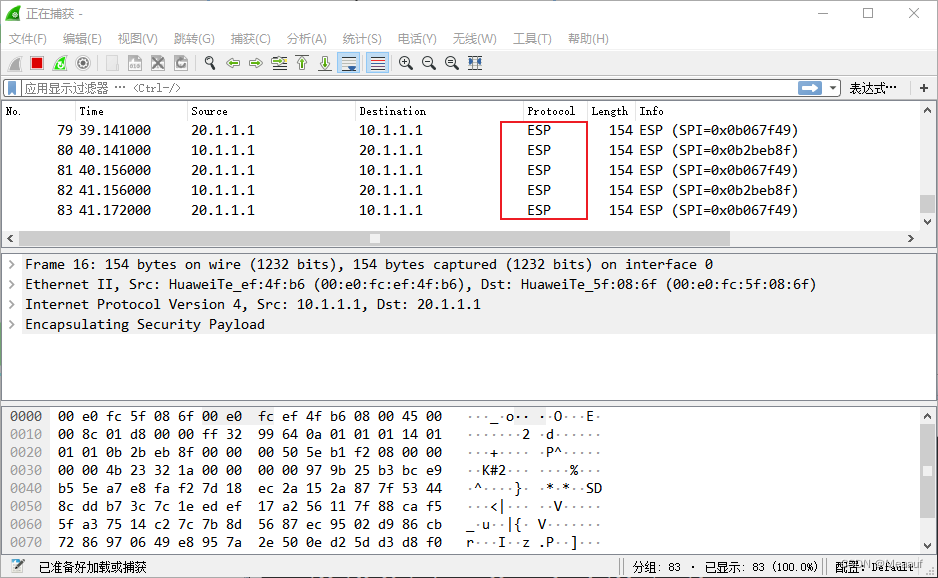

此外,Xilinx提供了几个寄存器配置选项,提供灵活的加密配置。如下图所示,7系列查看UG470,KU系列查看UG570,操作时按照下文推荐配置即可。需要注意eFUSE Control Register的CFG_AES_Only,如果该位被设置为1,则FPGA上电之后将强制进行解密操作,一旦bit流没有设置密钥或者密钥不正确,将不会被加载,因此一定慎用该寄存器,否则一旦密钥丢失,FPGA将变成废铁。

3.加密流程

3.1生成加密的bit流

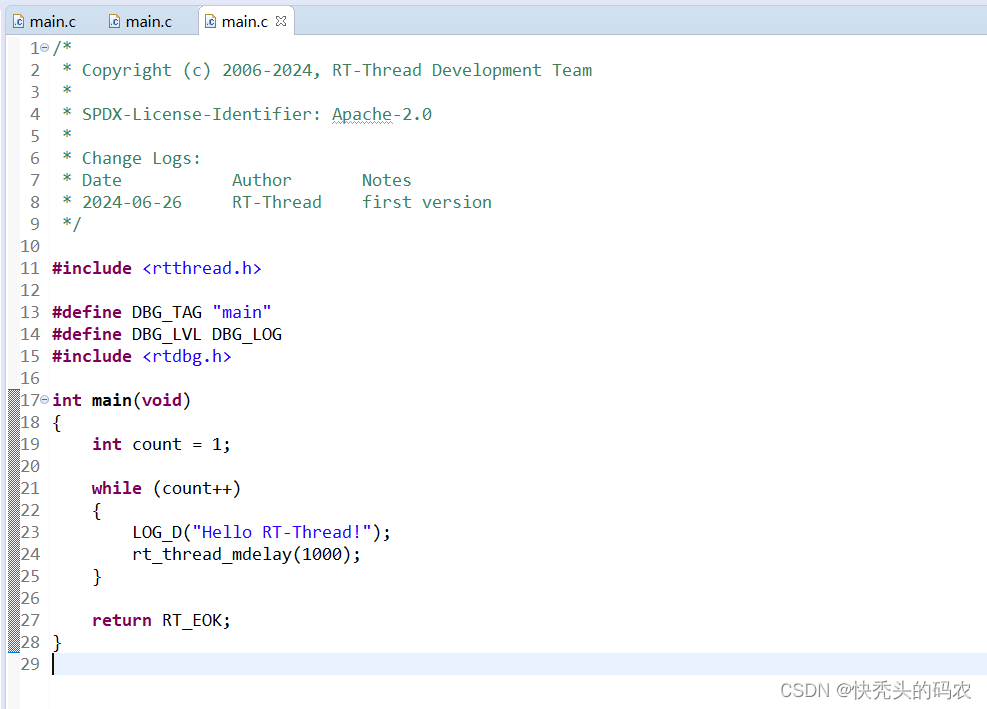

①打开“Open Elaborated Design”,此时在“Generate Bitstream”右键才会出现下图中蓝色字体“Configure additional bitstream settings”,单击它

②设置使能bit流加密,设置选择密钥存储位置为EFUSE。这里可以手动指定三个密钥的值,这个选择不指定即不填写任何东西,软件工具将会自动生成。

③设置回读配置为LEVEL1即禁止回读。此处要注意,并不是禁止从Flash里面回读,也就是说通过JTAG接口在hardware manager中选择flash器件点击右键选择readback configuration memory device依然可以回读,这里是告诉配置工具在 FPGA 配置完成后不要自动读取配置数据进行校验。

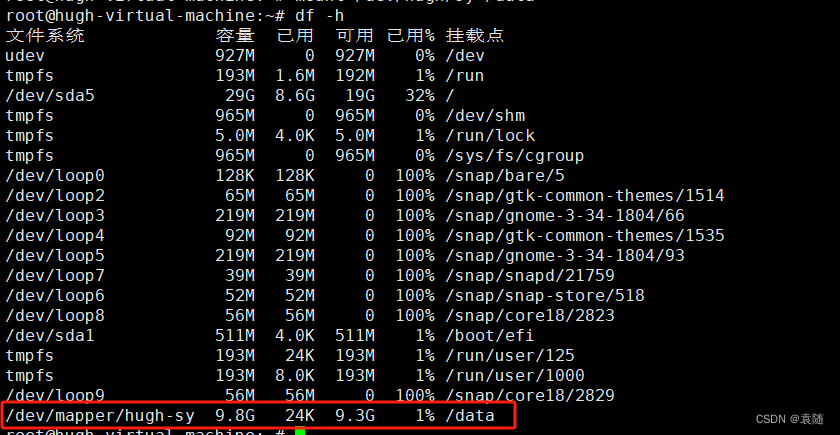

④上述配置完成之后一定在Elaborated Design界面点击保存或者ctrl+s配置才能生效,保存后会发现xdc文件中多了两句话,然后重新生成bit流,在与bit文件同级的文件夹中将会出现与bit流同名但后缀是nky的文件,这就是软件自动生成的密钥文件。现在生成mcs文件并烧写进FPGA发现FPGA不会启动,这是因为FPGA内部还没有密钥,需要进行下一节的操作。

3.2将密钥写入eFUSE寄存器

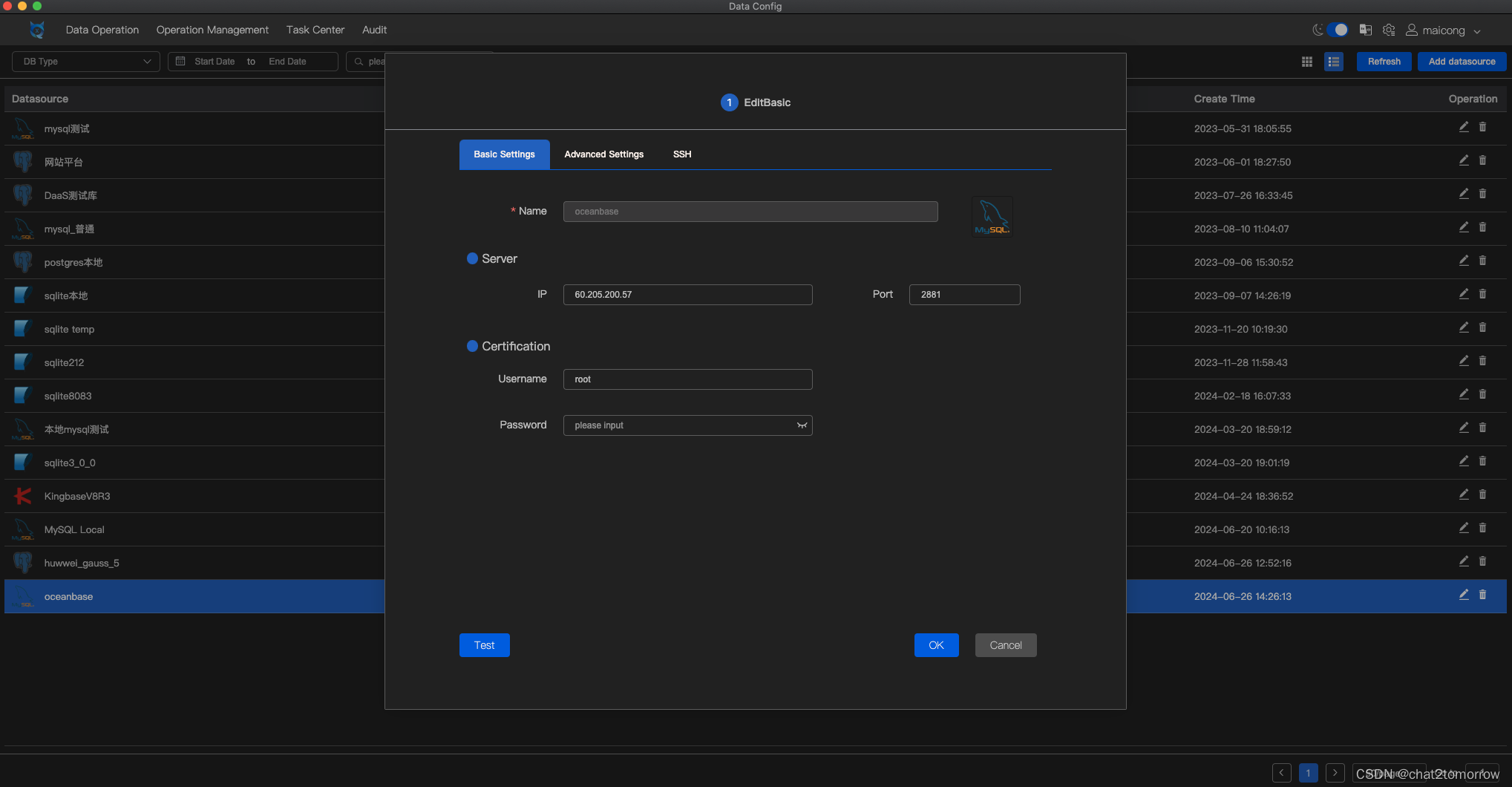

①打开vivado软件,连接JTAG并上电,打开Open Hardware Manager,进入Hardware界面,点击Auto Connect。在芯片名字上右键,选择Program eFUSE Registers。

②勾选Enable AES key programming,选择上一节生成的后缀为nky的文件,然后选择next。

③勾选Enable control register programming,接着按照如图所示勾选,此处千万不能勾选出错,否则造成严重后果!然后点击next。

④最后一页无需勾选,按照默认next即可,最后单击finish。导出的后缀nkz的文件将记录eFUSE的密钥信息和相关寄存器的配置信息。

4.验证结论

准备两块一摸一样的板卡A和B,制作一个简单的测试程序。

①在A板卡上配置了eFUSE寄存器,并将密钥写入eFUSE寄存器,此时烧写不加密的bit文件或者mcs文件,都是可以正常工作,并且回读A中的MCS文件烧写到B,B可以正常工作。

②在A板卡按照上述第三节配置,配置了eFUSE寄存器,写入密钥,并设置禁止回读,发现仍然可以回读,证明xdc中设置的禁止回读并不是禁止从flash读回mcs文件。

③给A板卡写入密钥1,并将工程用密钥1生成bit流,此时回读工程写入B板卡,B板卡无法完成FPGA代码加载。这里可以看出加密的最重要的作用就是禁止回读后逆向。同样如果给B写入的密钥不是密钥1,那么显然B还是无法加载。

④给A板卡在不写入密钥的情况下烧写加密的bit文件,FPGA无法完成加载。

5.传送门

- 我的主页

- FPGA开发必备技能专栏汇总导航

- 上一篇:FPGA开发技能(6)Qt生成ROM IP核使用的COE文件

| END |

💎文章原创,首发于CSDN论坛。

💎欢迎点赞💖收藏✨打赏💷!

💎欢迎评论区🎤或私信指出错误🎤,🗣️提出宝贵意见或疑问。