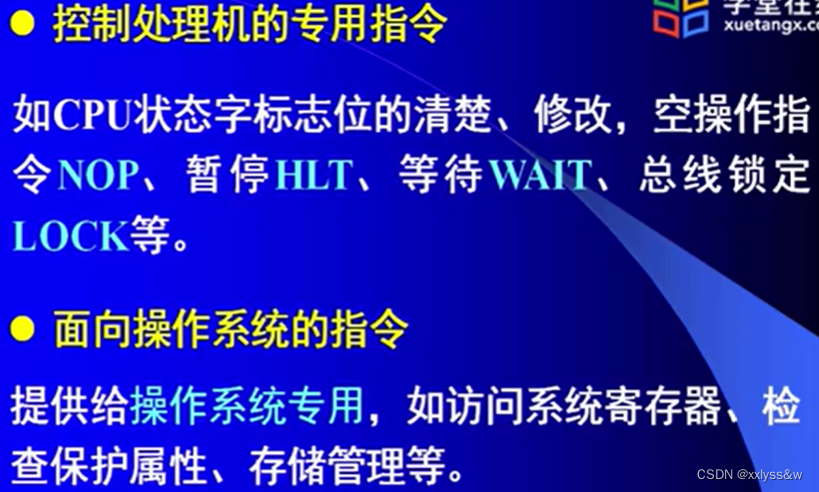

如果要对信号进行分析,可以使用外置的逻辑分析仪,但成本较高,对初学者来说没有必要,可以使用Xilinx Vivado内自带的逻辑分析仪IP核对信号进行分析,不过需要占用一定的芯片资源。

本节采用上一节配置的LED灯闪烁代码,对其中的信号进行捕获分析。

1 引入IP核

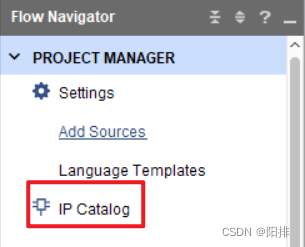

1、点击IP Catalog。

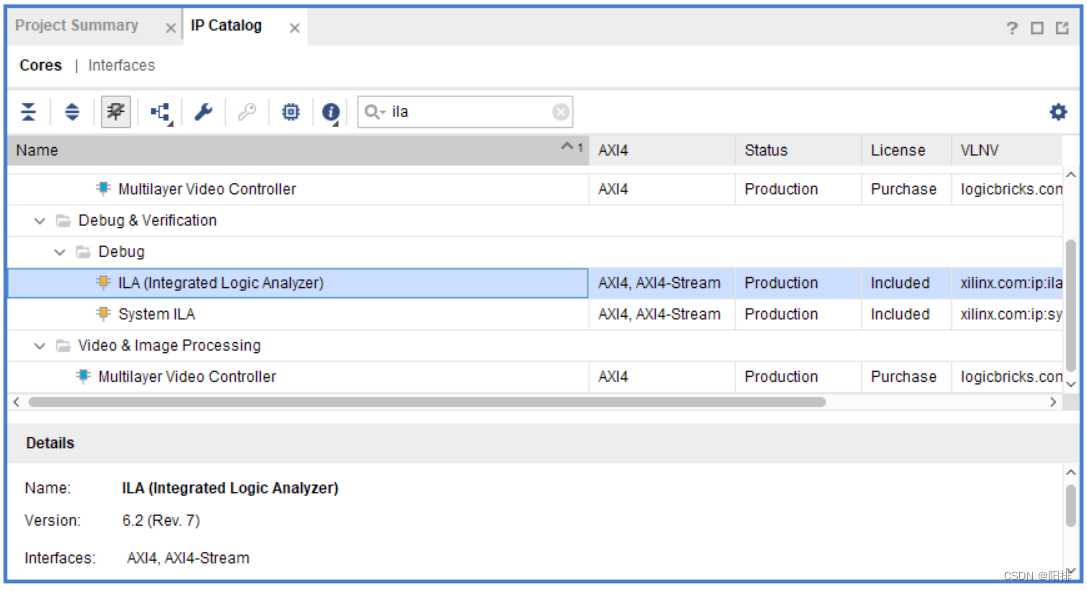

2、打开IP核。

在IP Catalog窗口中搜索并选择ILA (Integrated Logic Analyzer),双击打开。

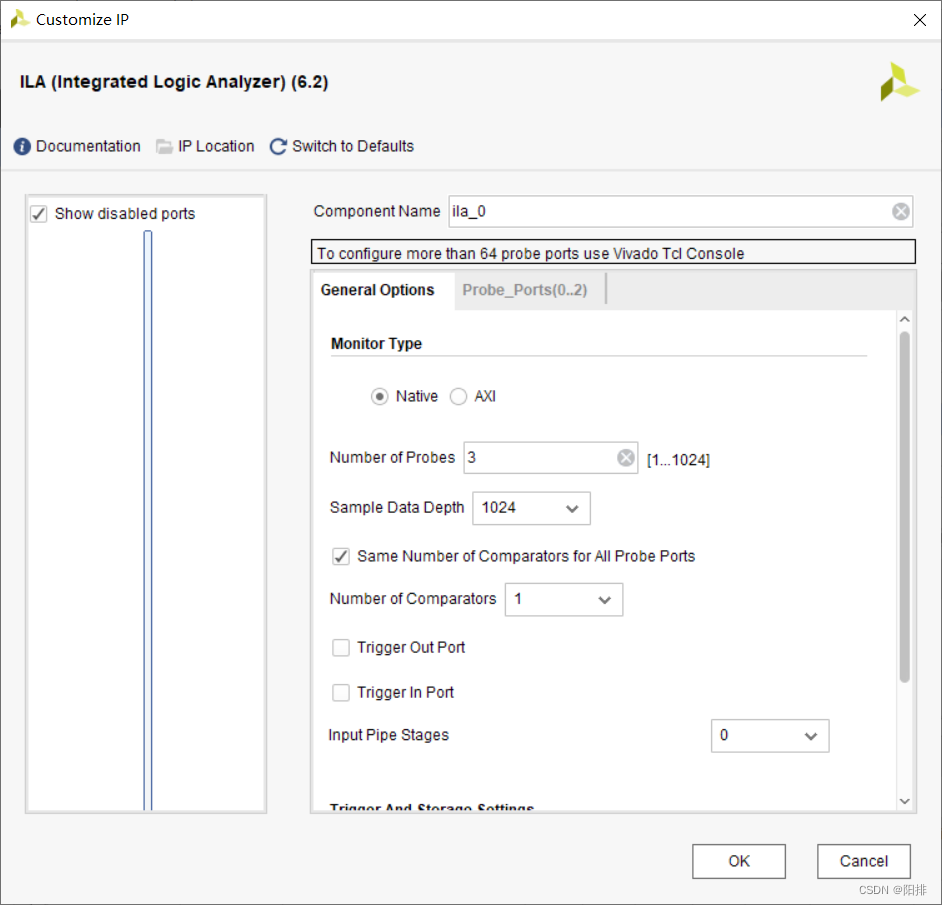

3、配置ILA

在General Options中:

(1)例化名称:Component Name 可以设置为默认

(2)监控类型:Monitor Type设置为Native

(3)探针数量:Number of Probes按照需要监控的端口数量进行配置,如果要监控

(4)采样深度:Sample Data Depth设置的越大,一次能看到的数据量越多,但对FPGA芯片的DRAM消耗也越多。

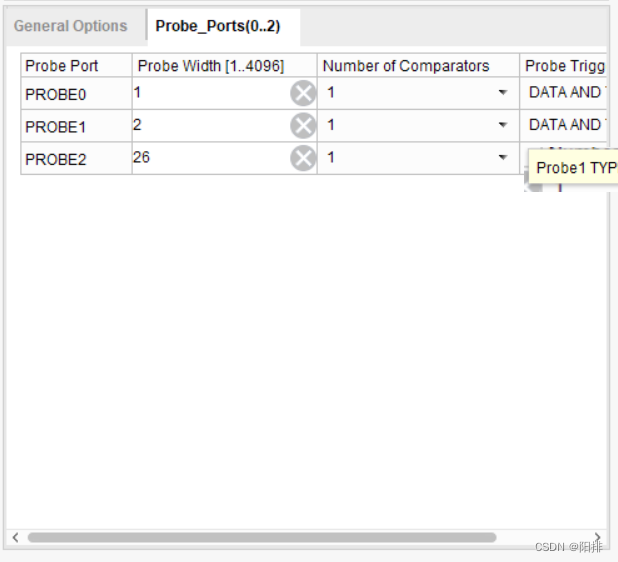

在Probe_Ports中:

根据前一页的设置,能看到3个探针端口,分别设置不同的位宽。

点击2次OK,自动新建文件夹存放ila的IP核。

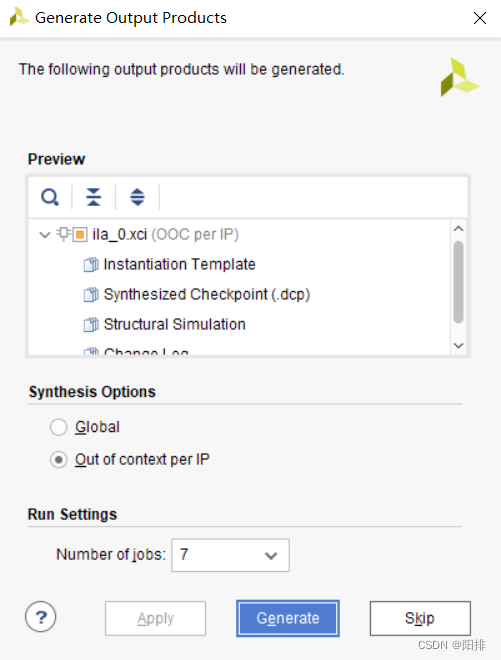

4、设置IP核综合模式:

弹出的Generate Output Products窗口,Synthesis Options选项如果选择Global,则每次修改文件都会让此IP核重新综合(调整IP核的位置和电路),如果选择Out of context per IP,则每次修改文件后都不会对IP核造成修改。因此这里选择Out of context per IP(OOC)。

点击Generate生成IP核。

2 例化IP核

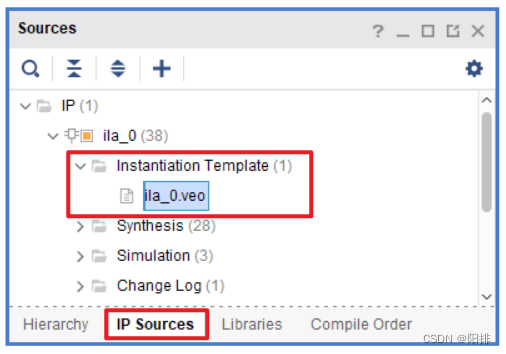

等待一小会儿,直到IP核加载完成。

1、打开模板文件:在Sources窗口下点击IP Sources,然后点击ila_0、Instantiation Template(例化模板),双击ila_0.veo打开模板文件。

2、复制例化代码:将ila_0.veo中的代码复制到顶层模块000_test_project.v中,并修改模块名称和探针所对应的端口。

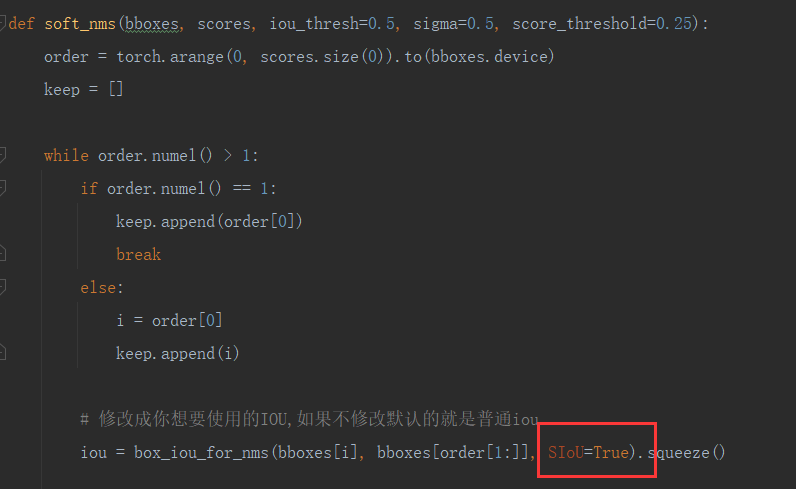

// ila_0.veo中代码

ila_0 your_instance_name (

.clk(clk), // input wire clk

.probe0(probe0), // input wire [0:0] probe0

.probe1(probe1), // input wire [1:0] probe1

.probe2(probe2) // input wire [25:0] probe2

);

需要注意所连接的变量位宽需要和探针位宽相对应。

// 000_test_project.v

module test_project(

input sys_clk,

input sys_rst_n,

output [1:0] led

);

// reg define

reg [25:0] cnt;

assign led = (cnt <= 26'd2500_0000) ? 2'b01 : 2'b10;

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 26'd0;

else if(cnt < 26'd5000_0000)

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

// 新加的模块 start

ila_0 my_ila_0 (

.clk(sys_clk), // input wire clk

.probe0(sys_rst_n), // input wire [0:0] probe0

.probe1(led), // input wire [1:0] probe1

.probe2(cnt) // input wire [25:0] probe2

);

// 新加的模块 end

endmodule

代码编写完成后保存。

3 ila试验

3.1 综合、实现、生成比特流

可以直接点击生成比特流,这三步软件会自动完成。

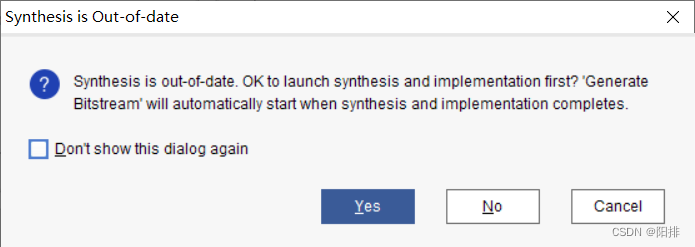

点击软件左侧Program and Debug,Generate Bitstream,在弹出的窗口Synthesis is Out-of-date后选择Yes。

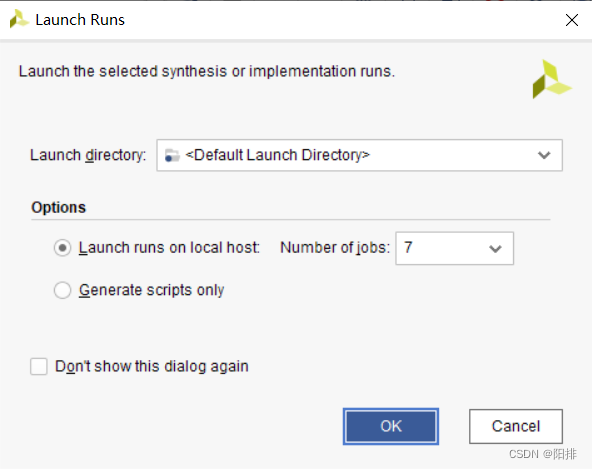

在弹出的Launch Runs窗口中自行选择Number of jobs CPU线程数,线程越多软件处理速度越快,然后点击OK。

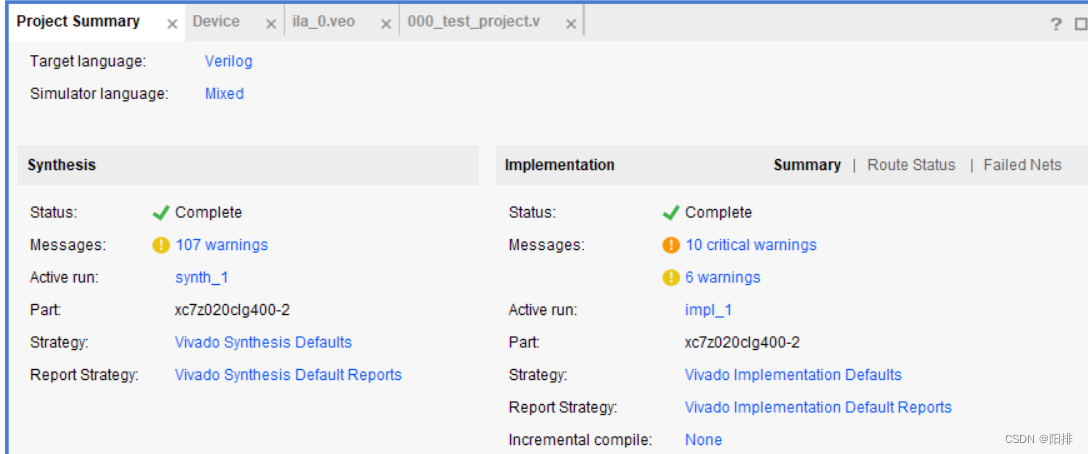

等待片刻,直到软件处理完成。点击Project Summary可以看到Synthesis、Implementation都显示绿色的√。

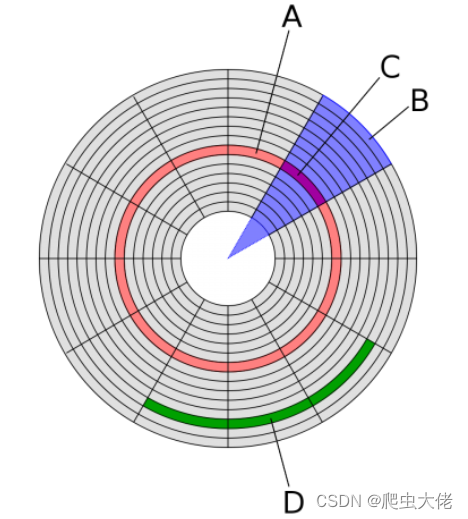

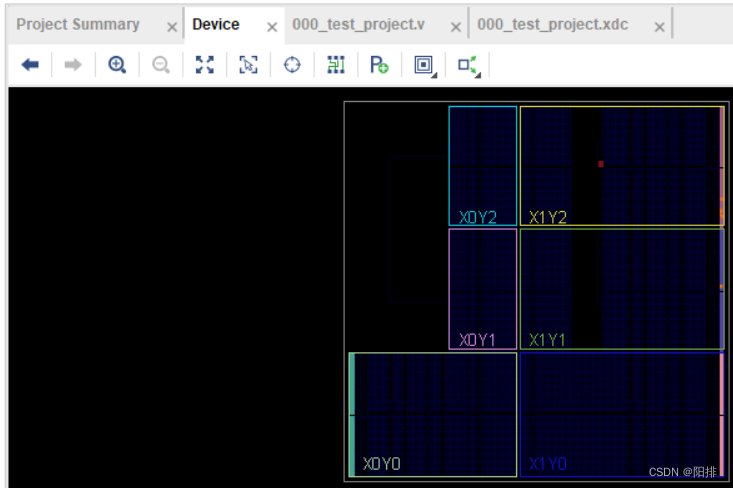

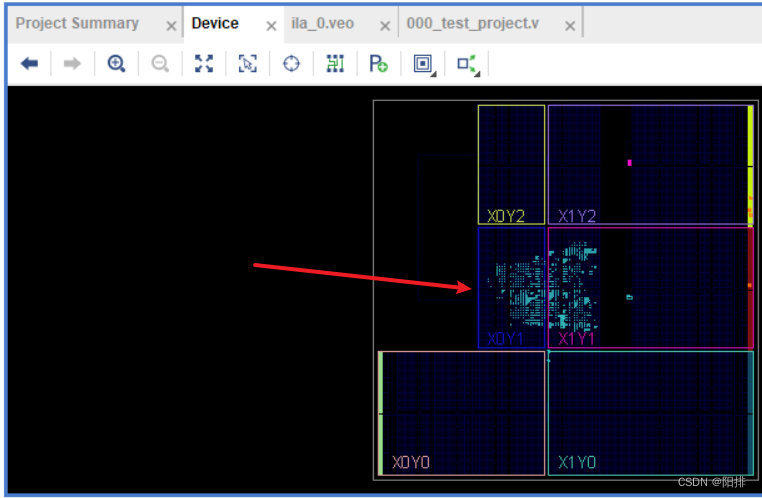

点开Device查看FPGA中PL的使用情况,可以发现相对于原来的让LED闪烁的逻辑电路,本实验中添加了ila后的使用了更多的逻辑资源。

不带ila的LED闪烁试验电路:

带ila的LED闪烁试验电路:

3.2 下载程序

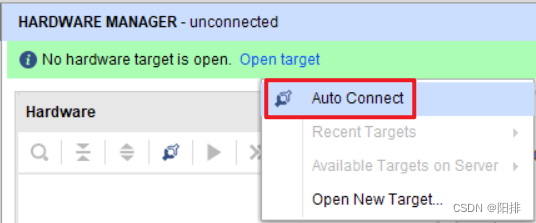

1、连接设备:拿出正点原子开发板,连接电脑。

点击Vivado的Open Hardware Manager,Open target,Auto Connect。

底部调试窗口Tcl Console显示如下信息,标明已经连接上开发板。

start_gui

open_project F:/FPGA/001_ZYNQ/004_ila_vio/004_ila_vio.xpr

open_project F:/FPGA/001_ZYNQ/004_ila_vio/004_ila_vio.xpr

Scanning sources...

Finished scanning sources

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'G:/Xilinx/Vivado/2018.2/data/ip'.

open_project: Time (s): cpu = 00:00:15 ; elapsed = 00:00:08 . Memory (MB): peak = 853.520 ; gain = 123.812

update_compile_order -fileset sources_1

reset_run synth_1

launch_runs impl_1 -to_step write_bitstream -jobs 7

[Tue Jun 25 21:29:30 2024] Launched synth_1...

Run output will be captured here: F:/FPGA/001_ZYNQ/004_ila_vio/004_ila_vio.runs/synth_1/runme.log

[Tue Jun 25 21:29:30 2024] Launched impl_1...

Run output will be captured here: F:/FPGA/001_ZYNQ/004_ila_vio/004_ila_vio.runs/impl_1/runme.log

open_run impl_1

INFO: [Netlist 29-17] Analyzing 106 Unisim elements for replacement

INFO: [Netlist 29-28] Unisim Transformation completed in 1 CPU seconds

INFO: [Project 1-479] Netlist was created with Vivado 2018.2

INFO: [Device 21-403] Loading part xc7z020clg400-2

INFO: [Project 1-570] Preparing netlist for logic optimization

INFO: [Timing 38-478] Restoring timing data from binary archive.

INFO: [Timing 38-479] Binary timing data restore complete.

INFO: [Project 1-856] Restoring constraints from binary archive.

INFO: [Project 1-853] Binary constraint restore complete.

Reading XDEF placement.

Reading placer database...

Reading XDEF routing.

Read XDEF File: Time (s): cpu = 00:00:00 ; elapsed = 00:00:00.289 . Memory (MB): peak = 1850.578 ; gain = 0.000

Restored from archive | CPU: 0.000000 secs | Memory: 0.000000 MB |

Finished XDEF File Restore: Time (s): cpu = 00:00:00 ; elapsed = 00:00:00.289 . Memory (MB): peak = 1850.578 ; gain = 0.000

INFO: [Project 1-111] Unisim Transformation Summary:

A total of 58 instances were transformed.

CFGLUT5 => CFGLUT5 (SRLC32E, SRL16E): 52 instances

RAM32M => RAM32M (RAMD32, RAMD32, RAMD32, RAMD32, RAMD32, RAMD32, RAMS32, RAMS32): 6 instances

open_run: Time (s): cpu = 00:00:30 ; elapsed = 00:00:25 . Memory (MB): peak = 1926.605 ; gain = 963.371

open_hw

connect_hw_server

INFO: [Labtools 27-2285] Connecting to hw_server url TCP:localhost:3121

INFO: [Labtools 27-2222] Launching hw_server...

INFO: [Labtools 27-2221] Launch Output:

****** Xilinx hw_server v2018.2

**** Build date : Jun 14 2018-20:42:52

** Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

open_hw_target

INFO: [Labtoolstcl 44-466] Opening hw_target localhost:3121/xilinx_tcf/Digilent/210512180081

set_property PROGRAM.FILE {F:/FPGA/001_ZYNQ/004_ila_vio/004_ila_vio.runs/impl_1/test_project.bit} [get_hw_devices xc7z020_1]

set_property PROBES.FILE {F:/FPGA/001_ZYNQ/004_ila_vio/004_ila_vio.runs/impl_1/test_project.ltx} [get_hw_devices xc7z020_1]

set_property FULL_PROBES.FILE {F:/FPGA/001_ZYNQ/004_ila_vio/004_ila_vio.runs/impl_1/test_project.ltx} [get_hw_devices xc7z020_1]

current_hw_device [get_hw_devices xc7z020_1]

refresh_hw_device [lindex [get_hw_devices xc7z020_1] 0]

INFO: [Labtools 27-1435] Device xc7z020 (JTAG device index = 1) is not programmed (DONE status = 0).

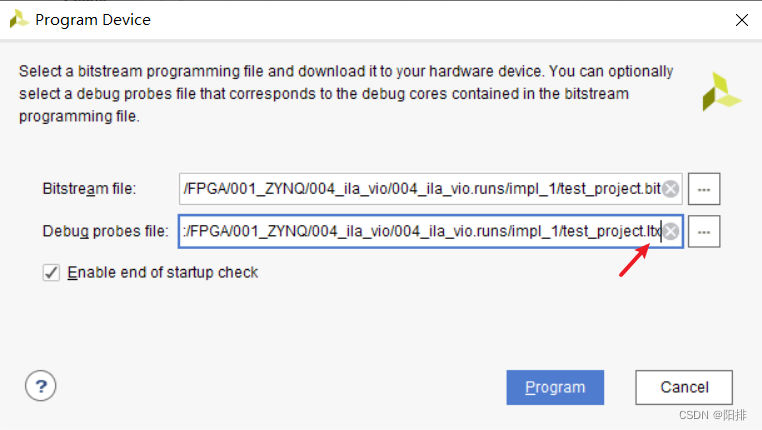

2、下载程序:

点击左上角的Program device下载程序。

可以发现下方Debug probes file出现了.ltx文件,内部包含了调试的一些探针信息,点击Program下载程序。

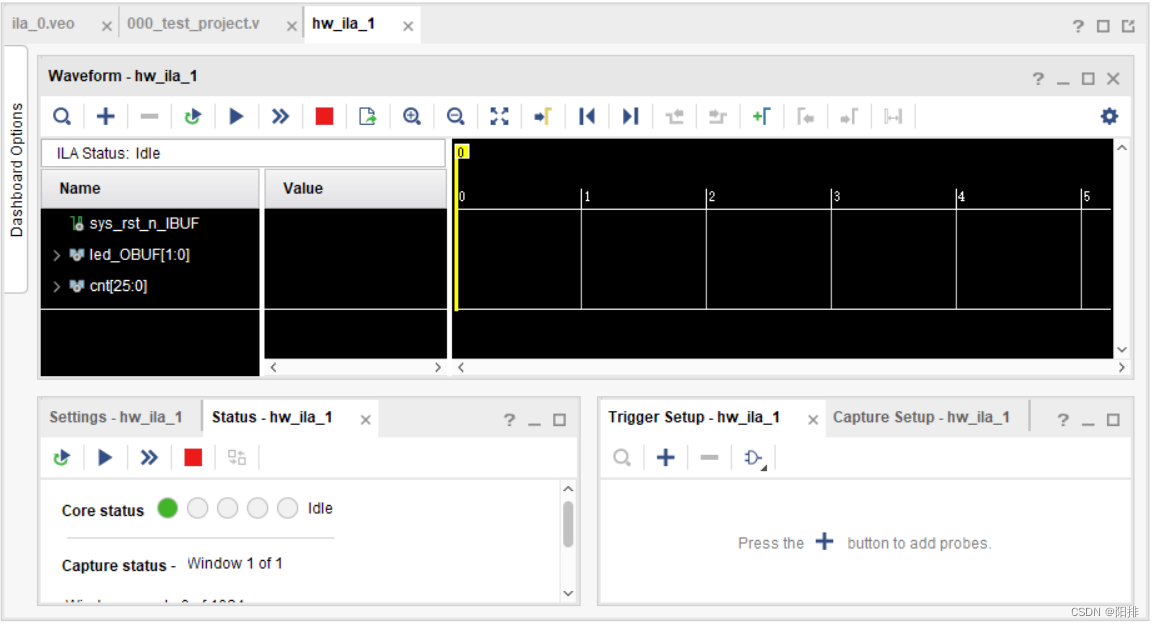

3、查看波形:

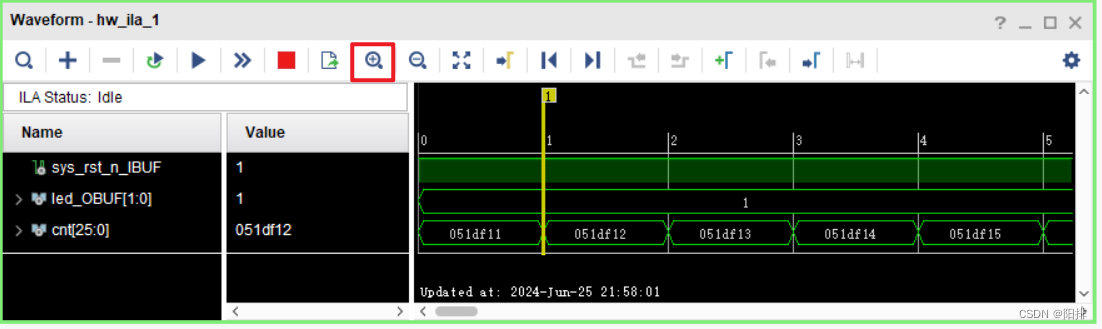

在下载完成后,Vivado软件会弹出Waveform - hw_ila_1波形图窗口,三个探针已经添加到波形图中。

窗口按钮部分功能:

- Add +:添加信号。

- Remove Selected -:删除信号。

- Toggle auto re-trigger mode for this ILA core:自动触发。

- Run trigger for this ILA core:手动触发。

- Run trigger immediate for this ILA core >>:立即触发。

- Stop trigger for this ILA core:停止触发。

- Export ILA waveform data:导出逻辑分析仪波形数据。

- Zoom In:放大。

- Zoom Out:缩小。

点击Run trigger for this ILA core,探针会捕获信号。然后点击放大。

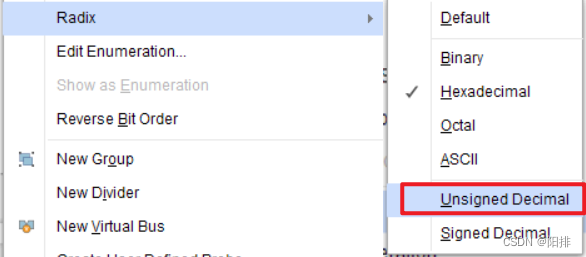

右键Name列表下的信号,可以修改信号显示的Radix进制,这里可以选择为Unsigned Decimal无符号十进制。

4、设置触发条件:

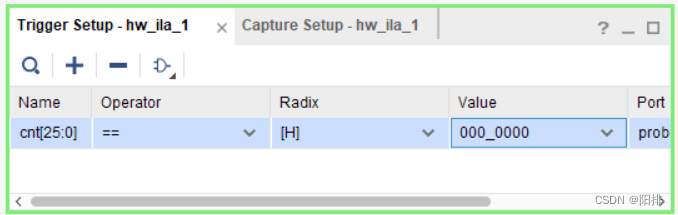

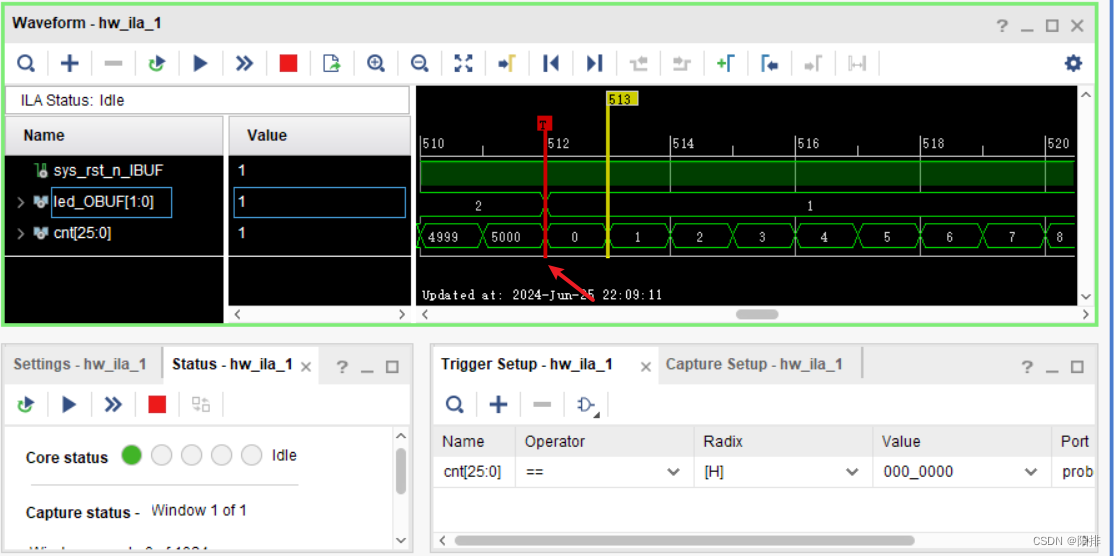

右下角的Trigger Setup可以设置触发条件,一位可以设置逻辑1触发(logic one)、逻辑0触发(logic zero)、上升沿触发(R)、下降沿触发(F)、双端触发(B)等等。多位可以设置为到一定的值触发。

此处设置cnt的值为0000000时触发。

再次点击Run trigger for this ILA core,可以发现红色的T触发标记出现在了cnt为0的时候。此时led_OBUF[1:0]也变成从2变成了1,代表LED灯发生交替变化。

3.3 调试完毕后处理

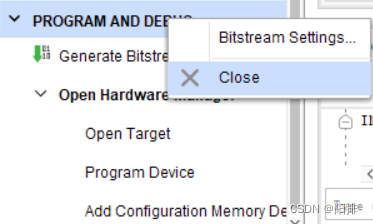

1、断开设备连接:右键PROGRAM AND DEBUG,点击Close即可断开开发板与电脑的连接。

2、删除调试模块:

由于ILA会占用较多的硬件资源,因此在debug完成后可以直接在顶层文件中注释或删除ila的模块代码。

//000_test_project.v

//ila_0 my_ila_0 (

// .clk(sys_clk), // input wire clk

// .probe0(sys_rst_n), // input wire [0:0] probe0

// .probe1(led), // input wire [1:0] probe1

// .probe2(cnt) // input wire [25:0] probe2

//);

代码保存后,重新生成比特流文件就可以获得原来资源使用较少的工程。