将多个数字信号处理 (DSP) 块、宽带数模转换器 (DAC) 和宽带模数转换器 (ADC) 集成到单个单片芯片中,现在可以卸载耗电的 FPGA 资源,以允许更小的占地面积、更低的功耗、增加通道数的平台,能够以比以前更高的速率进行采样。伴随这一新功能而来的是这些集成电路 (IC) 中的新颖多芯片同步 (MCS) 算法,它允许用户在为系统供电或以其他方式对系统进行软件修改时为所有通道实现已知(确定性)相位。因此,这个确定性阶段简化了更广泛的系统级校准算法,以实现所有通道在输出或输入到连接到这些 IC 的前端网络的同步。本文展示了使用由多个数字转换器 IC、时钟源和数字接口组成的 16 通道接收器/发送器平台时展示此 MCS 功能的实验结果。

系统框图

用于此测试的系统框图如图 1 所示,由四个集成 DAC/ADC/DSP IC 组成,每个 IC 由四个 12 GSPS DAC、四个 4 GSPS ADC、12 个数字上变频器 (DUC) 和 12 个数字下变频器 (DDC) 块。

图 1. 用于演示 MCS 和多通道校准算法的系统框图。(:Analog Devices)

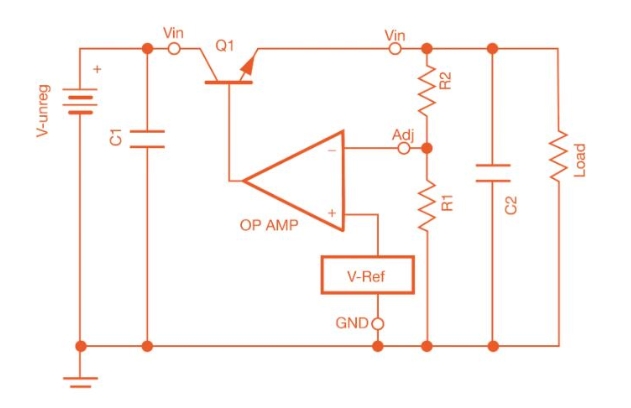

DUC/DDC 允许在数字域内进行频率转换和/或内插/抽取。使用注入到板上的单个 500 MHz 参考时钟,然后使用参考锁定时钟缓冲器生成 MCS 所需的系统参考信号以及基带处理器 (BBP) 数字接口所需的时钟。该系统还包含四个独立的锁相环 (PLL) 合成器,这些合成器生成从公共参考源为每个数字化 IC 提供时钟所需的 12 GHz 源。RF 前端连接到每个数字化仪输出/输入,它创建一个过滤和放大的信号到/从边缘发射的 RF 连接器。实施完整的配电解决方案。系统所需的所有电压均由单个 12 V 电源产生。

子阵时钟树结构

如前所述,子阵列时钟树由一个 500 MHz 参考源组成,该参考源被拆分并发送到四个独立 PLL 合成器 IC 的参考输入,如上图 1 所示。这个 500 MHz 信号也是 10 dB 耦合、放大,并发送到另一个时钟缓冲器 IC,负责生成数字接口所需的系统参考 (SYSREF) 和 BBP 时钟。这个时钟树的目标有三个,因为它:

允许单个通道 SYSREF 延迟以纠正 IC 之间的任何走线长度不匹配。

允许单独的 PLL/合成器相位调整,因此确保各个数字化器 IC 时钟源之间的同步,以补偿系统内任何感应的热梯度。

使用户能够实现数字化 IC 的必要设置和保持要求。

选择时钟树 IC 是为了证明各种电路板布局异常可以在这些芯片中存在的数字和模拟延迟块的帮助下在软件和/或硬件中得到纠正。终结果是一个时钟树,它可以在每个 IC 的相同采样时钟周期内向所有需要的 IC 提供 SYSREF 脉冲。

与基带处理器的数字接口

四个数字化 IC 各自建立一个与 BBP 的 JESD204B 或 JESD204C 数字链路接口。1,2该接口负责通过物理走线 (SERDES) 将 ADC 和 DAC 代码传输到 BBP 或从 BBP 传输。此接口中使用的差分 SERDES 走线数称为此链路的通道数 (L)。通过链路发送的转换器位分辨率被视为 N'。通道化数据路径(也称为虚拟转换器)的数量标记为 M。本文所示结果使用 JESD204C 链路,M = 16,N' = 16,DAC 侧链路 L = 4,M = 8 , N' = 16, L = 2 对于 ADC 端链路。

在数字转换器 IC 和 BBP 之间传输和接收数据的速率被称为通道速率。硅片上的 DSP 模块(即 DDC/DUC)允许用户以不同于通过物理通道发送的数据速率的速率对数字化仪进行采样。因此,通道速率取决于每个数据路径的数字抽取/内插数据速率。对于这项工作,使用了 250 MSPS I/Q 数据速率。对于 JESD204C 接口,通道速率定义为:

而对于 JESD204B 接口,通道速率定义为:

本文所示结果对 ADC 和 DAC 端 JESD204C 链路使用 16.5 Gbps 的通道速率。

每个 JESD204B/JESD204C 链接都可以在不同的子类中建立。这些子类根据是否需要多芯片同步或确定性延迟来分离。对于这项工作,显示的数据使用 JESD204C 子类 1 模式,因此利用 SYSREF 信号对齐跨系统中存在的多个链路传输的数字数据部分。具体而言,在此 JESD204C 子类 1 模式中,SYSREF 信号用于对齐本地扩展多块计数器 (LEMC),其传输速率为:

其中 F 是每个通道每个 JESD 帧的八位字节数,K 是每个单个多帧的帧数。对于这项工作,F = 8 且 K = 32,因此使用 7.8125 MSPS 的 LEMC 速率。了解此 LEMC 速率很重要,因为任何成功的 MCS 例程都需要证明不是 LEMC 速率整数倍的 RF 频率能够实现确定性的上电阶段。

多芯片同步方法

在该系统中,宽带集成 ADC/DAC IC 提供 MCS 电路,以允许所有发射和接收 RF 通道上的加电确定性相位,即使在 IC 内使用 DUC/DDC DSP 块时也是如此。此 MCS 功能使用户能够在工厂校准期间填充查找表 (LUT),以限度地减少操作停机时间。任何成功的 MCS 演示都必须能够为每个尝试的 RF 频率、热梯度和系统电源循环提供系统内所有通道的确定性相位。

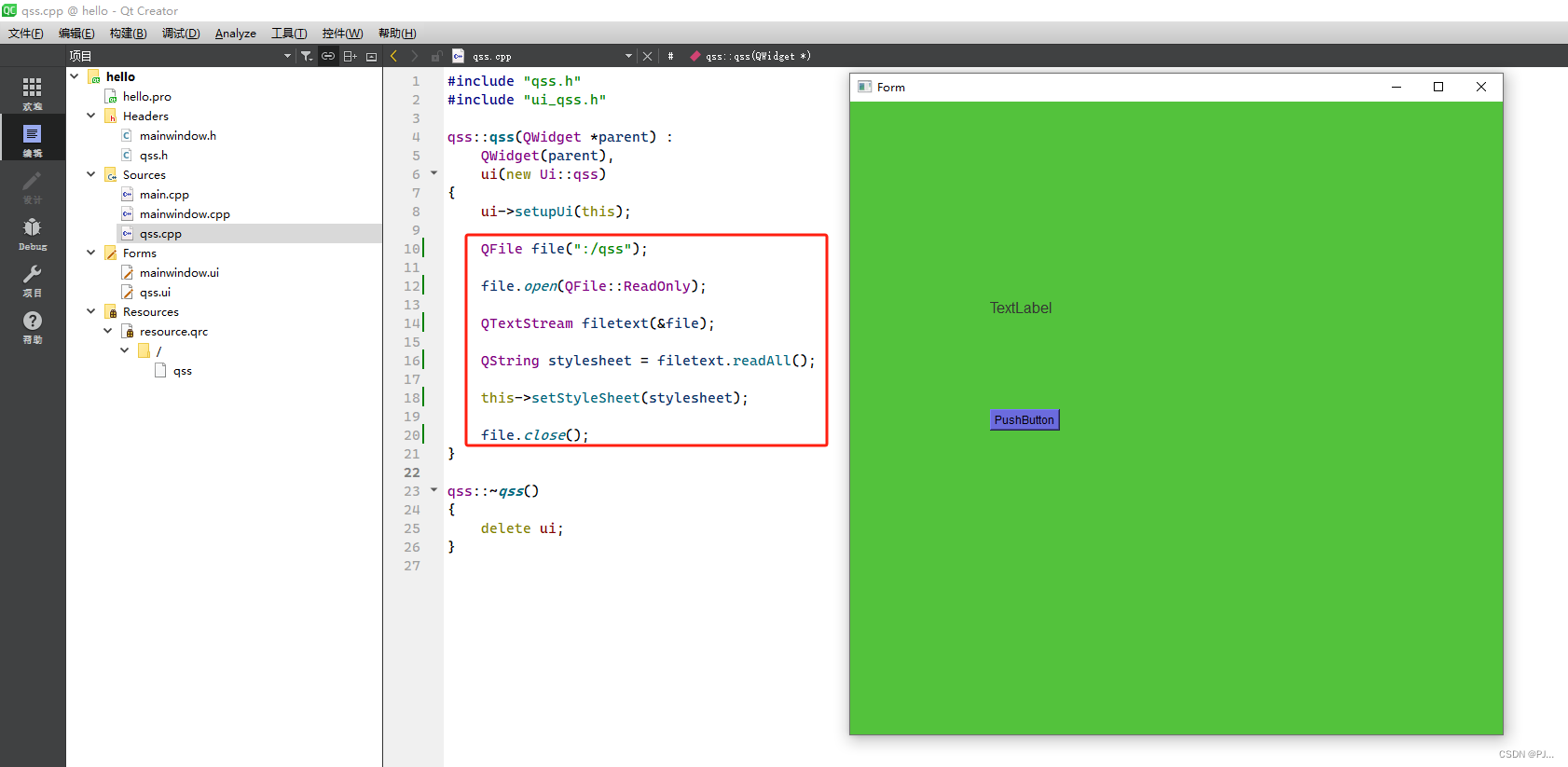

集成 ADC/DAC IC 包含 12 个 DUC 块和 12 个 DDC 块,如上图 1 所示。这些块中的每一个都包含一个插值 (DUC) 或抽取 (DDC) 子块,以更改 DAC 数字输入信号的数据速率或分别为ADC数字化输出信号。每个 DUC/DDC 中还包含一个复杂的数控振荡器 (NCO),它允许在数字域内进行频率转换。这些 NCO 中的每一个都能够进行实时复杂的相位调整,以便可以修改 DAC/ADC 和 BBP 之间的数字信号,以补偿各种 SERDES 走线长度不匹配。

这些 ADC/DAC IC 的 MCS 功能负责在数字化仪 IC 数据路径的所有方面实现相位确定性。实现 MCS 的工作流程如图 2 所示。

图 2. MCS 工作流程涉及对齐数据路径不同部分的单独功能。(:Analog Devices)

MCS算法可以分为两个独立的功能:

性同步:此功能负责对齐通过子阵列系统内所有数字化仪 IC 的物理通道发送的基带数据。

NCO 主从同步:此功能负责对齐子阵列系统内所有不同数字化仪 IC 中的所有 NCO。

单次同步功能首先要求用户定义 JESD 链路参数(如 M、N'、L 等),然后为任何所需的 SYSREF 平均配置同步逻辑(如果使用连续的 SYSREF 脉冲)。此外,所需的 LEMC 延迟可用于强制在 SYSREF 边沿之后的某个延迟生成 LEMC。完成后,用户随后启用每个数字转换器 IC 中的单次同步位,然后请求在同一时钟周期内向每个 IC 发送 SYSREF 脉冲,如图 3 所示。

图 3. MCS 算法使用 SYSREF 信号实现单次同步,使用 GPIO 信号实现 NCO 主从同步以实现确定性相位。(:Analog Devices)

对于该系统,时钟缓冲器 IC 中引入了模拟精细延迟,以允许所有数字转换器 IC 同步 SYSREF。可以执行后续检查,通过查询每个 IC 内的寄存器来验证单次同步过程是否成功执行,这些寄存器提供有关 SYSREF 信号和每个 IC 链路的 LEMC 边界之间相位关系的信息。

一旦测量到稳定的相位(即,一旦 SYSREF-LEMC 相位寄存器读数为 0),用户便知道所有数字化仪 IC 的 LEMC 已对齐,然后用户可以继续进行 NCO 主从同步过程。对于此活动,为性同步描述的子任务包含在芯片制造商提供的应用程序编程接口 (API) 中。

NCO 主从同步功能首先指定子阵列中的一个数字化仪 IC 作为主芯片,如上图 3 所示。所有其他数字化仪随后被视为从属 IC。主 IC 的设置使得该设备的 GPIO0 引脚配置为输出并路由到三个从属数字转换器 IC 的 GPIO0 网络。从属 GPIO0 网络配置为输入。然后用户可以选择在 SYSREF 脉冲、LEMC 上升沿或 LEMC 下降沿触发。对于本文中显示的数据,LEMC 上升沿用作 NCO 主从同步触发源,GPIO 网络通过 BBP 布线,而不是在子阵列上本地布线。接下来,DDC 同步位先切换为低电平,然后再切换为高电平,以启动 ADC 端 NCO 同步算法。同样地,

当请求此触发器时,在下一个 LEMC 上升沿,主数字化器 IC 通过其 GPIO0 网络将主输出信号置为高电平。该信号传播到每个从属设备的 GPIO0 输入。在下一个 LEMC 边缘,所有数字化仪 IC 都会经历 NCO 重置算法。此后,对于 NCO 主从同步算法,任何 LEMC 脉冲都将被忽略。与性同步一样,这些 NCO 主从同步子任务包含在 API 函数中,以方便用户使用。

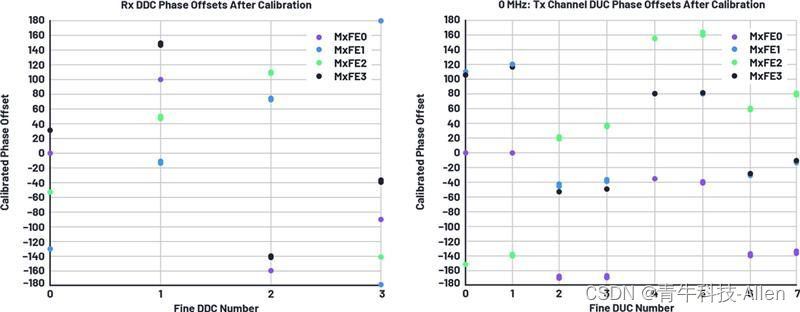

使用单次同步和 NCO 主从同步功能将两个输入对准每个 DDC/DUC,这样每个接收和发送通道的输出相位偏移在多个电源循环后可重复,如图 4 所示。数据图 4 中的 显示了在每次重新启动期间系统在静态热梯度下运行时,每个接收和发射通道化器在 100 个功率循环(由多个实心点表示)内的校准相位偏移。

图 4. 接收精细 DDC(左)和传输精细 DUC(右)在执行 MCS 算法时正确对齐。(:Analog Devices)

从该图中存在的多个点可以看出,给定 DDC/DUC 的每种颜色的点在电源循环后都紧密聚集到同一位置,从而描绘了该特定通道的确定性相位。对于本次测试中的数据,所有八个通道化器 DUC 都已在发送端使用,而八个通道化器 DDC 中仅使用了四个。然而,已经证实所有八个通道化器 DDC 在使用 MCS 算法时确实提供了确定性相位。

如果 PLL 合成器采样时钟和时钟 IC SYSREF 在启动时保持相同的相位关系,则在启动时发出此算法会为??每个通道建立确定性相位。然而,任何系统都会经历热梯度,这会导致 PLL 时钟漂移,如果不进行补偿,则会导致不同的上电阶段。为了补偿系统内的热梯度漂移,该平台利用 PLL 合成器相位调整。

在本系列文章的下一部分,我们将探讨 PLL 合成器相位调整、多个子阵列的可扩展性和系统级校准算法。