PCB走线的阻抗对每个网络的信号完整性至关重要,但是,验证每个信号是不切实际的,尤其对于设计复杂度很高的产品而言,设计者的有限精力只能用于关注关键的设计点,这一过程往往会造成一些设计的疏忽从而导致错误。

ADS SIPro中,提供了一个不用进行S参数提取而快速计算走线阻抗的小工具-RapidScan-Z0,通过这个工具,设计者可以任意可视化地查看走线阻抗以及定位不符合设计规格的走线部分。

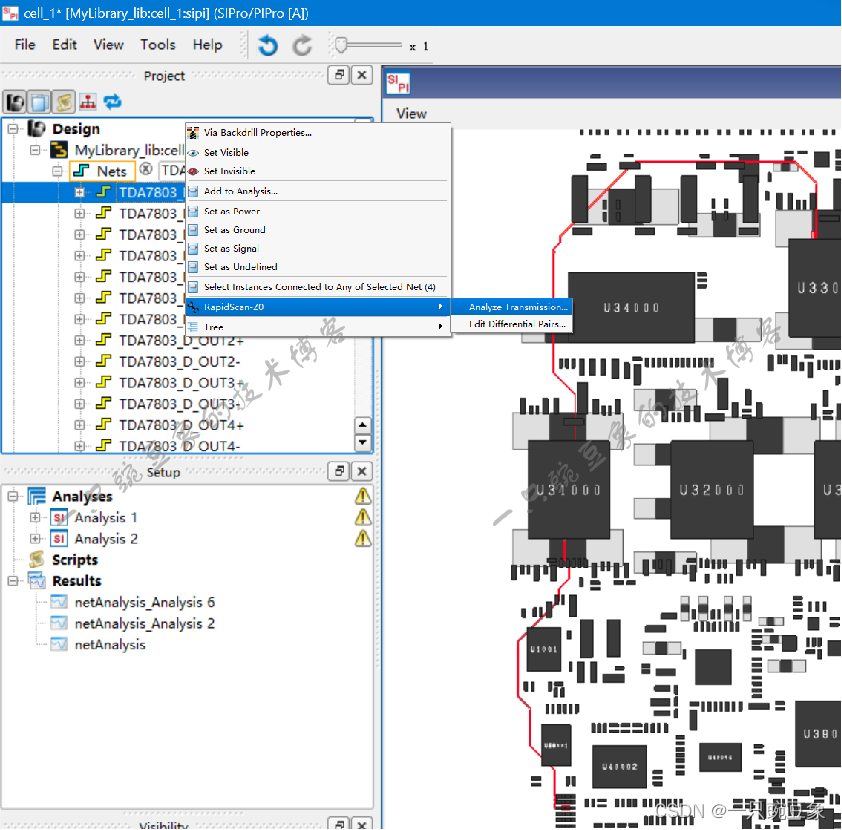

以一个设计为例,在对PCB的时钟线路进行阻抗检查时,可以在需要检查的信号网络上鼠标点击右键,在弹出的菜单栏中选择RapidScan-Z0-->Analyze Transmission...,软件会快速计算这根走线的阻抗。

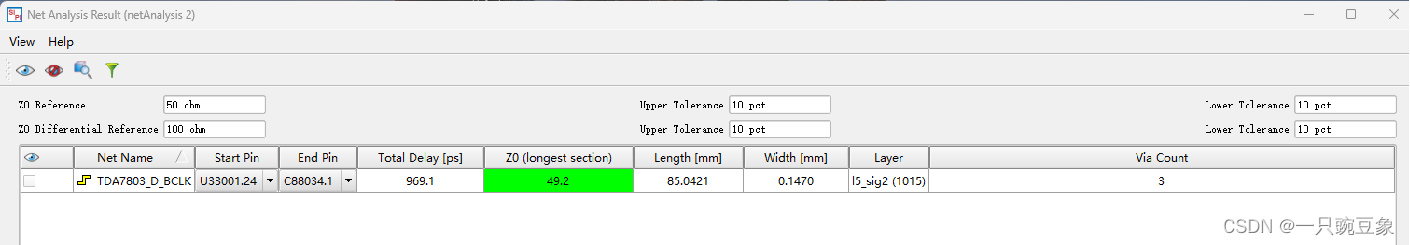

弹出的对话框中会显示如下的阻抗计算结果,但这个结果很笼统,不能反映出整个走线的阻抗变化情况;

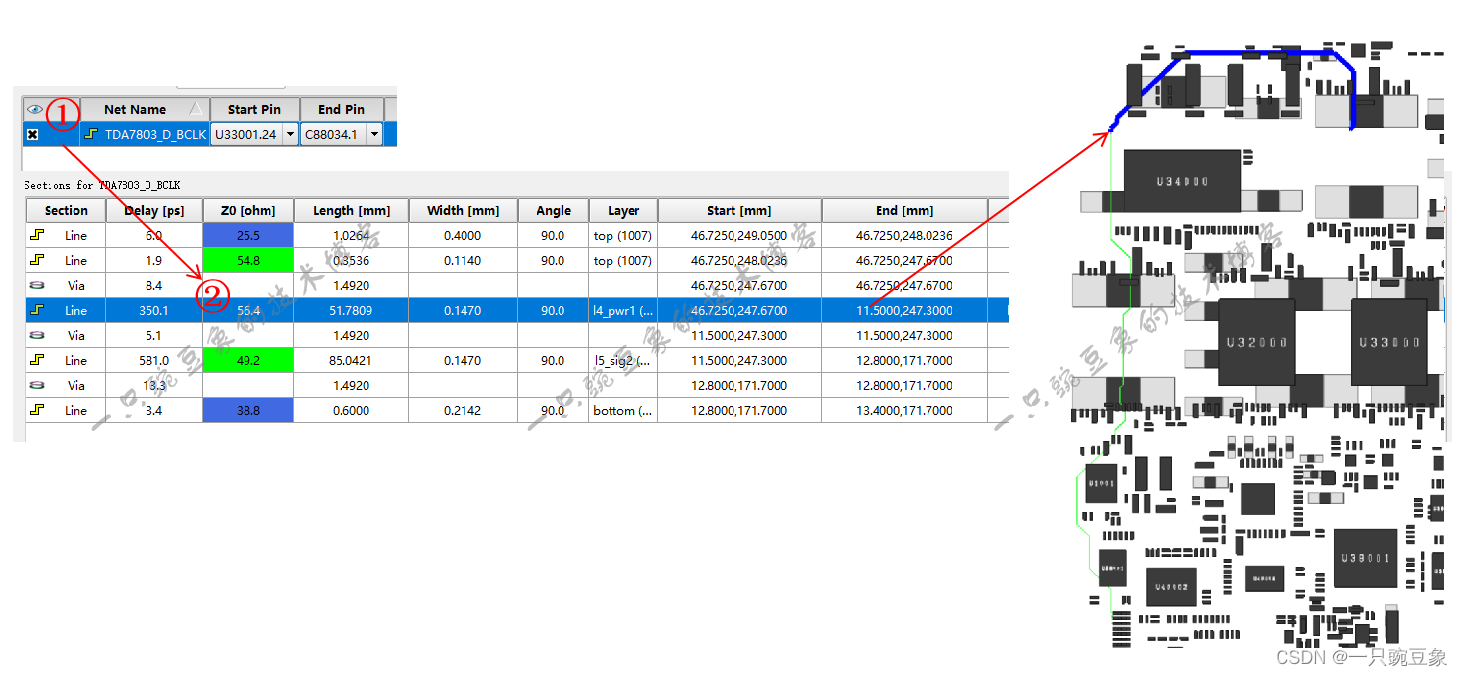

鼠标左键单击选中该网络,在下方的菜单栏中可以展现出走线随参考面的阻抗变化情况,此时,就发现了问题,如图中红色虚线框所示,该段走线的阻抗高达56.4欧姆,并不符合50±10%的设计要求;

此时,再按照下图所示的操作步骤,可以快速地在PCB设计文件中高亮出该走线所在的位置,经过检查发现,产生阻抗异常的原因:走线由第5层换到了第6层,而在叠构设计中,并未对第6层的走线做出阻抗控制的要求,因此,走线宽度并未因换层做出调整。

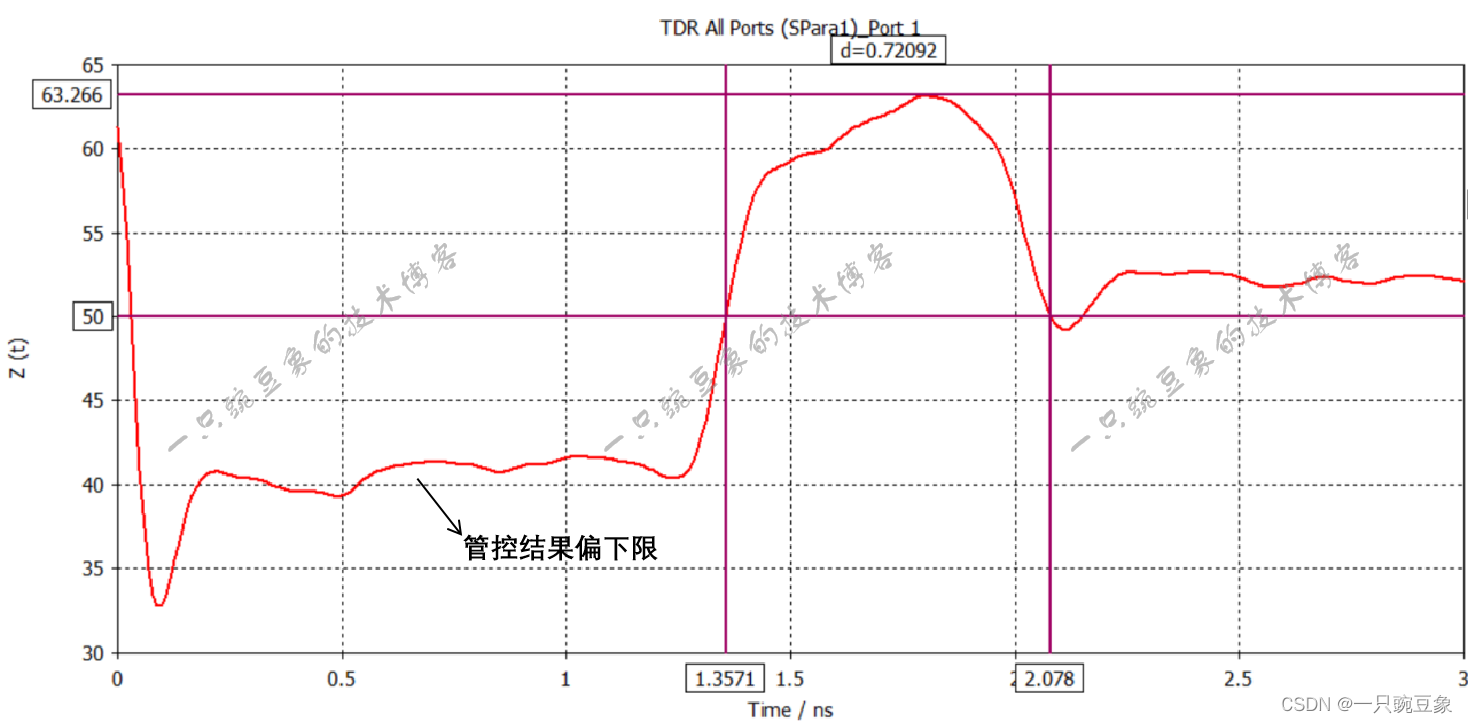

由于上述问题是在样件测试阶段发现的,因此,对该走线进行了TDR测试,测试结果显示,这段走线确实会出现阻抗偏高,并且传播延时也基本可以匹配上,再加之样件试制阶段,板厂的阻抗控制并不精准(实测管控结果偏下限),因此,这类阻抗偏差问题,导致了时钟信号剧烈地信号反射。

上述案例是在偶然间产生的,却验证了RapidScan-Z0工具的使用意义,与此同时,也是一个很好的Lessons-learn,告诫设计者不能疏漏任何一个设计的关键细节。

![[汇总] Docker容器详解 Macvlan 创建不同容器独立跑仿真(持续更新中)](https://img-blog.csdnimg.cn/direct/3aa76f80bc134f838599f2ae0ec3bb1b.png)