代码:

sort4.v

module sort4(ra,rb,rc,rd,a,b,c,d);

output[3:0] ra,rb,rc,rd;

input[3:0] a,b,c,d;

reg[3:0] ra,rb,rc,rd;

reg[3:0] va,vb,vc,vd;

always @ (a or b or c or d)

begin

{va,vb,vc,vd}={a,b,c,d};

sort2(va,vc); //va 与vc互换。

sort2(vb,vd); //vb 与vd互换。

sort2(va,vb); //va 与vb互换。

sort2(vc,vd); //vc 与vd互换。

sort2(vb,vc); //vb 与vc互换。

{ra,rb,rc,rd}={va,vb,vc,vd};

end

task sort2;

inout[3:0] x,y;

reg[3:0] tmp;

if(x>y)

begin

tmp=x; //x与y变量的内容互换,要求顺序执行,所以采用阻塞赋值方式。

x=y;

y=tmp;

end

endtask

endmodule

sort4.vt

`timescale 1 ns/ 100 ps

module sort4_vlg_tst();

// constants

// general purpose registers

// test vector input registers

reg [3:0] a;

reg [3:0] b;

reg [3:0] c;

reg [3:0] d;

// wires

wire [3:0] ra;

wire [3:0] rb;

wire [3:0] rc;

wire [3:0] rd;

// assign statements (if any)

sort4 i1 (

// port map - connection between master ports and signals/registers

.a(a),

.b(b),

.c(c),

.d(d),

.ra(ra),

.rb(rb),

.rc(rc),

.rd(rd)

);

initial

begin

a=0;b=0;c=0;d=0;

repeat(50)

begin

#100 a ={$random}%15;

b ={$random}%15;

c ={$random}%15;

d ={$random}%15;

end

#100 $stop;

end

endmodule

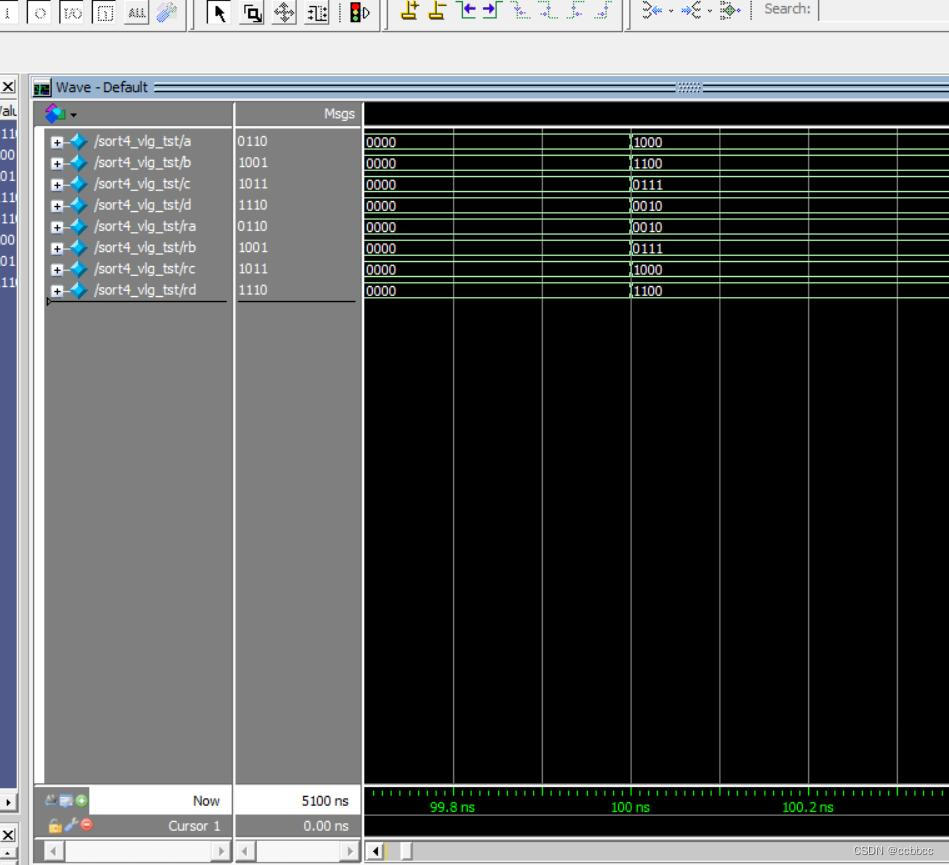

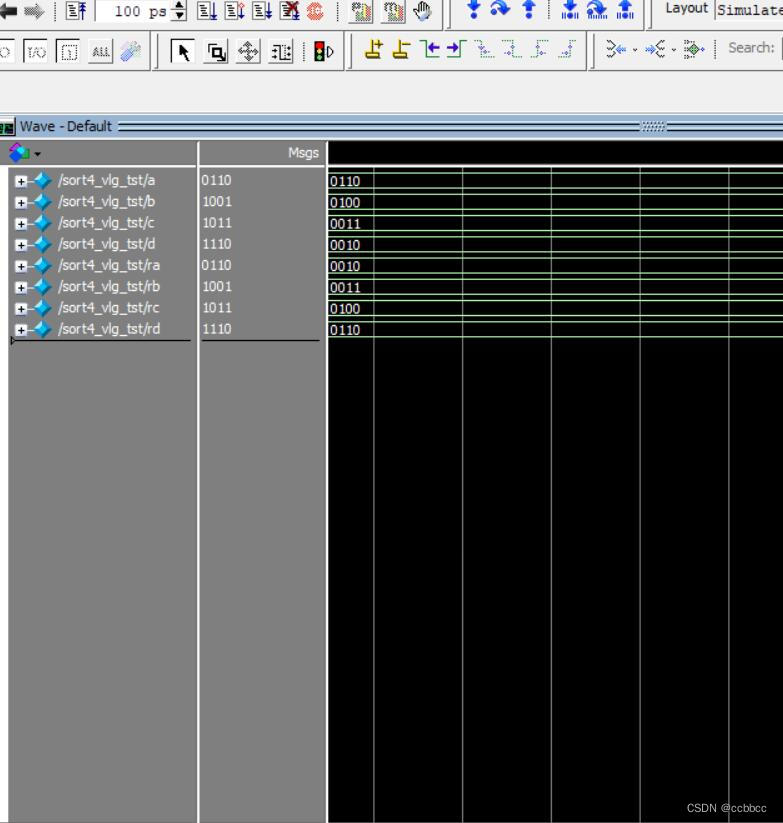

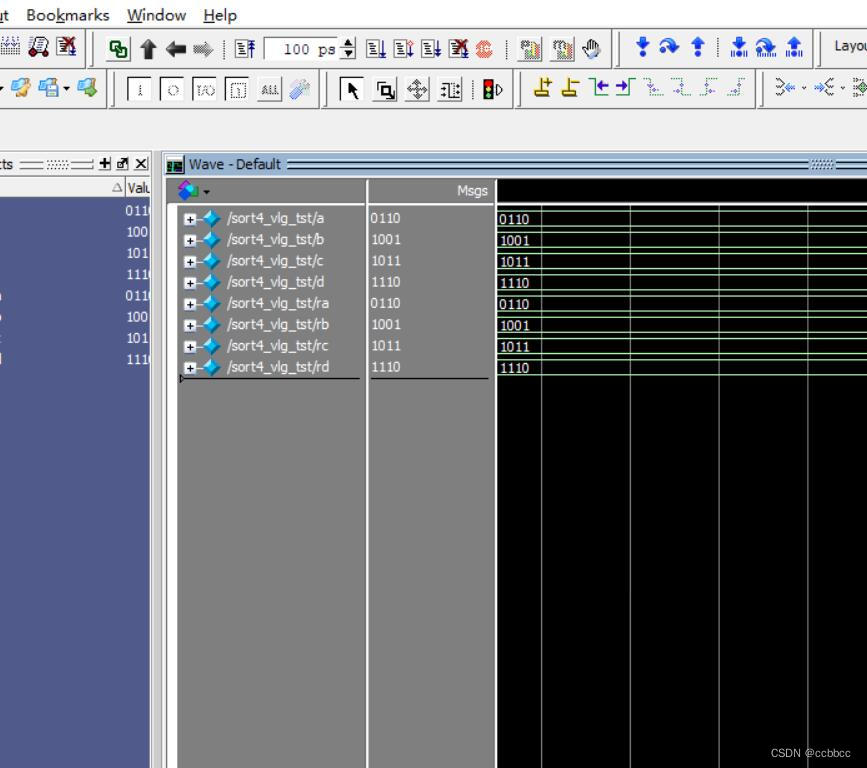

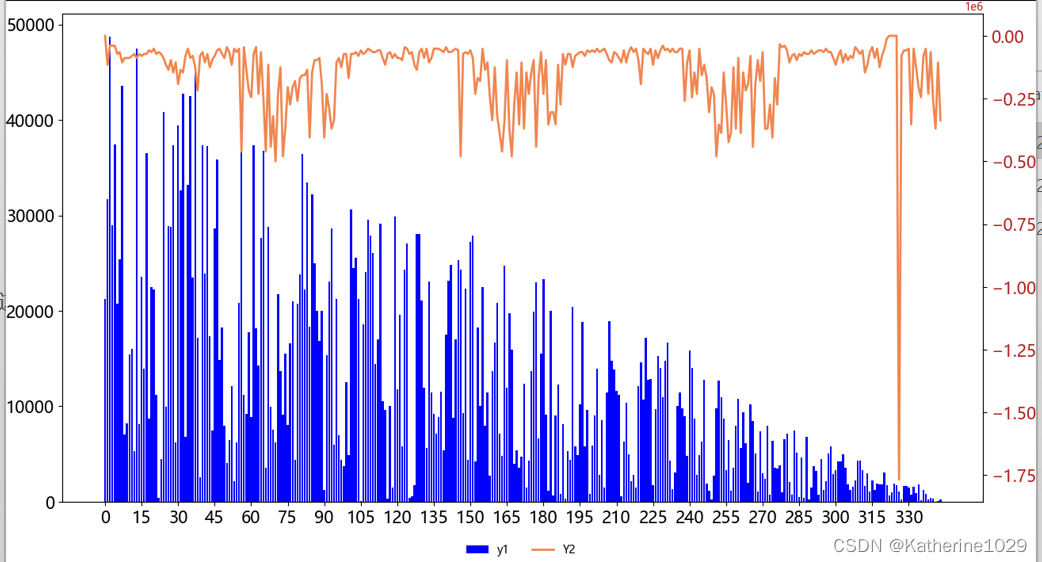

仿真排序