REVIEW

| 之前已经学习过: RAM: RAM IP核配置_ip核 ram配置-CSDN博客 串口接收:Vivado 串口接收优化-CSDN博客 串口发送:Vivado 串口通信(UART)------串口发送_vivado串口收发实验-CSDN博客 按键:基于状态机的按键消抖实现-CSDN博客 按键+串口发送实验_串口发按键值-CSDN博客 |

1. 今日摸鱼任务

| 小梅哥教材:02_【逻辑教程】基于HDL的FPGA逻辑设计与验证教程V3.4.pdf

15 搭建串口收发与存储双口 RAM 简易应用系统

|

| 实现:串口写入RAM,按键控制串口发送RAM中的数据 |

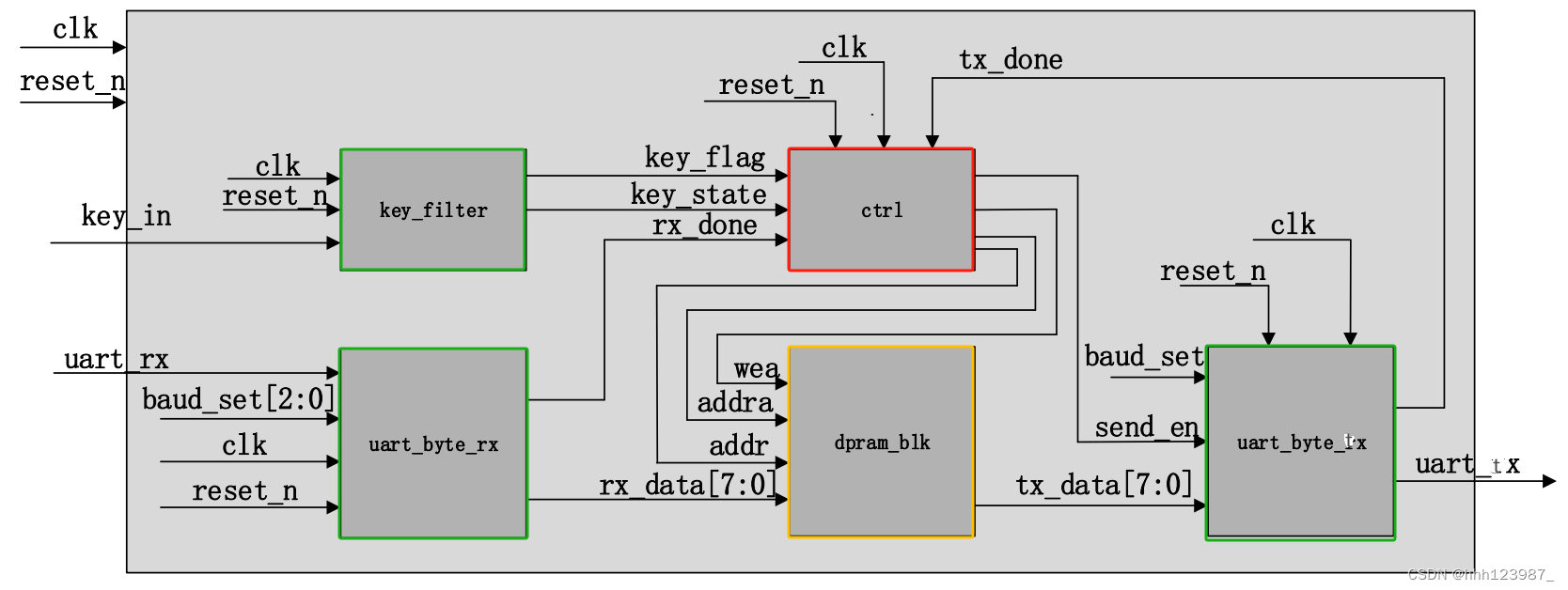

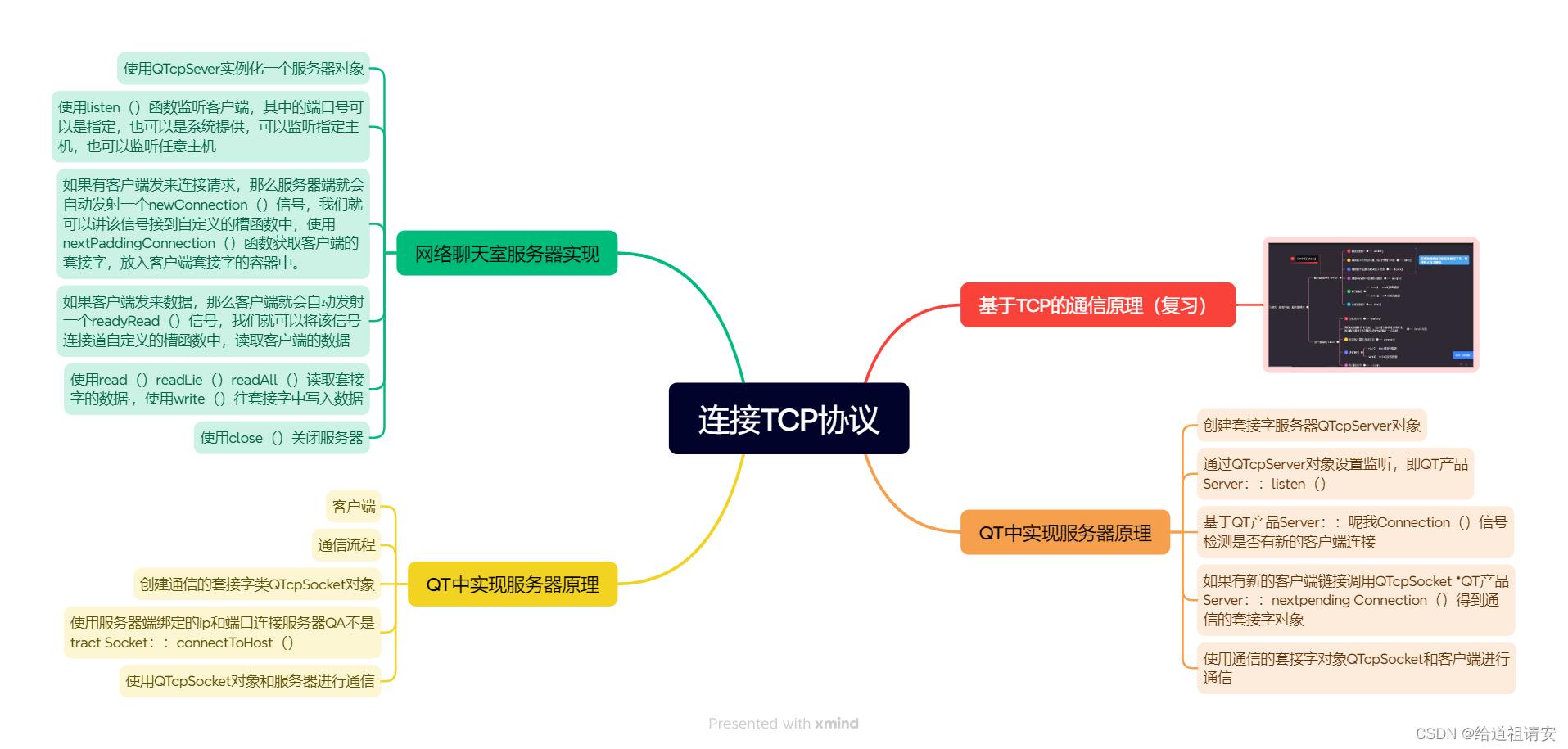

2. 系统框图

| 系统框图如下图: (其中baud_set[2:0],摸鱼怪是直接改的波特率) (俺下载的这版还有小错误嘎嘎嘎~右下角应该是串口发送tx) |

|

|

| 分析: 绿色:已封装好的模块 黄色:添加RAM IP核 红色ctrl:编写ctrl模块 总:写顶层 |

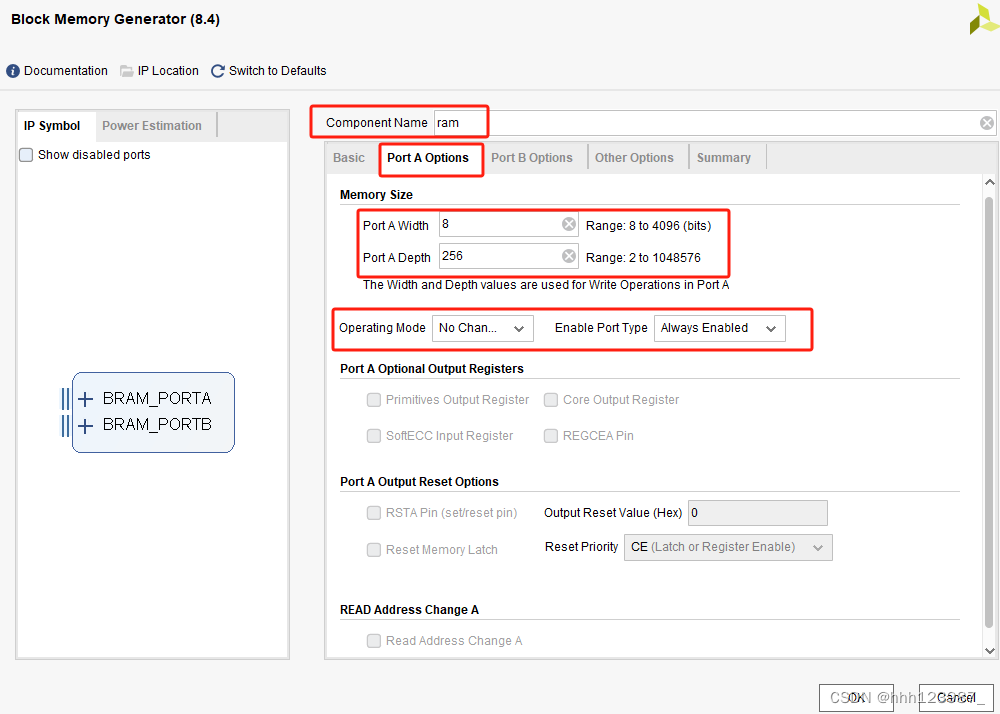

3. RAM配置

| RAM: RAM IP核配置_ip核 ram配置-CSDN博客 使用的是无ena 、enb第一版 |

|

|

|

|

|

4. RX + RAM

uartrx.v |

| 区别于之前的程序,使rx_data提前于rx_done一个clk |

| module uartrx( rx_data <= r_rx_data; |

rx_ram_00.v |

| module rx_ram_00( ram ram_ ( |

rx_tb.v |

| `timescale 1ns / 1ns module rx_tb(); reg clk , reset_n ; reg uart_rx; reg clkb; reg [7:0]addrb; wire [7:0]doutb; integer i; rx_ram_00 rx_ram_00_( . clk(clk) , . reset_n(reset_n) , . uart_rx(uart_rx) , . clkb(clkb) , . addrb(addrb) , . doutb(doutb) ); initial clk = 1 ; always #10 clk = ~clk ; initial clkb = 1 ; always #20 clkb = ~clkb ; initial begin reset_n = 0 ; uart_rx = 1 ; addrb = 255; i = 0 ; #201; reset_n = 1 ; #2000; // F0 1111_0000 uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); #200000; // 55 0101_0101 uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); #200000; // 55 0101_0101 uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); #200000; // F0 1111_0000 uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); #200000; // F0 1111_0000 uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); #200000; // 55 0101_0101 uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); #200000; // 55 0101_0101 uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); #200000; // F0 1111_0000 uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 0 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); uart_rx = 1 ; #(5208*20); #200000; for (i = 0 ; i < 8 ; i = i+1) begin addrb = i; #40; end addrb = 255; #2000; $stop; end endmodule |

|

|

|

|

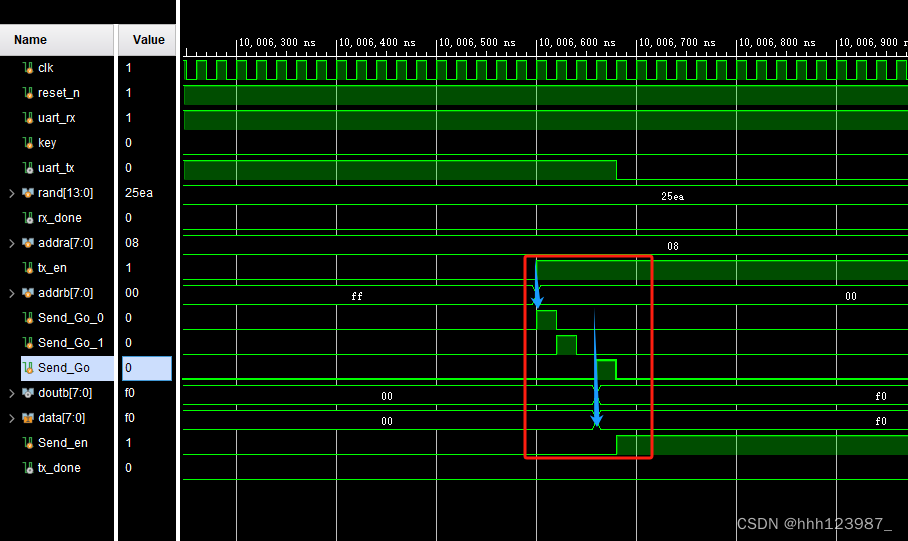

| 测试了向RAM中写入8个数据,并读出 |

| 由图可以看出串口写入模块正常 |

| 摸鱼怪碎碎念:之前 always@(posedge clk or negedge reset_n) always@(posedge clk) rx_data <= r_rx_data; 这两部分调试出来滴,之前没有连续传输过,so没注意到这个问题,嘿嘿嘿~ |

5. RX + RAM +Key + TX

key_one.v |

| module key_one( //测试的时候为了速度快一点调成这个,当然之前参数化有学习过应该咋做 //摸鱼怪是这样的(确信 //上板记得改回6个0 endmodule |

uarttx.v |

| module uarttx(input clk , |

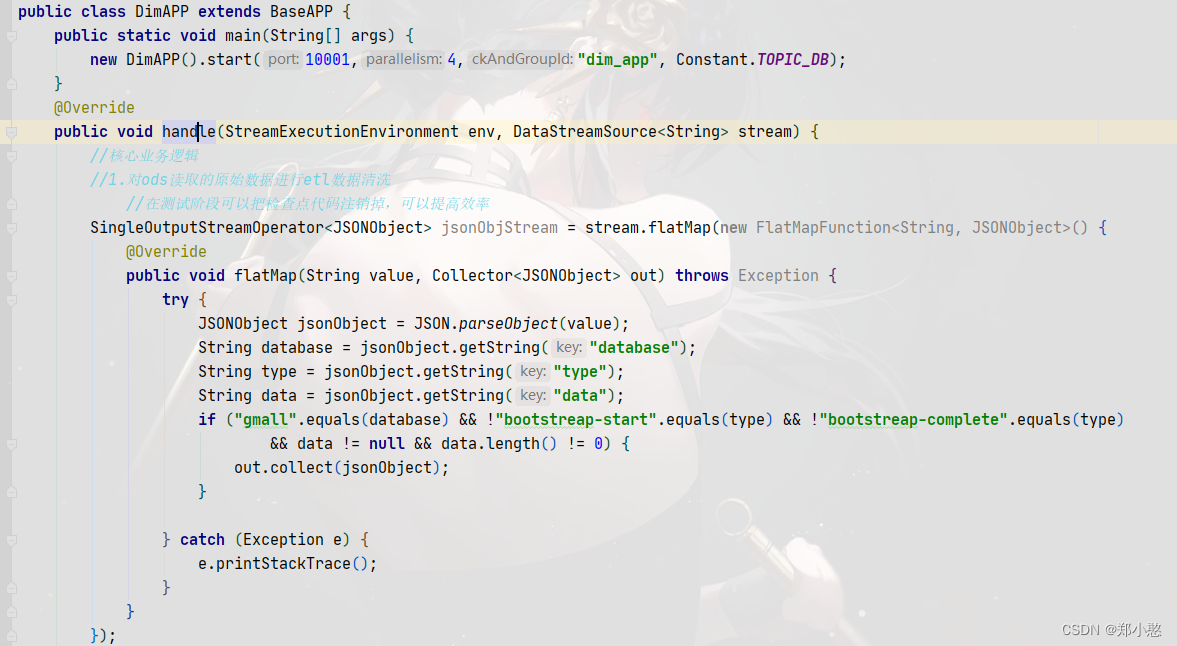

rx_ram_tx.v |

| module rx_ram_tx( //为什么跟addrb 同样的颜色捏~ |

rx_ram_key_tx_tb.v(第一版) |

| `timescale 1ns / 1ns module rx_ram_key_tx_tb( ); |

|

|

| 嘎嘎嘎~是不是觉得貌似没有问题~ 那为什么要说存在问题捏! 自行调试一下: always@(posedge clk or negedge reset_n) (俺这里没有保存,就是之前学习RAM读取,配置中存在一个Latentcy |

rx_ram_key_tx_tb.v(修改后) |

| module rx_ram_tx( //这部分是之前的Send_Go |

|

|

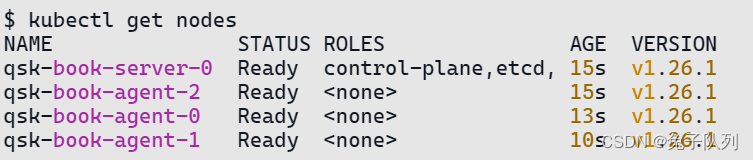

6. 板级验证

.xdc |

| set_property IOSTANDARD LVCMOS33 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports key] set_property IOSTANDARD LVCMOS33 [get_ports reset_n] set_property IOSTANDARD LVCMOS33 [get_ports uart_rx] set_property IOSTANDARD LVCMOS33 [get_ports uart_tx] set_property PACKAGE_PIN U18 [get_ports clk] set_property PACKAGE_PIN H18 [get_ports key] set_property PACKAGE_PIN H20 [get_ports reset_n] set_property PACKAGE_PIN K16 [get_ports uart_rx] set_property PACKAGE_PIN J16 [get_ports uart_tx] |

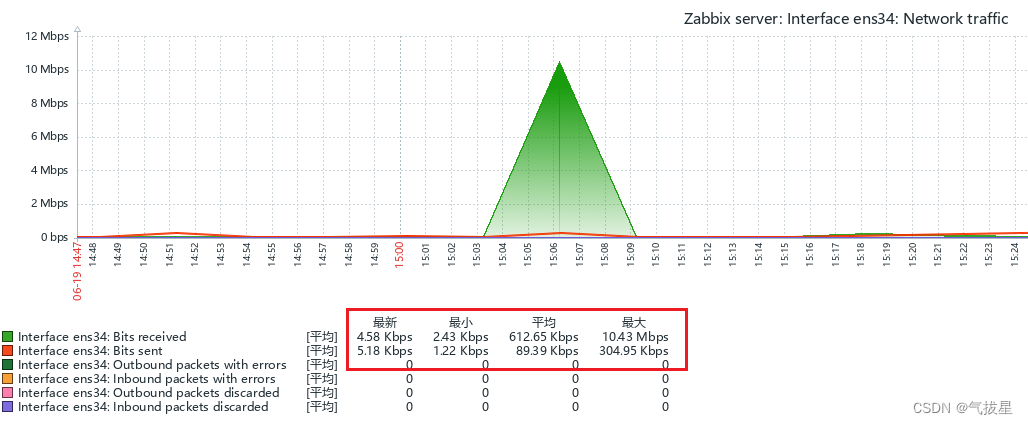

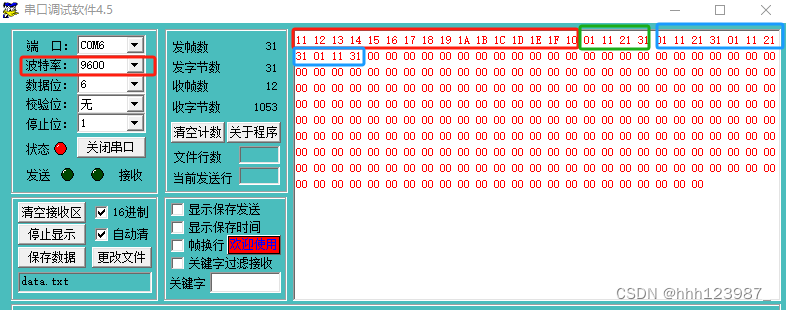

| 依次向RAM中写入:0x10~0x1F(一开始把0忘记哩~)读取到的数值是正确的 但是写入:0x01~0xF1 可以看出,最高两位的数据一直为0 |

|

| 存在的小错误下次继续调试叭~ 摸鱼怪跑路~ |