文章目录

- 一、HLS介绍

- 1.1 什么是HLS

- 1.2HLS与VHDL/Verilog编程技术有什么关系?

- 1.3HLS的关键技术和技术局限性

- 1.3.1关键技术

- 1.3.2 技术局限性

- 二、HLS入门实验

- 2.1安装Vivado

- 2.2创建项目

- 2.3添加文件

- 2.4仿真

- 2.5创建Vivado工程

- 2.6生成IP核

- 2.7添加代码

- 参考

一、HLS介绍

1.1 什么是HLS

高层次综合(High-level Synthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。所谓的高层次语言,包括C、C++、SystemC等,通常有着较高的抽象度,并且往往不具有时钟或时序的概念。

1.2HLS与VHDL/Verilog编程技术有什么关系?

VHDL(VHSIC Hardware Description Language)和 Verilog 是两种常见的硬件描述语言,用于描述数字电路的结构和行为。设计人员通常会使用这两种语言来描述硬件电路的功能、时序和结构,然后将其综合为最终的硬件实现。因此,HLS 技术可以将高级编程语言转换为 VHDL/Verilog 代码,进而实现硬件功能的描述和实现。总的来说,HLS 可以与 VHDL/Verilog 结合使用,从而提高硬件设计的效率和灵活性。

1.3HLS的关键技术和技术局限性

1.3.1关键技术

- 高级别算法描述

- 自动化综合

- 并行化和流水线

- 时序分析和约束

- 优化技术

- 仿真和验证

1.3.2 技术局限性

- 复杂性转换难题

- 性能不确定性

- 资源利用效率

- 时序约束挑战

- 功耗优化困难

- 难以调试和测试

二、HLS入门实验

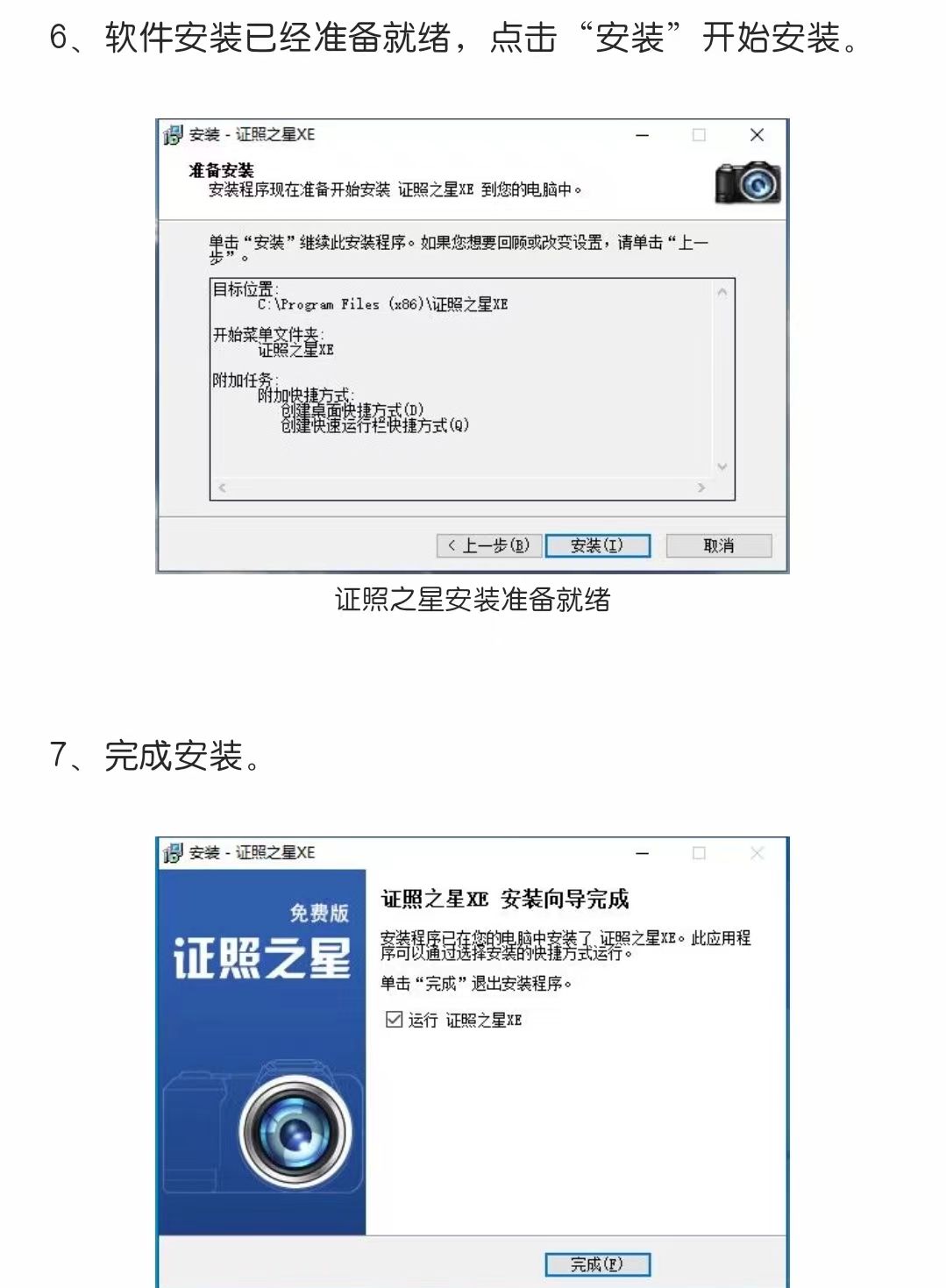

2.1安装Vivado

下载安装:参考博客

2.2创建项目

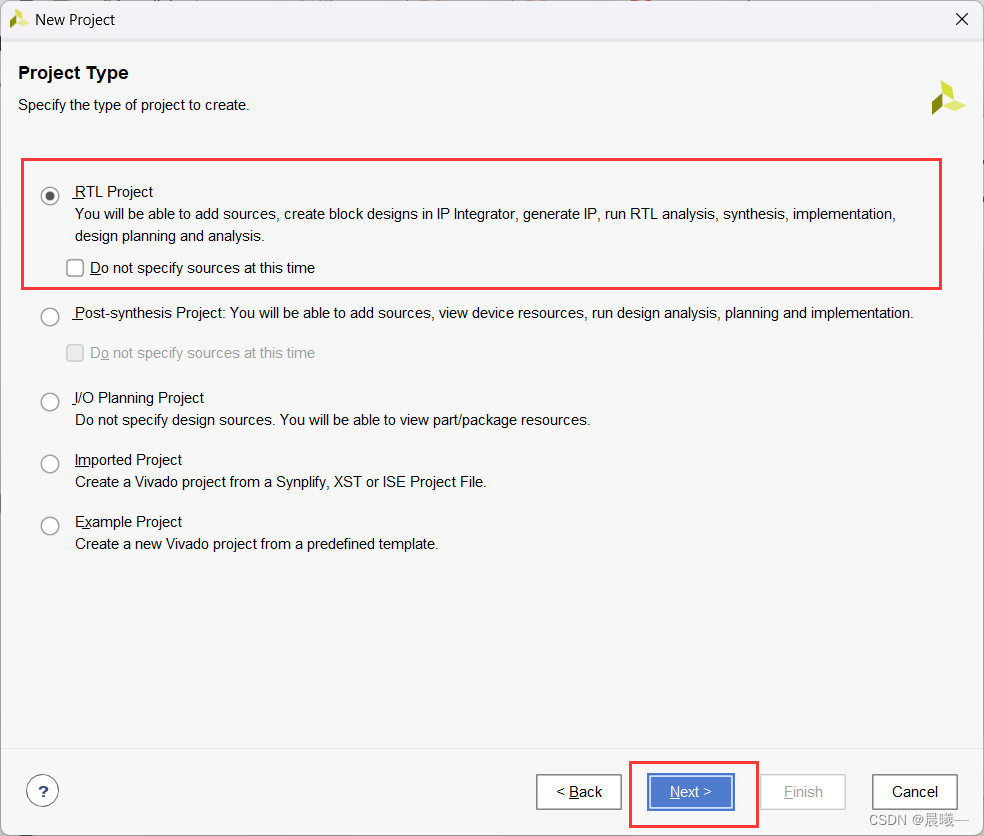

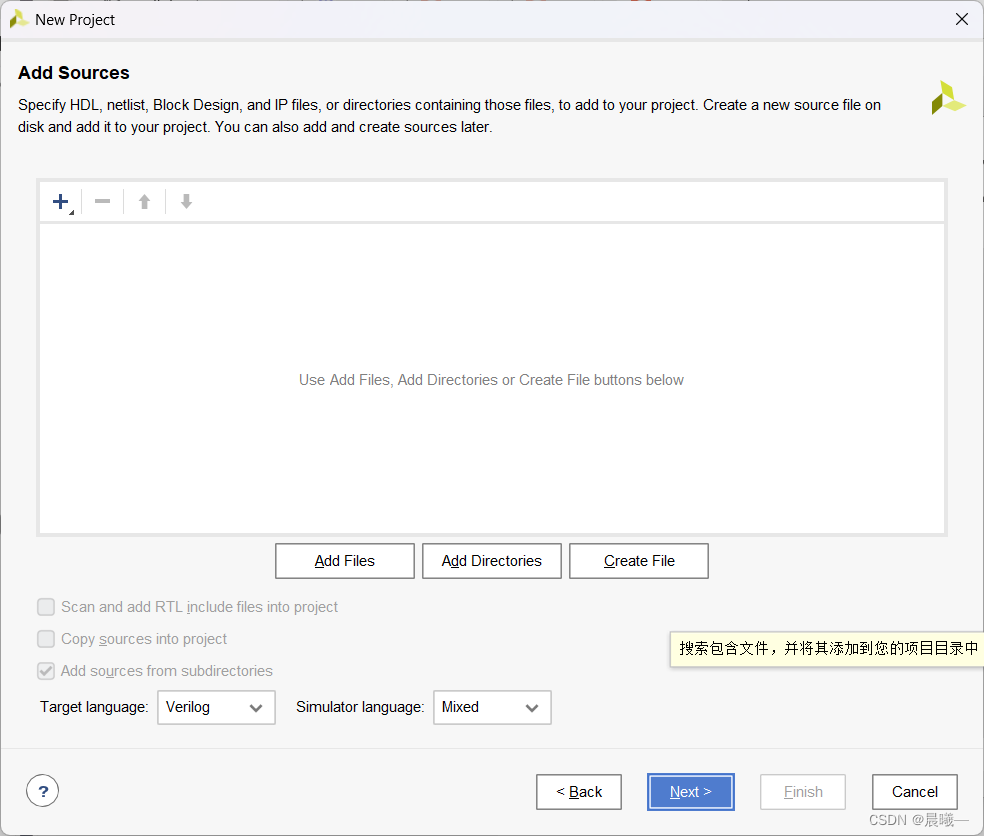

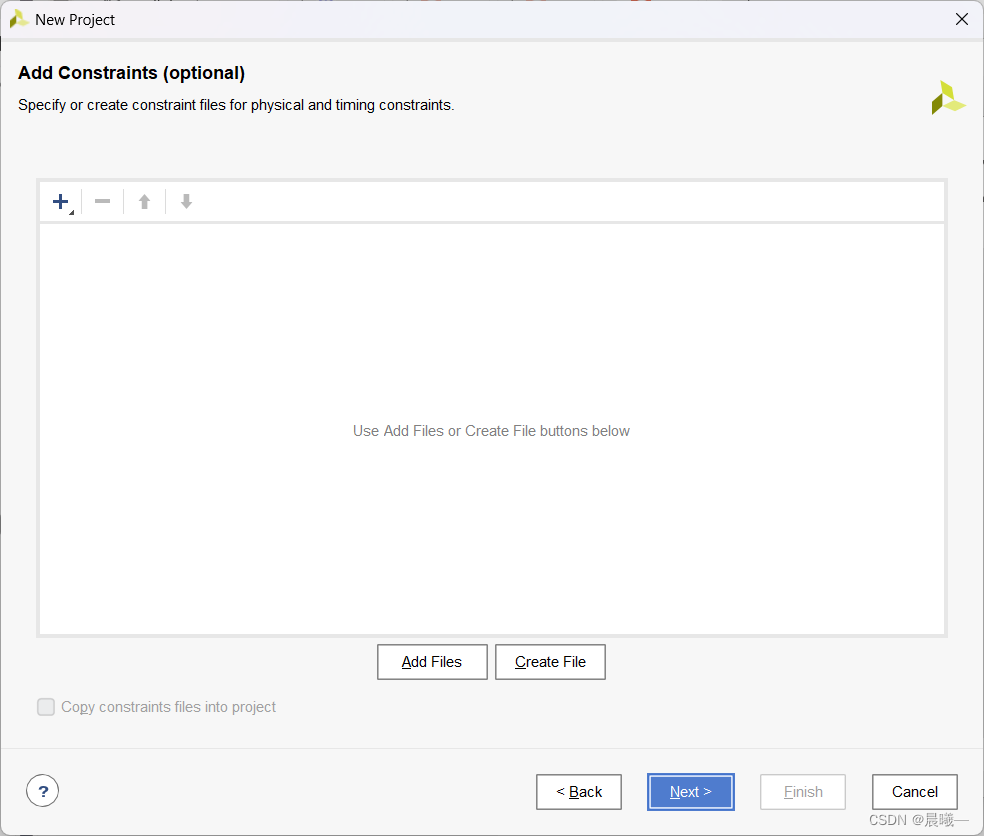

打开Vivado

设置名称

next

next

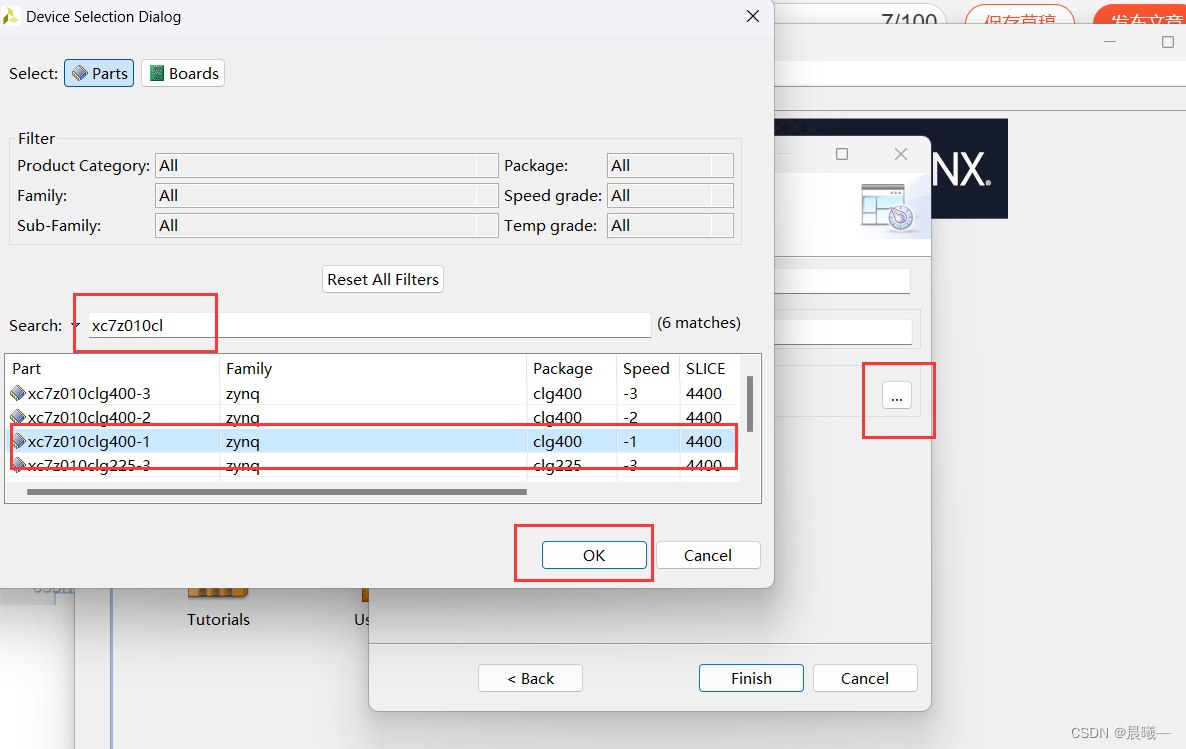

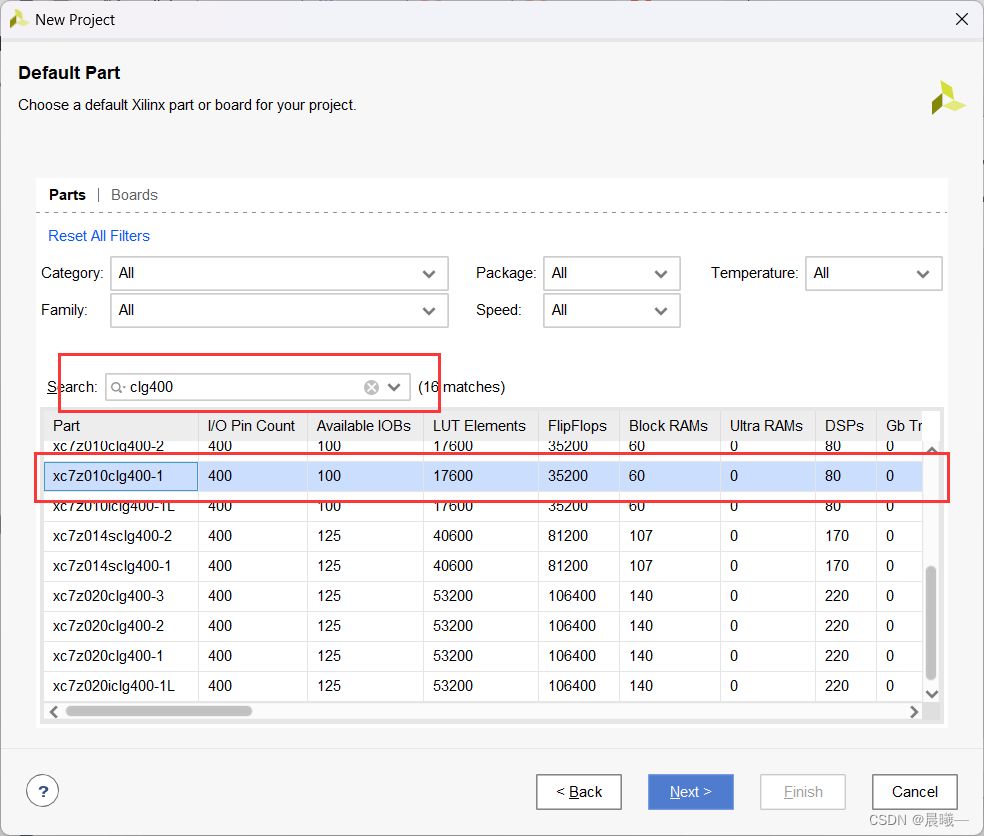

选择器件

finish

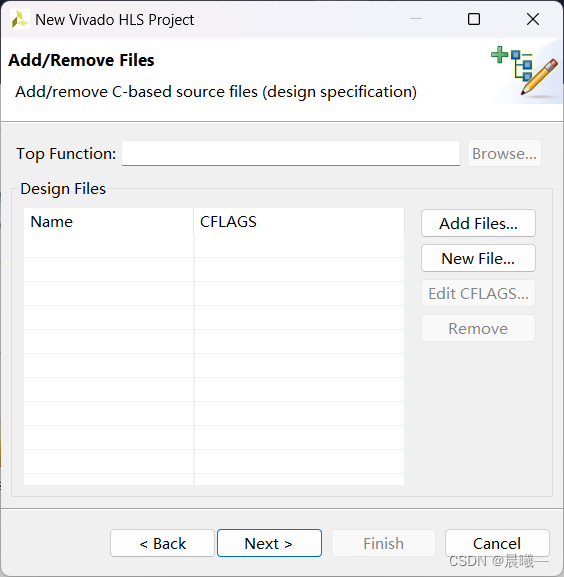

2.3添加文件

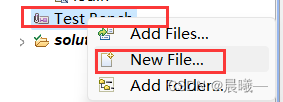

创建文件

led.h

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#include "ap_int.h"

#define CNT_MAX 100000000

//#define CNT_MAX 100,100M时钟频率下计数一秒钟所需要的计数次数

#define FLASH_FLAG CNT_MAX-2

// typedef int led_t;

// typedef int cnt_t;

typedef ap_int<1> led_t;

typedef ap_int<32> cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

led.cpp

#include "led.h"

void flash_led(led_t *led_o , led_t led_i){

#pragma HLS INTERFACE ap_vld port=led_i

#pragma HLS INTERFACE ap_ovld port=led_o

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}

}

添加测试文件

test_led.cpp

#include "led.h"

#include <stdio.h>

int main(){

led_t led_i=0x01;

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o , led_i);

led_i = led_o;

printf("shift_out is %d \n",(int)(led_o&0x01));

}

}

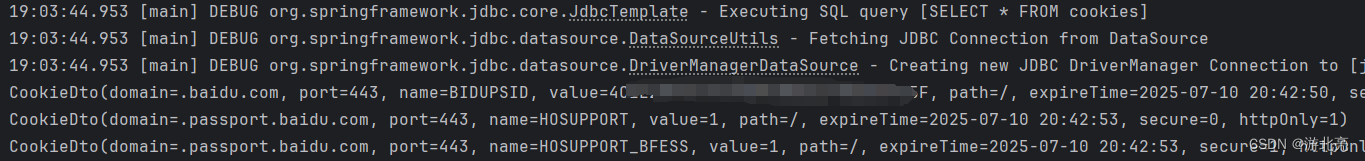

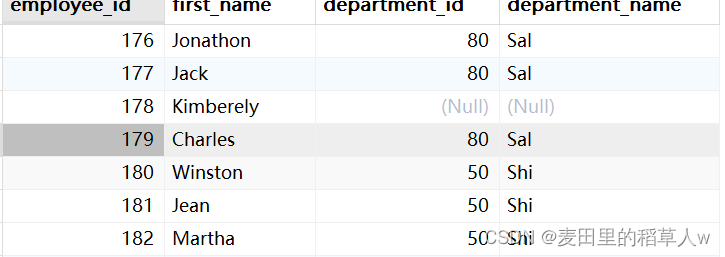

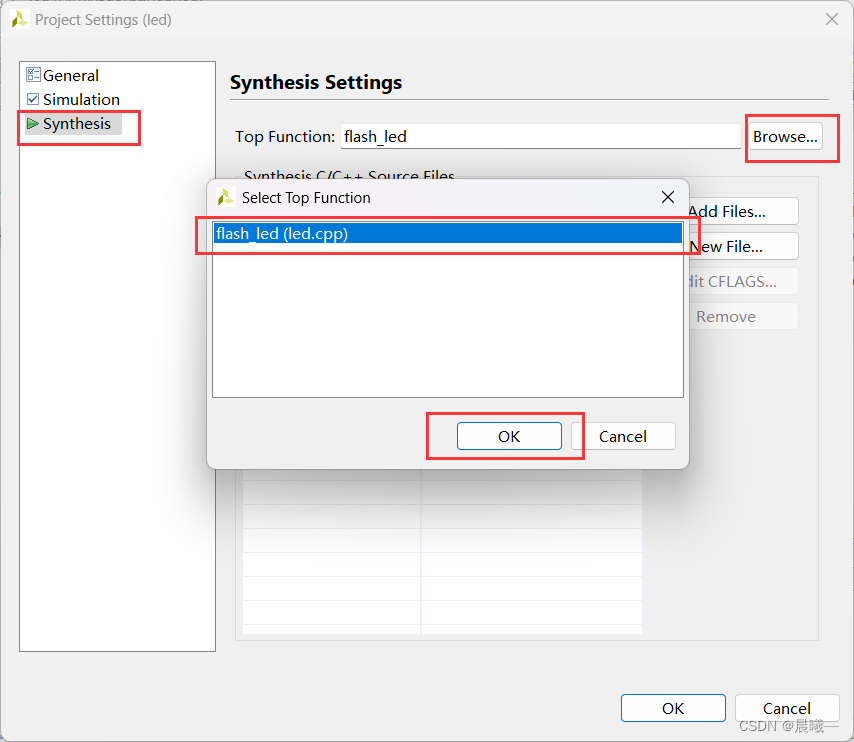

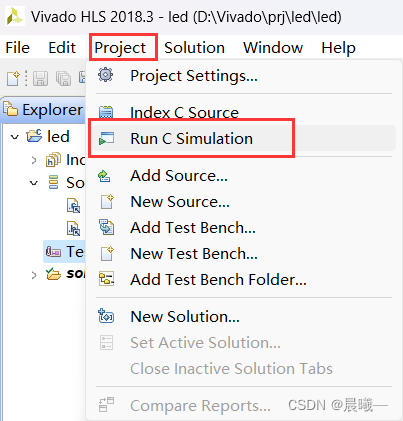

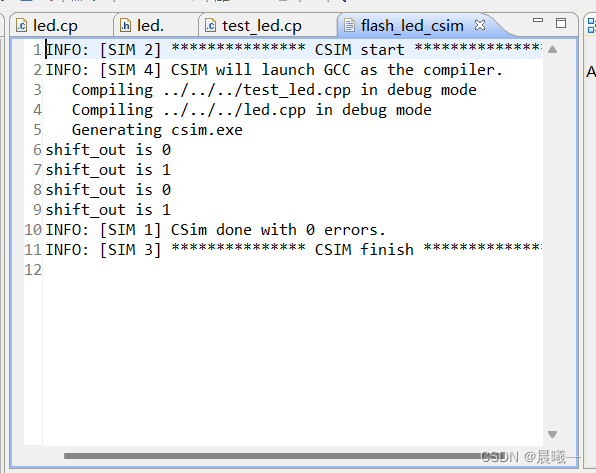

2.4仿真

运行

等待一会后,可以看见该界面出现0101交替

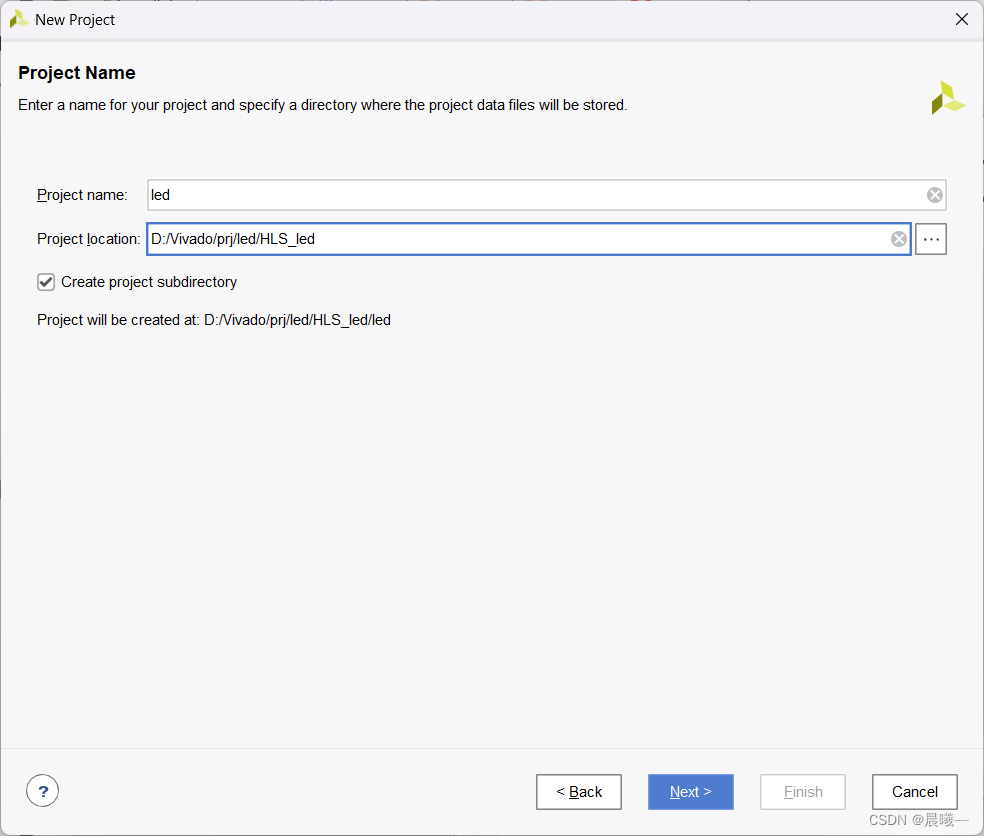

2.5创建Vivado工程

先不管next

next

选择器件

next->finish

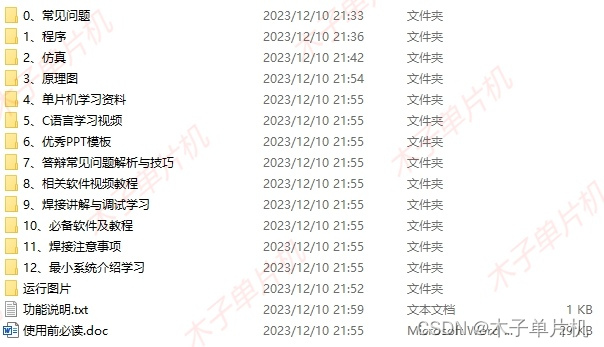

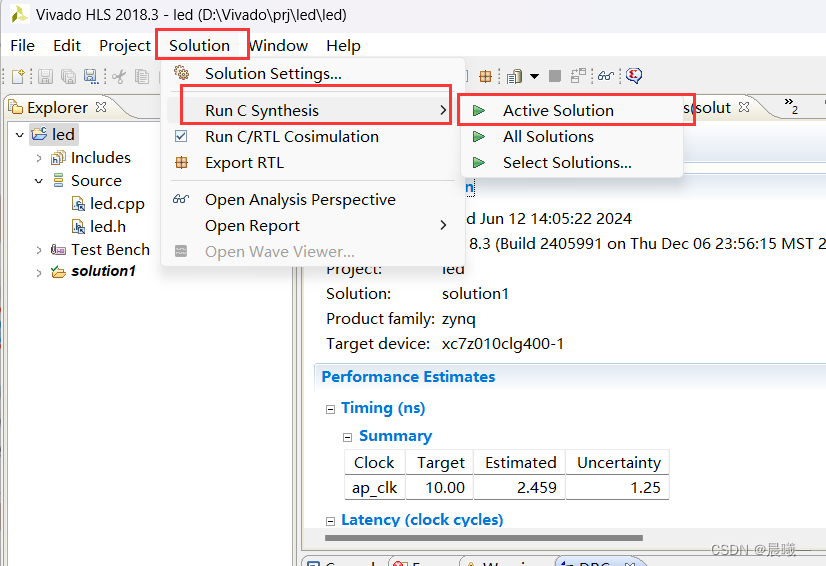

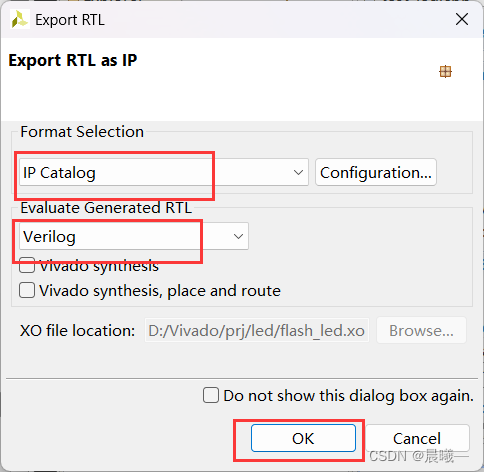

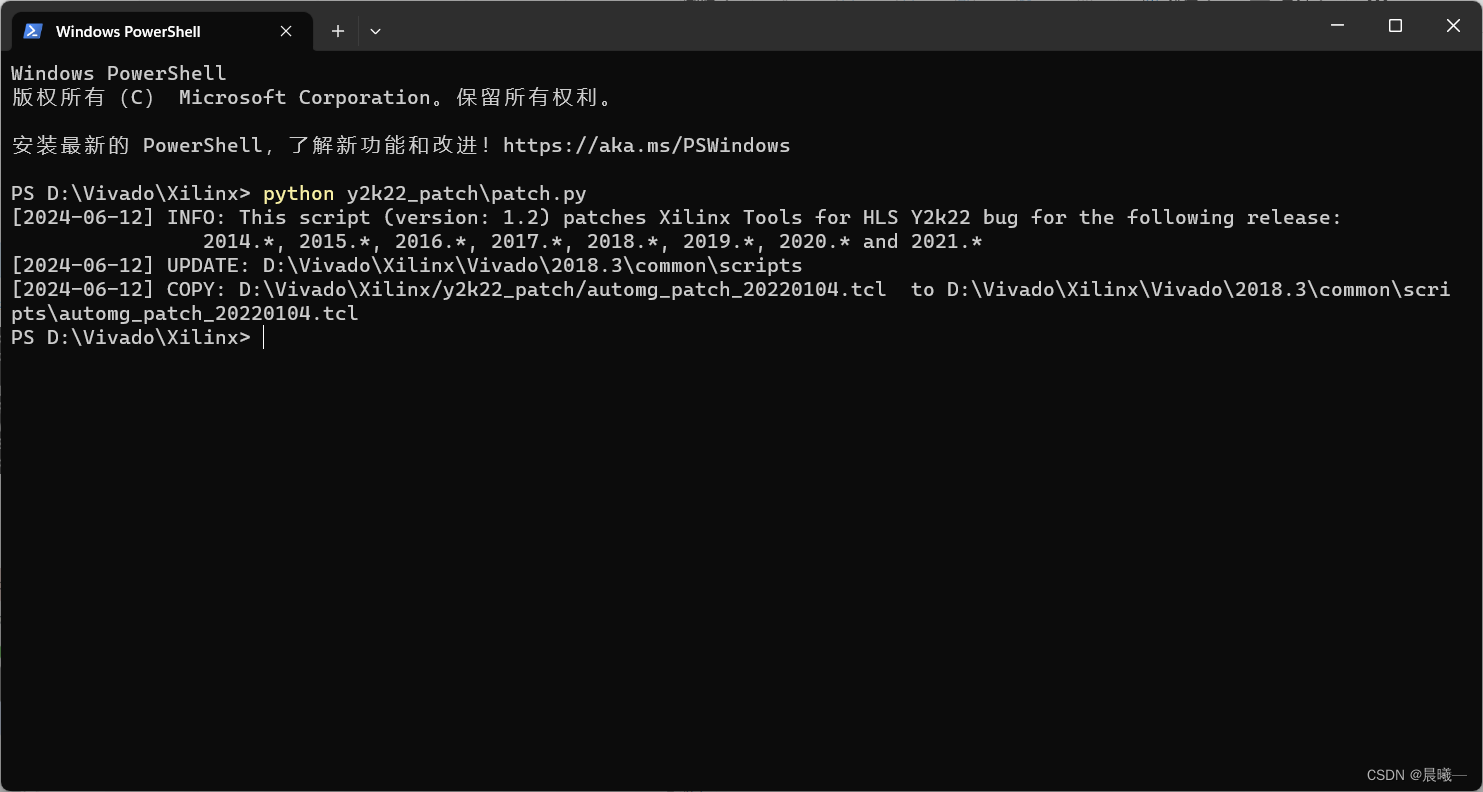

2.6生成IP核

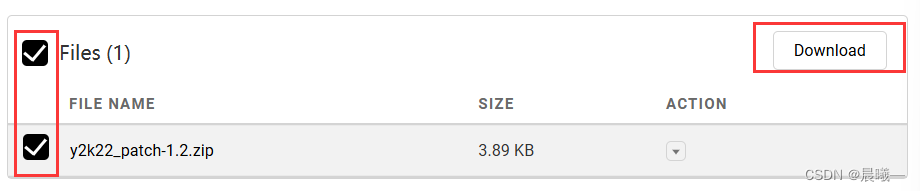

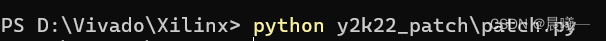

出现报错,前往官网下载补丁

https://support.xilinx.com/s/article/76960?language=en_US

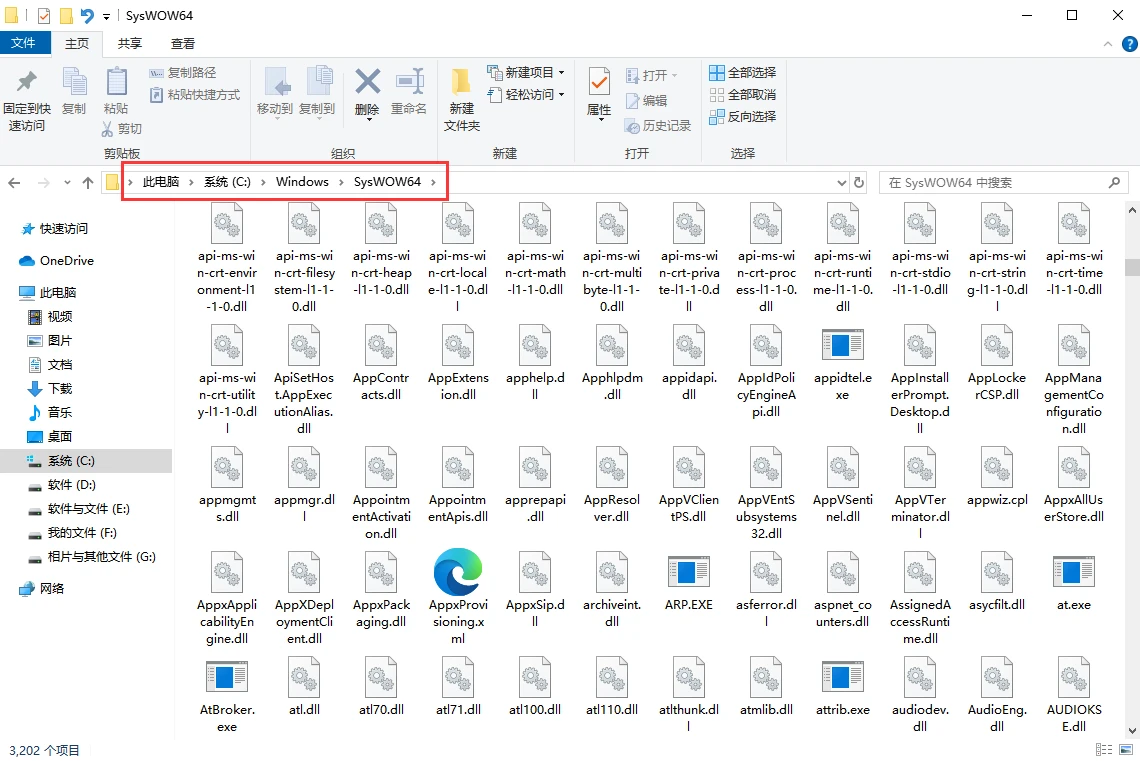

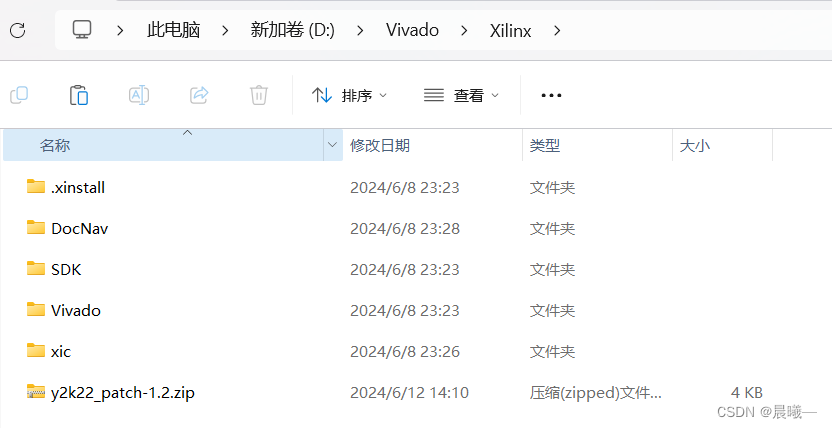

解压到该位置

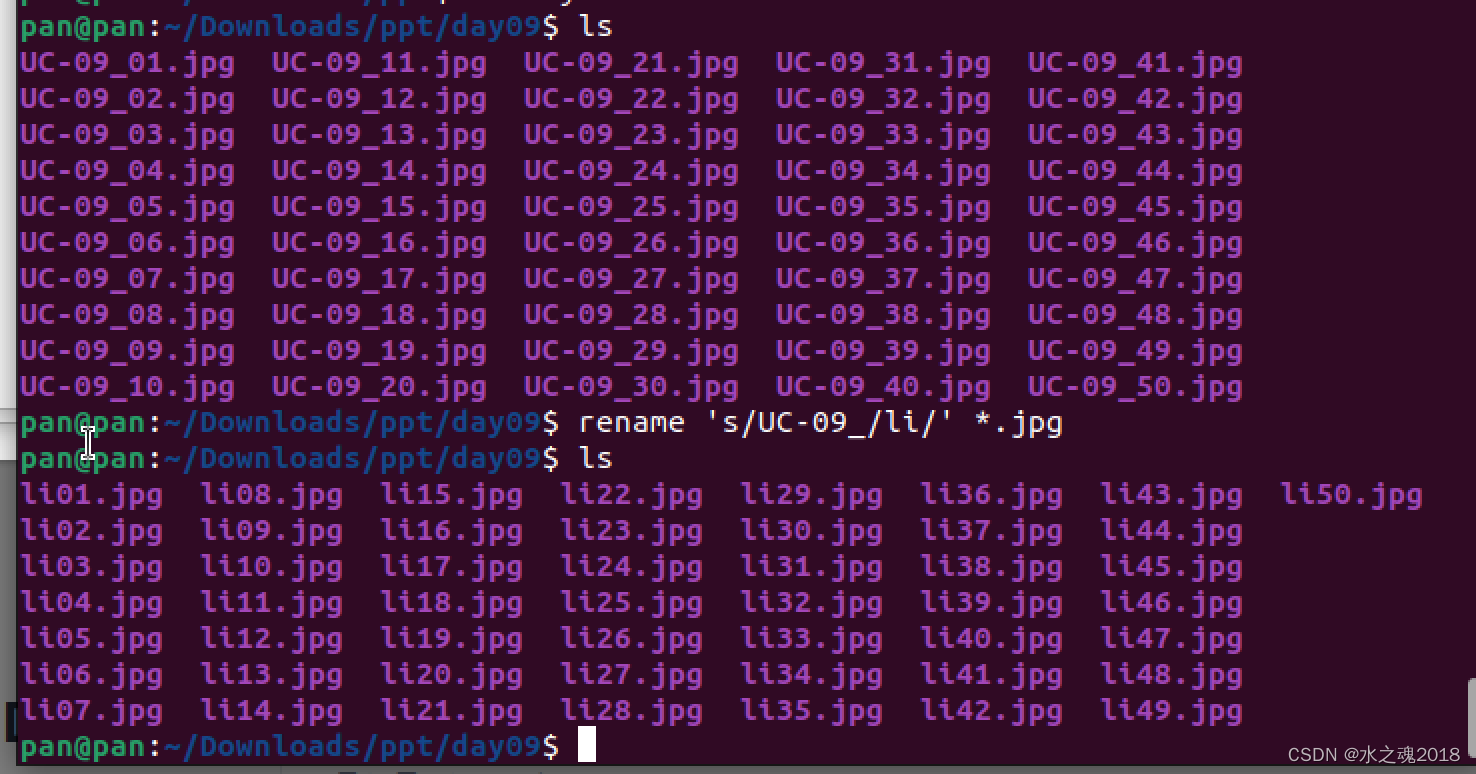

运行之前检查是否有python环境,如果没有

安装:参考博客

打开cmd,进入该目录,执行命令 python y2k22_patch\patch.py

然后再生成,没有报错信息

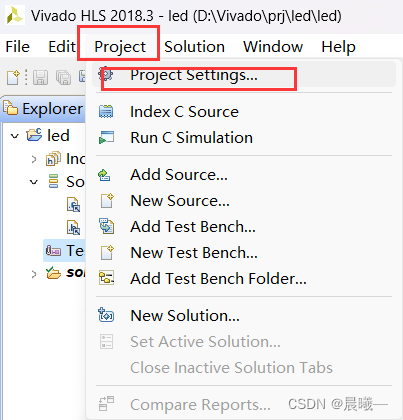

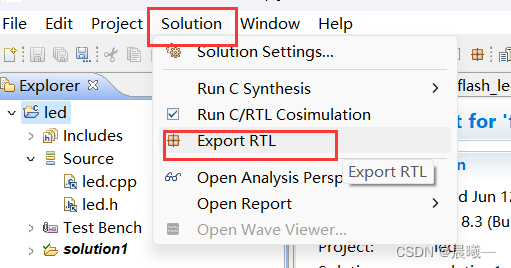

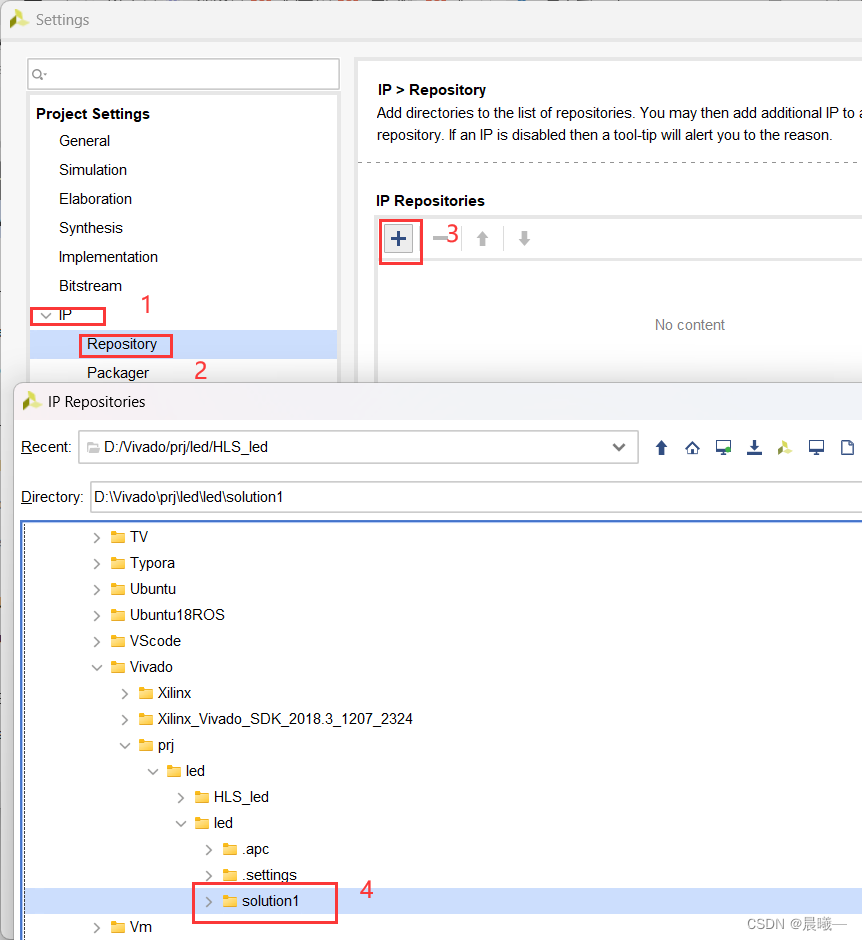

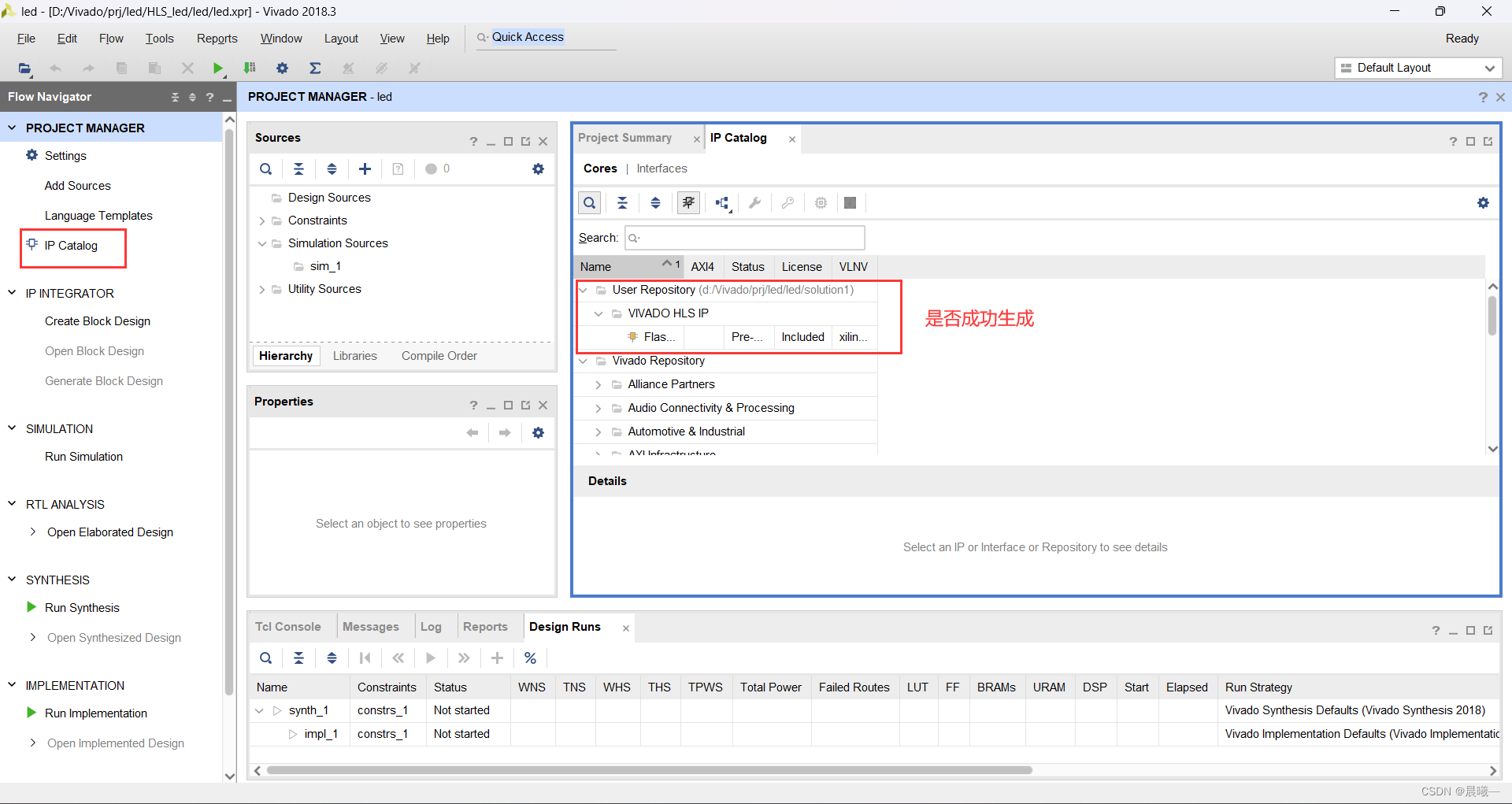

导入,先点击settings

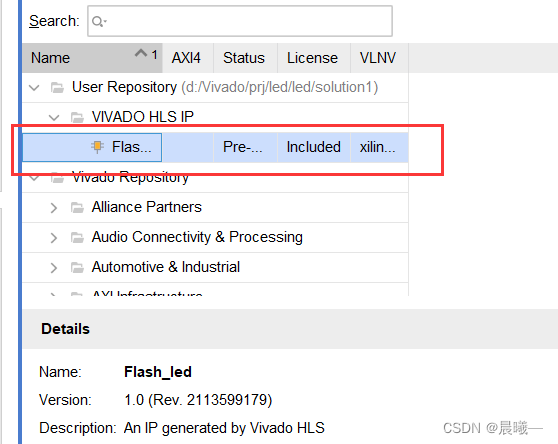

生成IP,双击进入

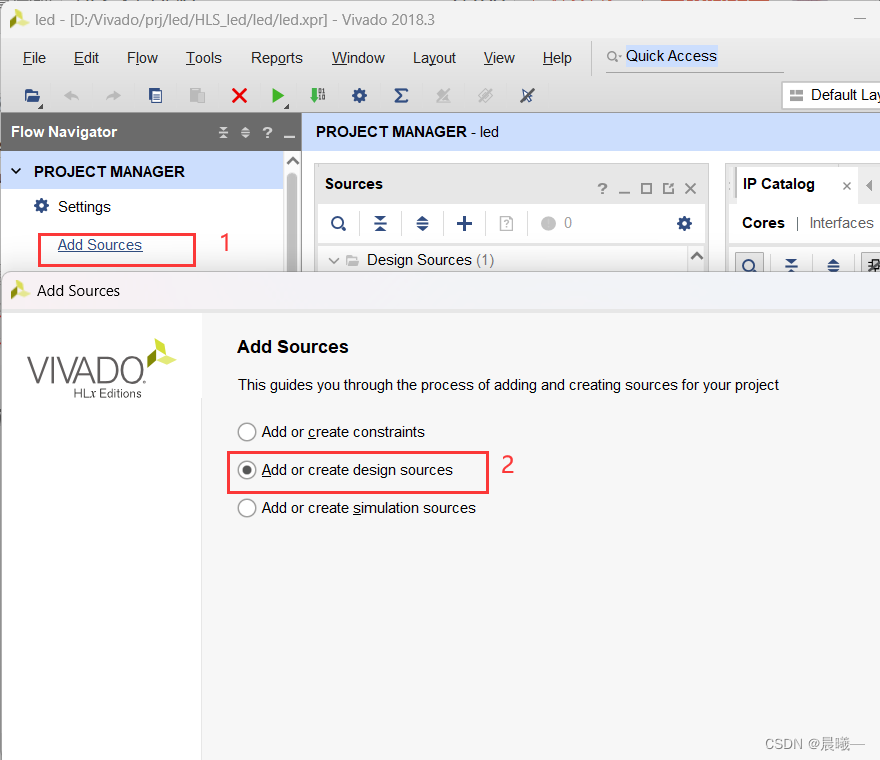

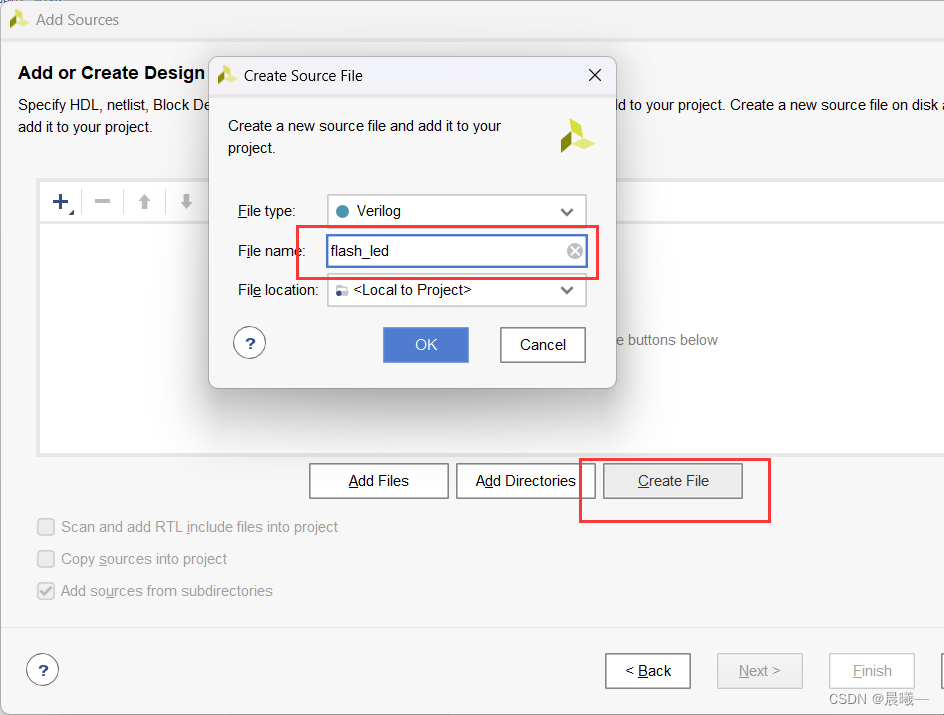

2.7添加代码

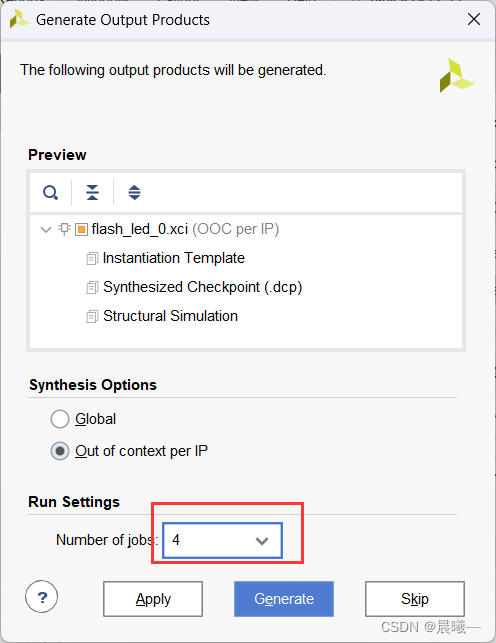

点击ok->finish,默认选择

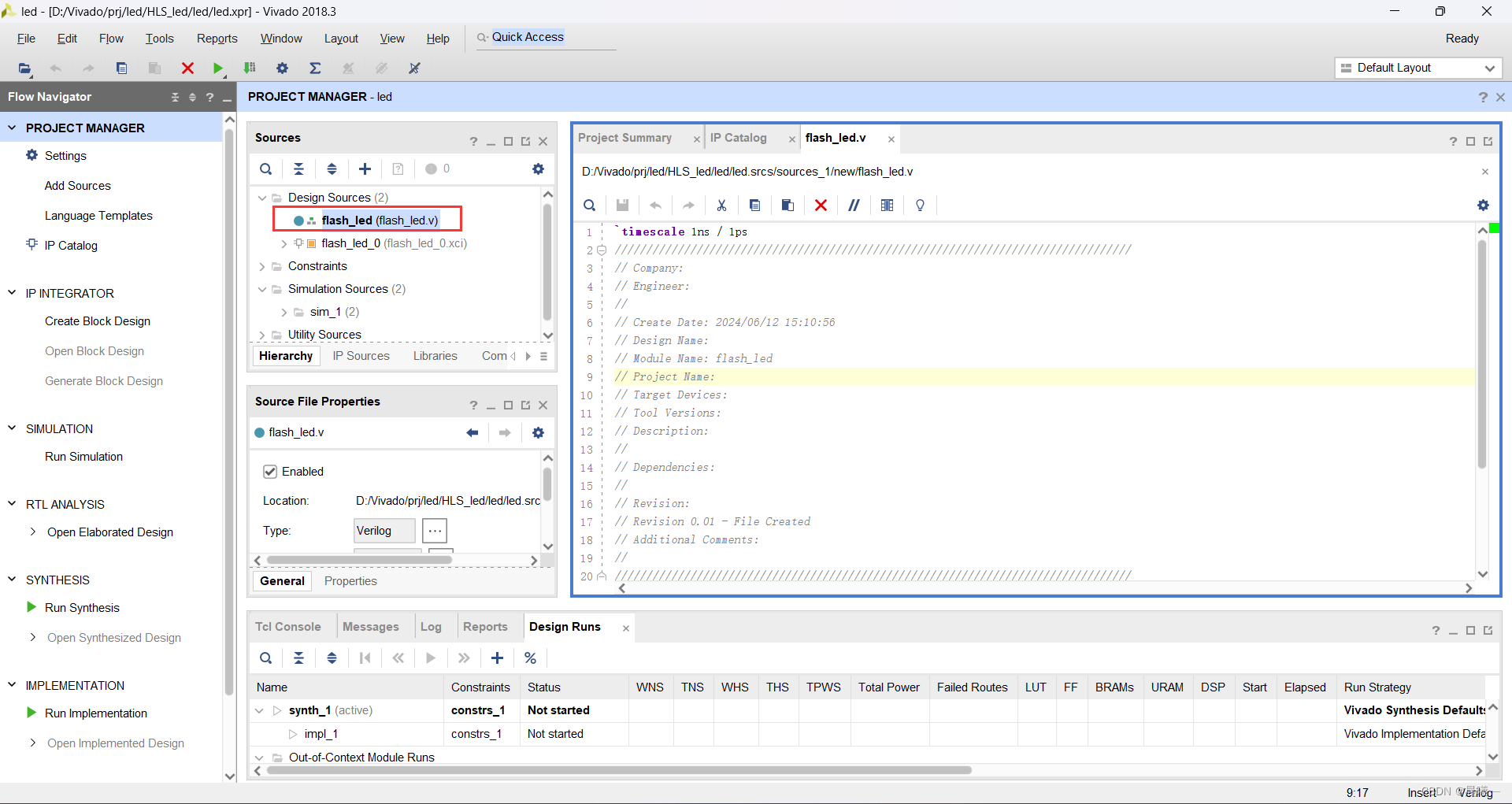

点击后写入代码内容

代码内容:

`timescale 1ns / 1ps

module flash_led(

input wire clk ,

input wire rst_n ,

output wire led_o

);

wire rst ;//同步复位

wire ap_ready ;//当前可以接收下一次数据

reg ap_start ;//IP 开始工作

reg led_i_vld ;//输入数据有效

wire led_o_vld ;

reg led_i ;//输入的 led 信号

wire led_o_r ;

wire ap_done ;

wire ap_idle ;

reg [1:0] delay_cnt ;

assign rst = ~rst_n ;

assign led_o = led_o_r ;

//----------------delay_cnt------------------

always @(posedge clk) begin

if (rst==1'b1) begin

delay_cnt <= 'd0;

end

else if(delay_cnt[1]==1'b0) begin

delay_cnt <= delay_cnt + 1'b1;

end

end

//----------------ap_start------------------

always @(posedge clk) begin

if (rst==1'b1) begin

ap_start <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

ap_start <= 1'b1;

end

end

//----------------led_i_vld------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i_vld <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

led_i_vld <= 1'b1;

end

end

//----------------ap_i------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i <= 1'b0;

end

else if(led_o_vld==1'b1)begin

led_i <= led_o_r ;

end

end

flash_led_0 inst_flash_led (

.led_o_V_ap_vld(led_o_vld), // output wire led_o_V_ap_vld

.led_i_V_ap_vld(led_i_vld), // input wire led_i_V_ap_vld

.ap_clk(clk), // input wire ap_clk

.ap_rst(rst), // input wire ap_rst

.ap_start(ap_start), // input wire ap_start

.ap_done(ap_done), // output wire ap_done

.ap_idle(ap_idle), // output wire ap_idle

.ap_ready(ap_ready), // output wire ap_ready

.led_o_V(led_o_r), // output wire [0 : 0] led_o_V

.led_i_V(led_i) // input wire [0 : 0] led_i_V

);

endmodule

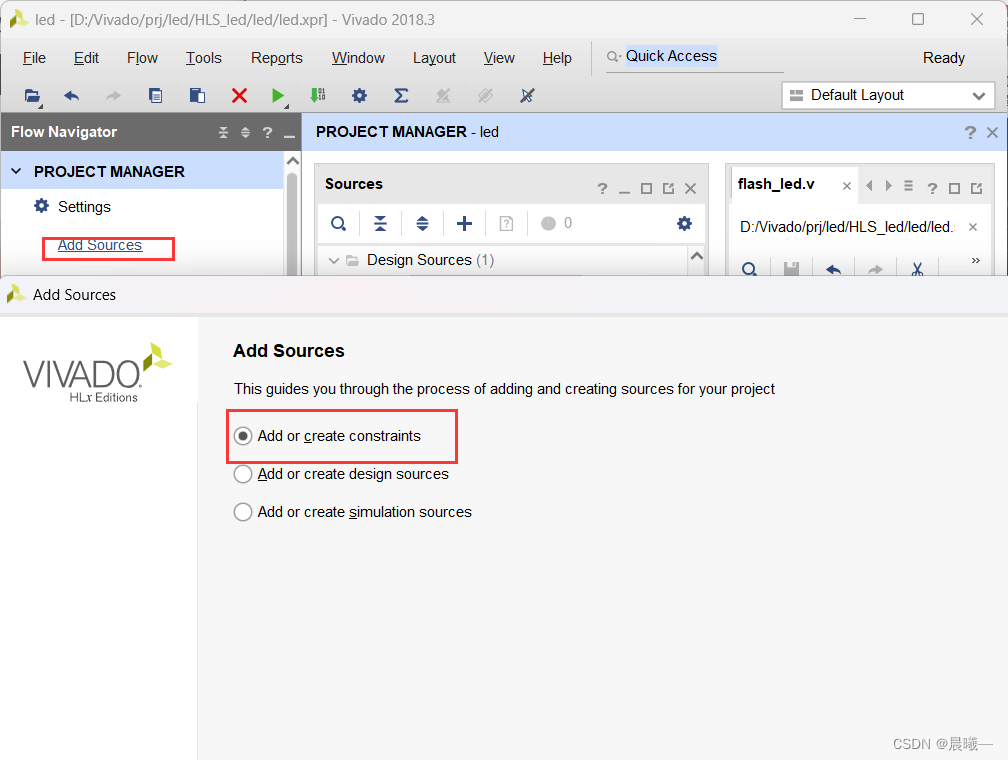

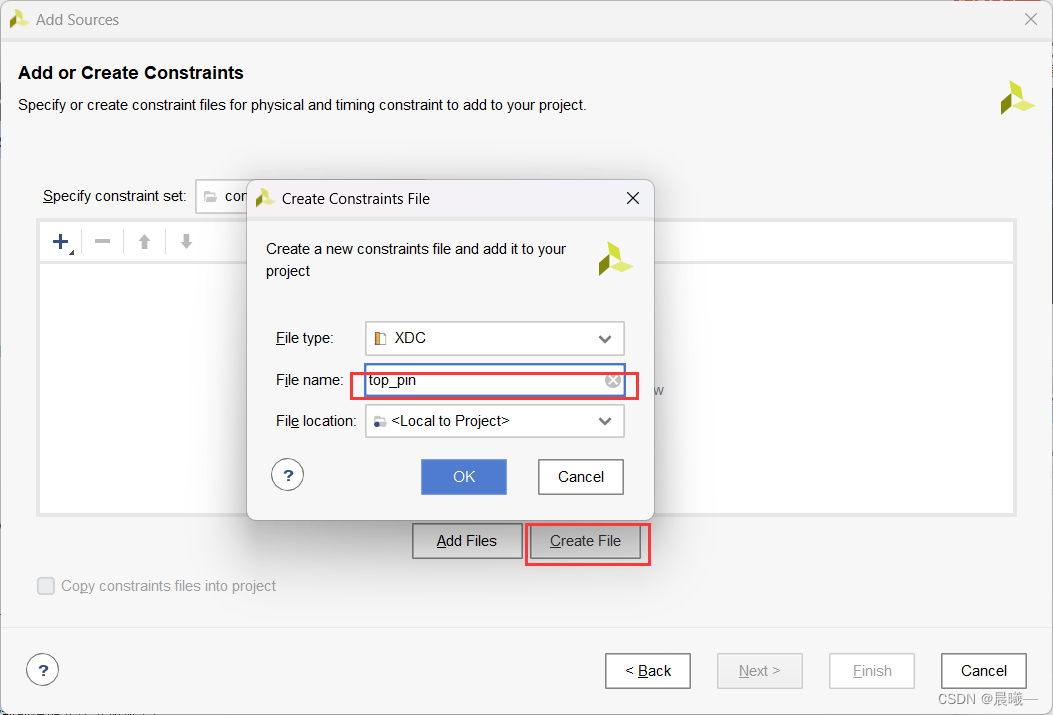

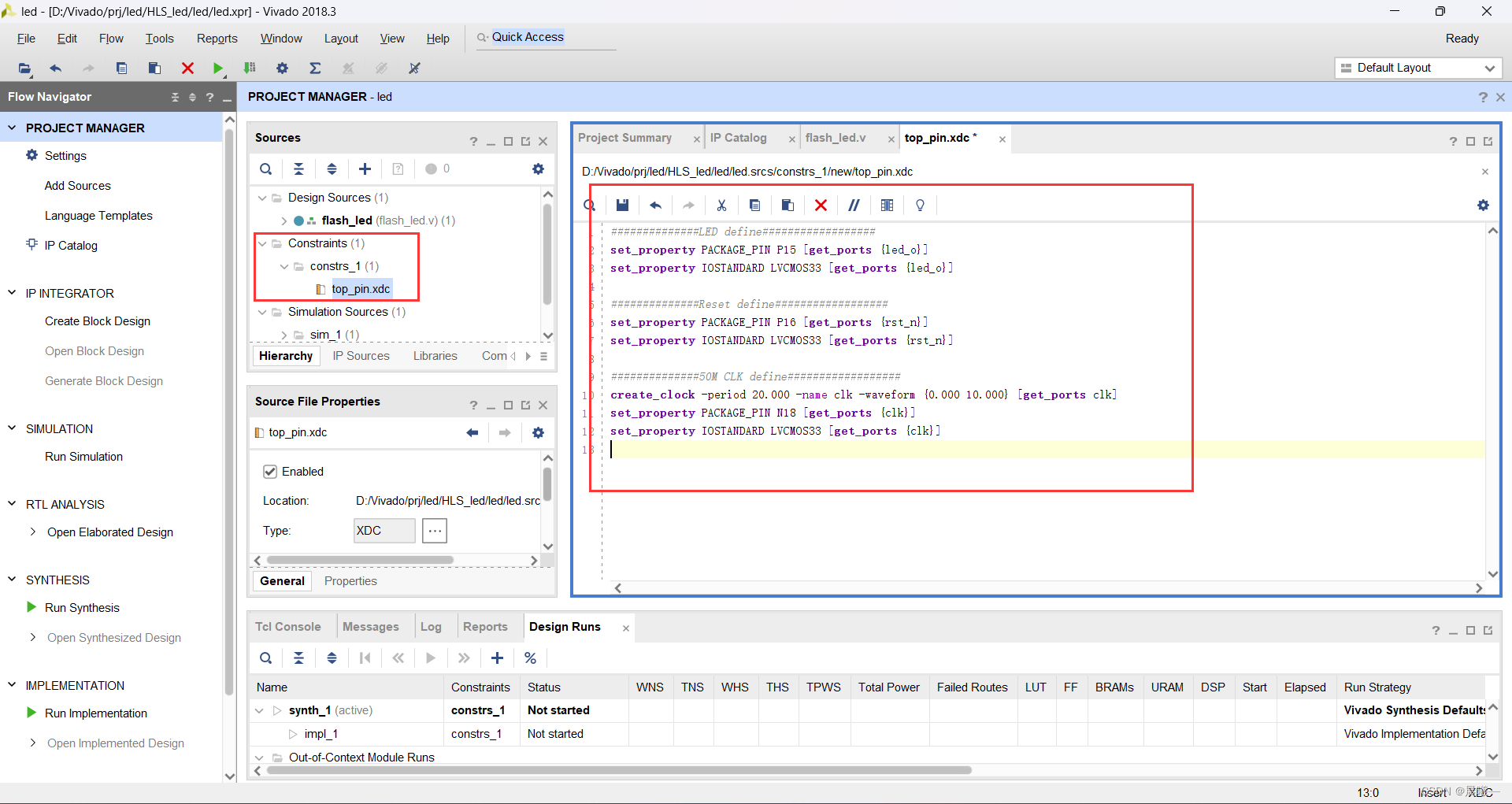

创建约束文件

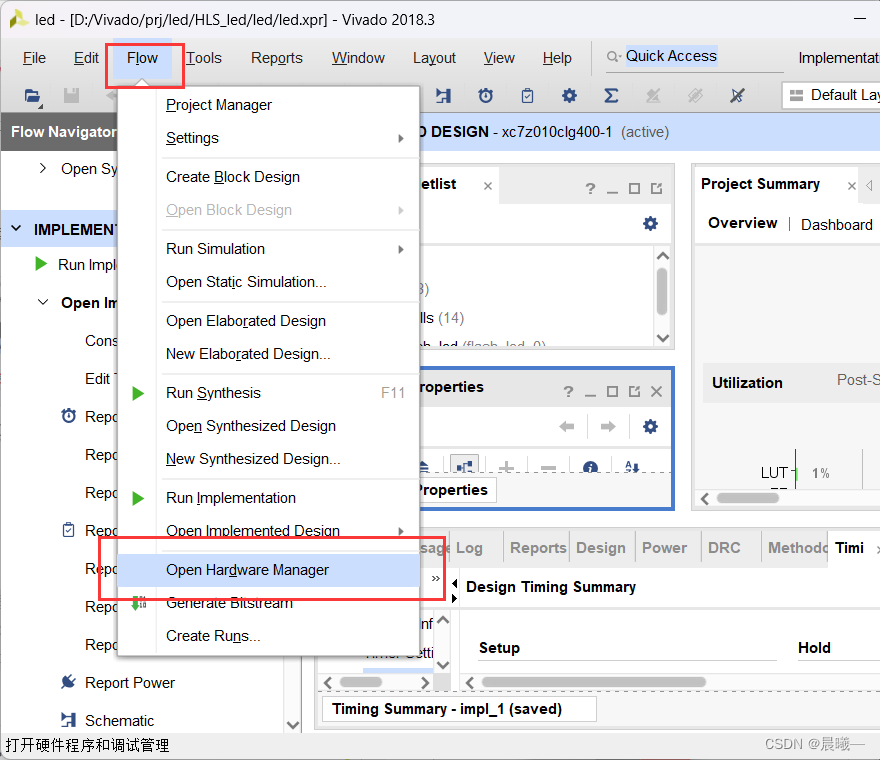

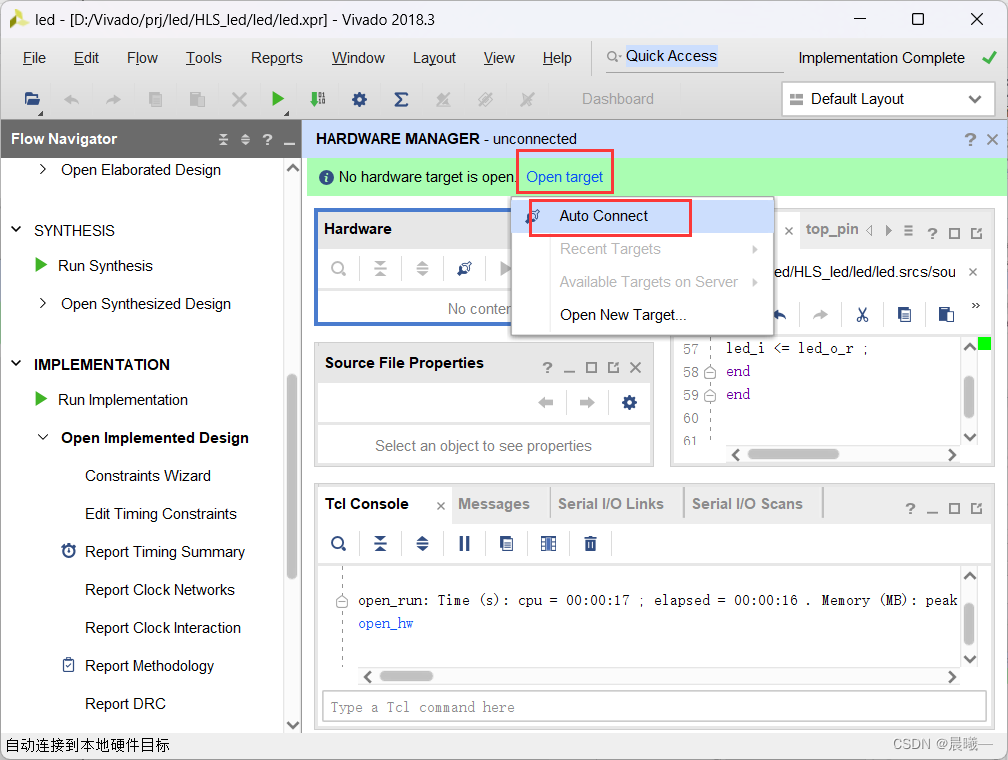

点击Flow

没有对应的开发板,跟着流程过一遍。编译结果均正确

参考

https://blog.csdn.net/weixin_54435584/article/details/130774070

https://blog.csdn.net/apple_52030329/article/details/130732768