PS

程序设计

LWIP

库修改

修改原因

SDK 2017.4

自带的

LWIP 1.4.1

库的版本为

2.0

,直接使用该库将无法通过

SFP

实现网络通信。

因此需要进行修改。 修改的原因有 2

个,第

1

个原因是由于

2017.4

版本产生的新

bug

。在

2015.4

版本中,若

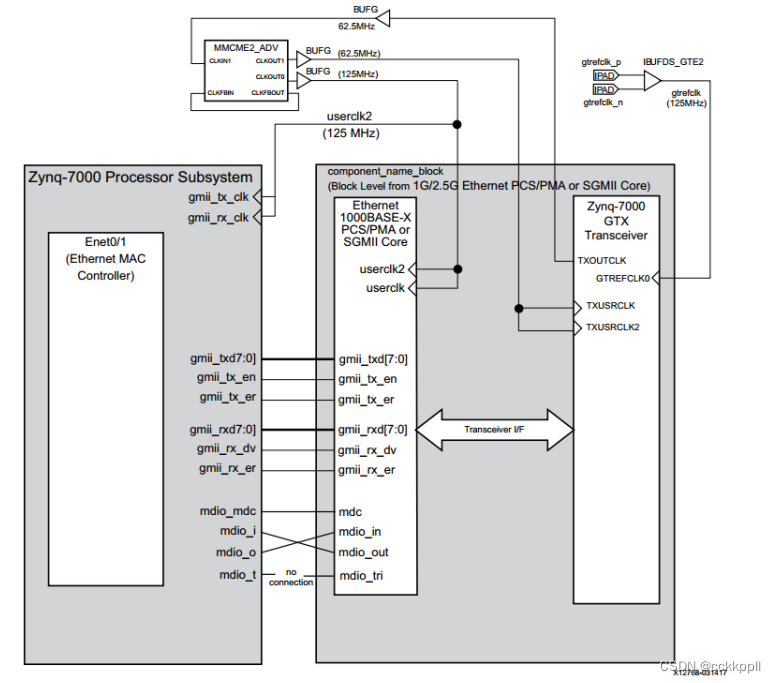

PL 部分使用了 1G/2.5G Ethernet PCS/PMA or SGMII IP

核,在

vivado

中编译完成

export

导入

SDK

后 在工程 bsp

的

xparameters.h

头文件中会包含一些与

1G/2.5G Ethernet PCS/PMA or SGMII IP

核相关 的宏定义。例如,使用 1000BASEX

模式时,产生的宏定义为:

#define

XPAR_GIGE_PCS_PMA_1000BASEX_CORE_PRESENT 1

#define

XPAR_PCSPMA_1000BASEX_PHYADDR 6

或者,使用

SGMII

模式时,产生的宏定义为:

#define

XPAR_GIGE_PCS_PMA_SGMII_CORE_PRESENT 1

#define

XPAR_PCSPMA_SGMII_PHYADDR 6

通过分析

lwip

库底层驱动代码,发现这些宏定义是

lwip

库底层代码的编译选项。在

lwip

库的

lwip141_v2_0\src\contrib\ports\xilinx\netif\xemacpsif_physpeed.c

和

xemacpsif_hw.c

两个文件中被使用。用于决定MDIO

接口配置外部

PHY

的方式。显然,作为

1000BASEX PHY

、

SGMII PHY

或通常的PHY

芯片的寄存器定义和配置方式是存在区别的,不能相互兼容。所以上述的宏定义对于使用

1G/2.5G Ethernet PCS/PMA or SGMII IP

核时至关重要。

而这些宏定义在

2017.4

版本中却不再出现。因而导致无法使用

LWIP

库对

1G/2.5G Ethernet PCS/PMA or SGMII IP 核进行正常配置使用。

第

2

个原因是由于

lwip

底层驱动自身存在的设计瑕疵。只要在

PL

部分使用

1G/2.5G Ethernet

PCS/PMA or SGMII IP

核,即

SDK

工程的

bsp

里存在宏定义

#define

XPAR_GIGE_PCS_PMA_SGMII_CORE_PRESENT 1

或者

#define

XPAR_GIGE_PCS_PMA_SGMII_CORE_PRESENT 1

那么,

lwip

底层驱动将只能通过

MDIO

接口采用对

1G/2.5G Ethernet PCS/PMA or SGMII IP

核进

行的配置方式。也就是说,只要使用了

1G/2.5G Ethernet PCS/PMA or SGMII IP

核,那么与

PS

连接的RGMII

接口的

PHY

芯片将不能被正常检测和配置,此时

lwip

将无法使用直接与

PS

连接的网口。这就对设计产生了限制。 为此,我们需要修改lwip

库。

修改方法

首先,找到

SDK

安装目录下的

LWIP

库的路径,例如

C:\Xilinx\SDK\2017.4\data\embeddedsw\ThirdParty\sw_servic

将

lwip141_v2_0

文件夹复制一份到工程目录下的

sdk_repo\bsp

文件夹下将其重新命名为

lwip141_v2_05

。

第一步,修改

lwip141_v2_05\data\lwip141.mld

文件(可用

Notapad++

等编辑器打开),

将其中的版本编号

OPTION VERSION = 2.0;

修改为

OPTION VERSION = 2.05;

然后, 在其中增加如下字段

:

BEGIN CATEGORY pcs_pma_core_options

PARAM name = pcs_pma_core_options, desc = "Options setting the pcs pma core related parameters"

PARAM name = use_pcs_pma_core_on_zynq, desc = "Option if set to 1 ensures emacps is used as emio, and connect to pcs_pma_core

in pl. Valid only for Zynq", type = bool, default = false;

PARAM name = use_1000basex, desc = "Option if set to 1 to ensures pcs_pma_core is using 1000basex mode", type = bool, default =

false;

PARAM name = use_sgmii, desc = "Option if set to 1 to ensures pcs_pma_core is using sgmii mode", type = bool, default = false;

PARAM name = 1000basex_phy_address, desc = "Option to define the phy address corresponding to the set in pcs_pma_core in

1000basex mode", type = int, default = 0;

PARAM name = sgmii_phy_address, desc = "Option to define the phy address corresponding to the set in pcs_pma_core in sgmii

mode", type = int, default = 0;

END CATEGORY

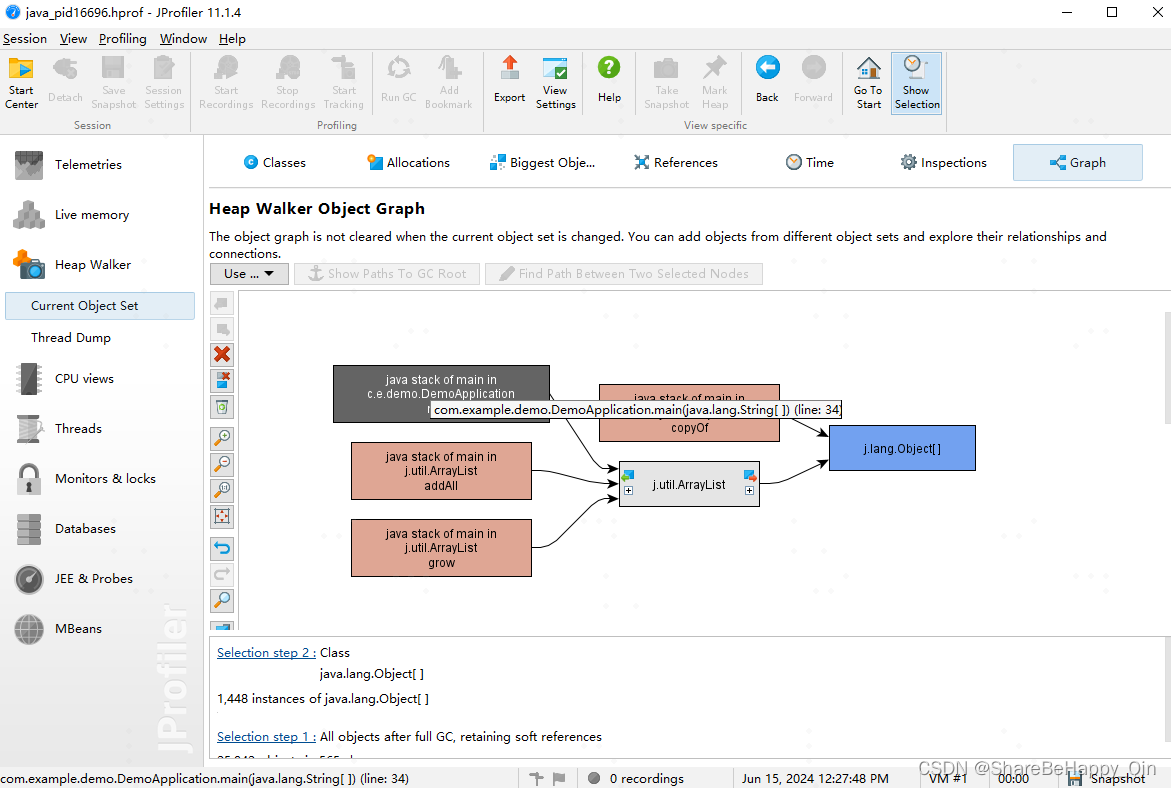

增加这段代码的目的是为了在

SDK

中

BSP

设置里,

lwip

参数设置窗口中增加一栏选项

pcs_pma_core_options

,其中包含

5

个子选项。如下图所示。

其中,

use_pcs_pma_core_on_zynq

表示

PL

端是否使用了

1G/2.5G Ethernet PCS/PMA or SGMII IP核;use_1000basex

表示

IP

核是否配置为

1000BASEX

模式;

use_sgmii

表示

IP

核是否配置为

SGMII

模式;1000basex_phy_address

表示使用

1000BASEX

模式时的

phy address

;

sgmii_phy_address

表示使用 SGMII模式时的

phy address

。这两个

phy address

必须与

vivado

中

IP

核的配置完全一致,例如,本例程中phy address

为

6

。

然后,打开

lwip141_v2_05\data\lwip141.tcl

文件,增加如下字段:

# PCS PMA CORE options

set use_pcs_pma_core_on_zynq [common::get_property CONFIG.use_pcs_pma_core_on_zynq $libhandle]

set use_1000basex [common::get_property CONFIG.use_1000basex $libhandle]

set use_sgmii [common::get_property CONFIG.use_sgmii $libhandle]

set 1000basex_phy_address [common::get_property CONFIG.1000basex_phy_address $libhandle]

set sgmii_phy_address [common::get_property CONFIG.sgmii_phy_address $libhandle]

if { $use_pcs_pma_core_on_zynq == true } {

puts $lwipopts_fd "\#define USE_PCS_PMA_CORE 1"

}

if { $use_1000basex == true } {

puts $lwipopts_fd "\#define XPAR_GIGE_PCS_PMA_1000BASEX_CORE_PRESENT 1"

puts $lwipopts_fd "\#define XPAR_PCSPMA_1000BASEX_PHYADDR $1000basex_phy_address"

}

if { $use_sgmii == true } {

puts $lwipopts_fd "\#define XPAR_GIGE_PCS_PMA_SGMII_CORE_PRESENT 1"

puts $lwipopts_fd "\#define XPAR_PCSPMA_SGMII_PHYADDR $sgmii_phy_address"

}

puts $lwipopts_fd ""

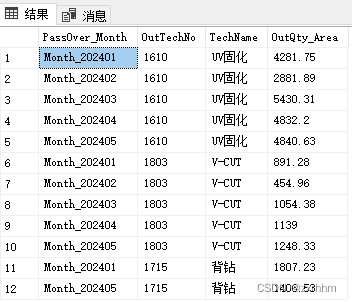

增加这段代码的目的是为了在工程所对应的

bsp

中的

lwipopts.h

头文件里,如下所示。

如下:

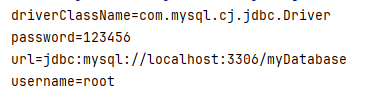

#define

USE_PCS_PMA_CORE 1

以及:

#define

XPAR_GIGE_PCS_PMA_1000BASEX_CORE_PRESENT 1

#define

XPAR_PCSPMA_1000BASEX_PHYADDR 6

或者:

#define

XPAR_GIGE_PCS_PMA_SGMII_CORE_PRESENT 1

#define

XPAR_PCSPMA_SGMII_PHYADDR 6

的宏定义。

这弥补了

2017.4

中的

bug

,可以通过

lwip

库增加所需的宏定义。

接 下 来 , 需 要 解 决 底 层 驱 动 使 用 限 制 , 为 此 要 修 改

lwip141_v2_05\src\contrib\ports\xilinx\netif\xemacpsif_physpeed.c

和

xemacpsif_hw.c

两个文件。两个文件的修改之处相同。在两个文件中,都将:

#if

XPAR_GIGE_PCS_PMA_1000BASEX_CORE_PRESENT == 1 || \

XPAR_GIGE_PCS_PMA_SGMII_CORE_PRESENT == 1

#define

PCM_PMA_CORE_PRESENT

改为:

#if

USE_PCS_PMA_CORE == 1 && (XPAR_GIGE_PCS_PMA_1000BASEX_CORE_PRESENT == 1 || \

XPAR_GIGE_PCS_PMA_SGMII_CORE_PRESENT == 1)

#define

PCM_PMA_CORE_PRESENT

这样就解决了

MDIO

接口配置的限制,只有当

USE_PCS_PMA_CORE

为

1

,即将

use_pcs_pma_core_on_zynq

设 为

1

时 。

MDIO

接 口 才 会 采 用

1G/2.5G Ethernet PCS/PMA or SGMII IP

核 的 配 置 策 略 。 将use_pcs_pma_core_on_zynq 设为

0

时,仍可以正常使用与

PS

连接的网口。

至此,

LWIP

库修改完成。