HW_SIO.GTGROUP

描述

GT组与硬件设备上的GT IO组相关,具有可用的数量

GT引脚和组由目标Xilinx FPGA确定。在Kintex-7 xc7k325部件上,用于

例如,有四个GT组,每个组包含四个差分GT引脚对。每个GT

pin有自己的接收器hw_sio_rx和发射器hw_sio_tx。GT组也可以包括

每个四路一个共享PLL或四路PLL。GT组是在IBERT调试核心上定义的,

并且当IBERT被添加到RTL中时,可以使用许多用户设置进行定制

设计请参阅集成误码率测试仪7系列GTX收发器LogiCORE IP

产品指南(PG132)[参考文献30]了解更多信息。

相关对象

GT组与hw_server、hw_target、hw_device、hw_sio_ibert、hw_si_GT、,

hw_sio_common、hw_sio_pll、hw_so_tx、hw_si_rx和hw_sio_link对象。

您可以查询与这些对象关联的GT组:

get_hw_sio_gtgroups-第个,共个[get_hw_sio_gts*MGT_X0Y9]

属性

可以使用report_property命令报告

HW_SIO_GTGROUP。请参阅Vivado Design Suite Tcl命令参考指南(UG835)

[参考文献13]了解更多信息。hw_sio_gtgroup对象的属性包括

以下,具有示例值:

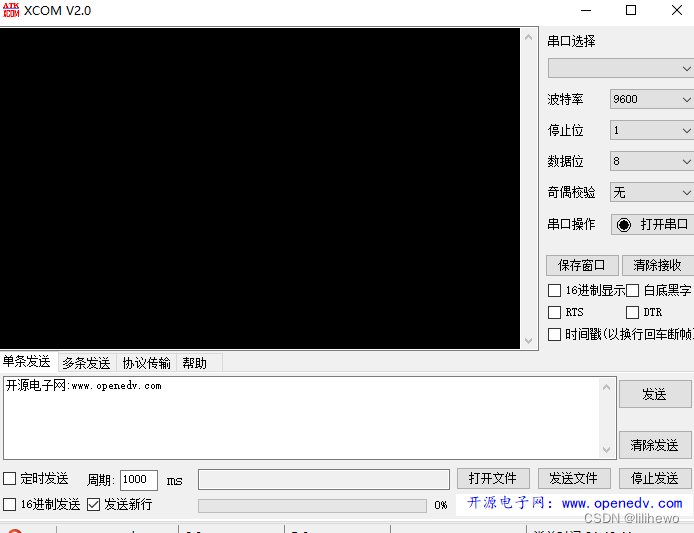

Vivado Design Suite Tcl shell或Tcl控制台中的以下命令:

描述

Xilinx的可定制LogiCORE™IP集成误码率测试仪(IBERT)核心

FPGA是为评估和监控千兆收发器(GTs)而设计的。IBERT

core支持系统内串行I/O验证和调试,使您能够进行测量和优化

基于FPGA的系统中的高速串行I/O链路。参考综合位错误

Ratio Tester 7系列GTX收发器LogiCORE IP产品指南(PG132)[Ref 30]了解更多信息

信息

IBERT调试核心允许您在上配置和控制GT的主要功能

设备,包括:

•TX预加重和后加重

•TX差动摆动

•RX均衡

•判决反馈均衡器(DFE)

•锁相环(PLL)分频器设置

当您对解决系统内的一系列问题感兴趣时,可以使用IBERT核心

调试和验证问题;从简单的时钟和连接问题到复杂的

边际分析和渠道优化问题。

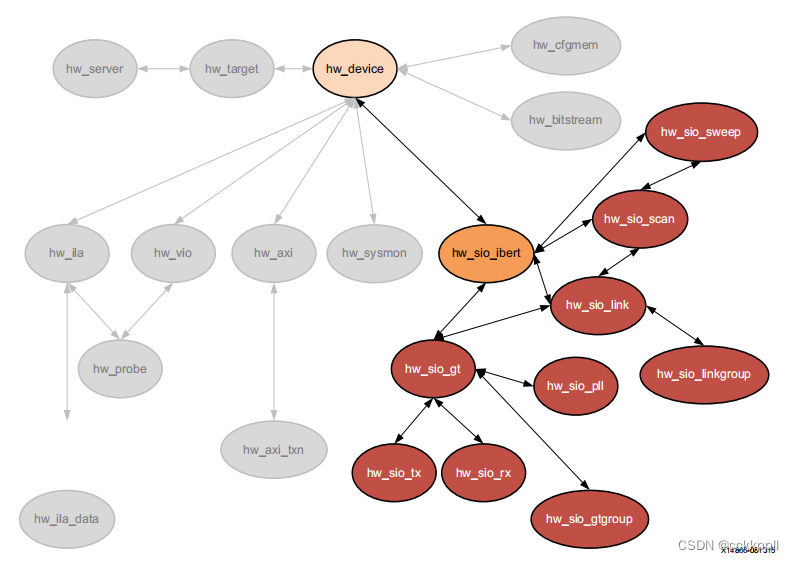

相关对象

如图2-22第83页所示,SIO-IBERT调试核心与hw_server相关联,

hw_target、hw_device、hw_sio-gt、hw_sio common、hw_si_pll、hw_sio_tx、hw_sio_rx,或

hw_sio_link对象。

您可以查询关联对象的IBERT调试核心:

get_hw_sio_iberts-of[get_hw_sio_plls*MGT_X0Y8/CPLL_0]

您还可以查询特定IBERT核心的关联对象:

get_hw_sio_commons-共[get_hw_sio_iberts]个

可以使用report_property命令报告指定给的实际特性

一个特定的hw_sio_ibert。请参阅Vivado Design Suite Tcl命令参考指南

(UG835)[参考文献13]了解更多信息。

分配给hw_sio_ibert对象的属性包括以下内容:

命令输入Vivado Design Suite Tcl shell或Tcl控制台: