1. 基于IODELAY的TDC设计原理

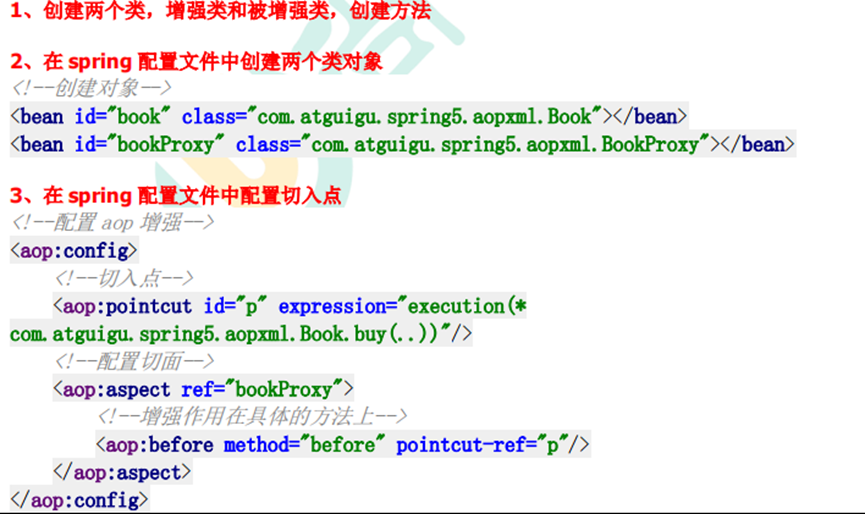

在第一篇中讲过,基于FPGA开发的TDC常见的有直接计数法,多相位时钟采样法,抽头延迟线法等等。前面3篇讲解了基于多相位的TDC,接下来主要讲解基于抽头延迟线的方法。在Xilinx FPGA开发中,要实现抽头延迟线,主要由进位链(Carry4)和IODELAY模块构建延迟链实现。以下主要介绍基于IODELAY的TDC设计原理。

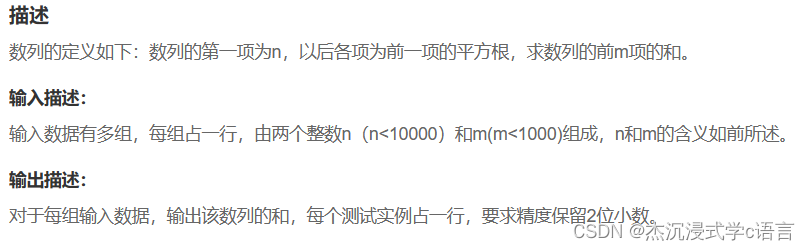

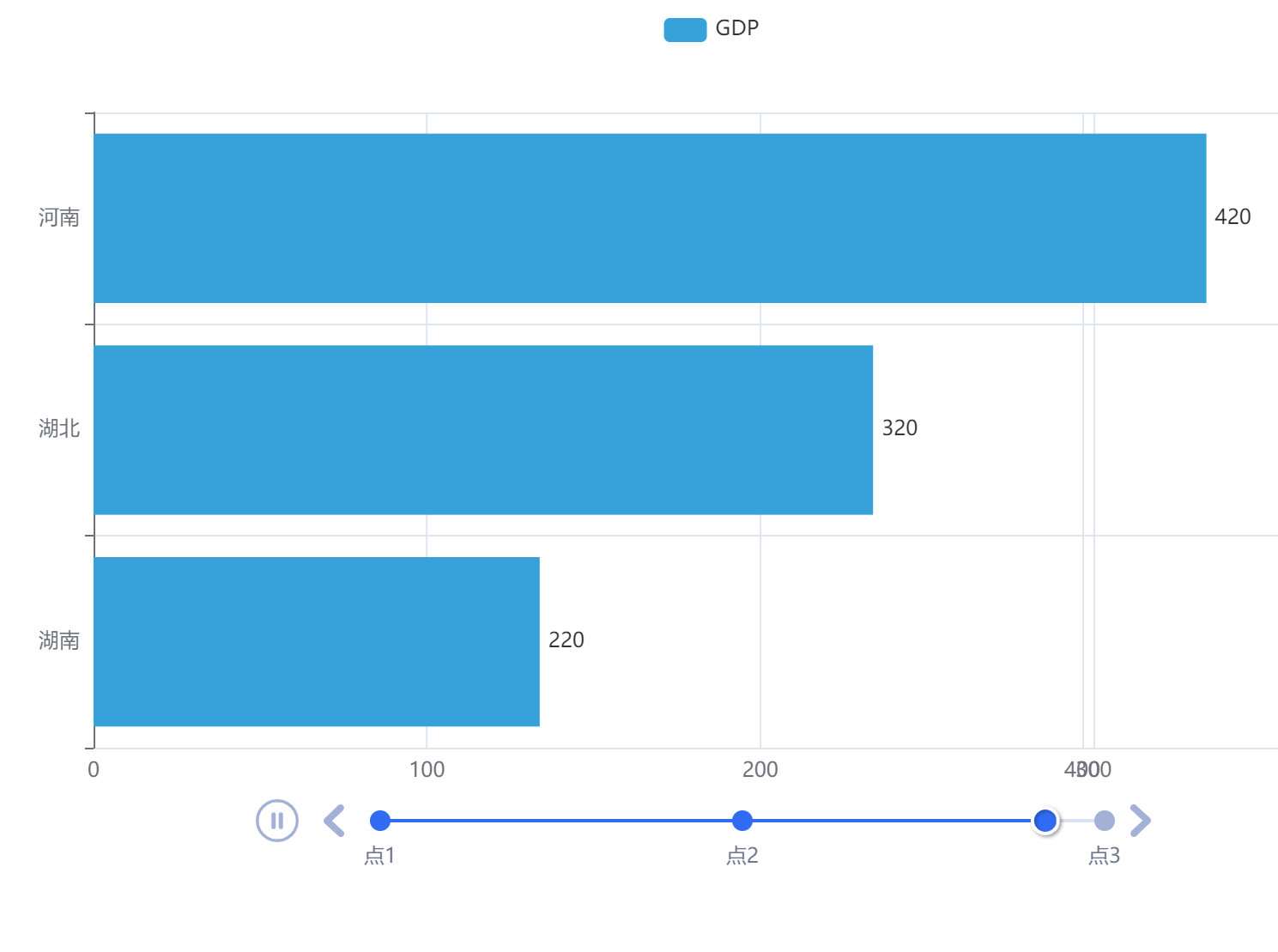

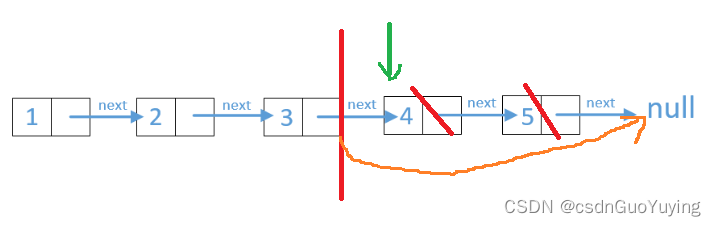

抽头延迟线法实现如下,图1为抽头延迟链TDC构成的一种结构,将一组延迟最小单元(延迟时间为)级联成一条延迟链,组成一个周期。每个延迟单元都会引出一个抽头,并用相应的触发器进行锁存。一般采用抽头延迟线法,都会使用粗计数和细计数相结合的方式。即粗计数用于统计Start信号和Stop信号之间完整的时钟周期的个数,而细计数用于测量小于一个时钟周期内信号传播的时间间隔,即统计经过了多少个延迟单元。