1. 简介

VCS是一种常用的Verilog仿真和综合工具,由Synopsys公司开发。它提供了一个完整的设计验证环境,用于验证硬件设计的正确性和性能。以下是VCS工具的一些主要特点和功能:

- 仿真功能:VCS支持基于事件驱动的数字电路级仿真,能够准确地模拟设计中的信号传输和电路行为。它可以处理大型设计,并提供高效的仿真方式和快速的仿真速度。

- 综合功能:VCS还提供了综合功能,允许将Verilog描述的设计转换成门级电路,在后端流程中进行布局和布线以及时序优化。

- 调试功能:VCS提供了强大的调试工具,包括信号波形查看器、断点设置、单步执行等功能,有助于定位设计中的错误并检查设计的正确性。

- 性能分析:VCS可以生成详细的仿真报告和性能分析结果,帮助设计人员优化设计,改进时序约束以满足各种性能目标。

- 支持多种设计语言:VCS支持Verilog和SystemVerilog等多种硬件描述语言,方便用户采用不同的设计风格和编码方式。

- 高级验证功能:VCS提供了诸多高级验证功能,例如,事务级建模、函数覆盖率分析、断言语句(Assertion)的支持等,帮助设计人员更全面地验证和测试设计。

- 集成与兼容性:VCS与其他EDA工具集成紧密,可以与逻辑综合工具、时序约束工具以及物理布局工具等进行无缝连接,方便整个设计流程的集成和协同工作。

2. 安装

此处安装VCS2018套装,包括vcs_vO-2018.09-SP2、scl_v2018.06、vcs_mx_vO-2018.09-SP2、verdi-2018.9。

2.1. 依赖安装

sudo apt install -y csh

sudo apt install -y lsb 2.2. 软件安装

- 下载vcs2018,百度网盘 请输入提取码,提取码gbkc 。

- 解压,添加权限,执行脚本。

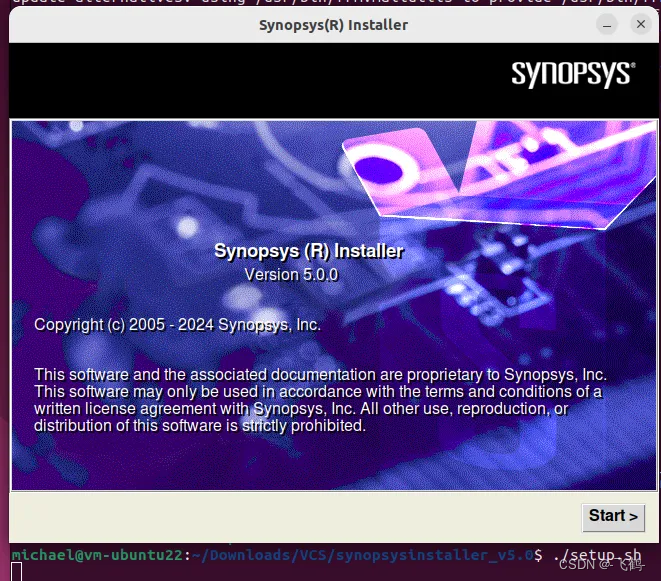

mkdir ~/synopsys unzip VCS.zip cd VCS/synopsysinstaller_v5.0 chmod 777 SynopsysInstaller_v5.0.run ./SynopsysInstaller_v5.0.run - 启动安装脚本./setup.sh,弹出安装界面

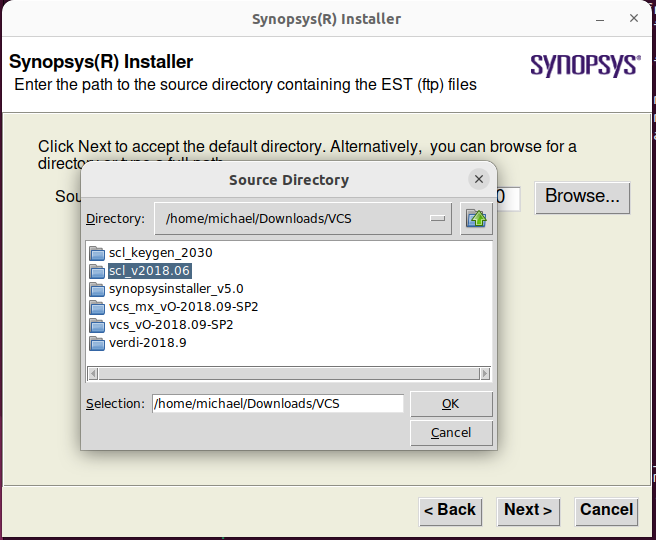

依次Next,直到安装源选择scl_v2018.06,再点击OK

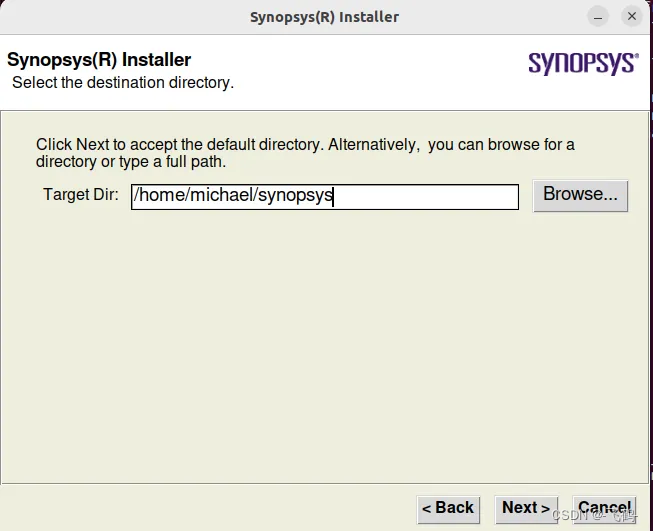

选择安装目录:

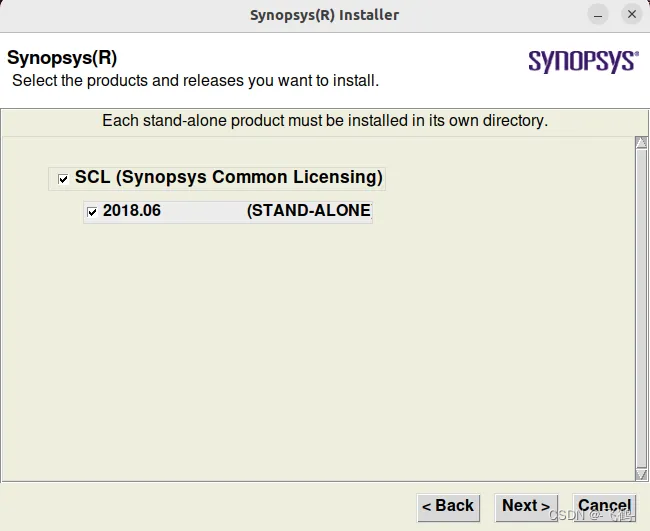

选择安装组件(勾选所有):

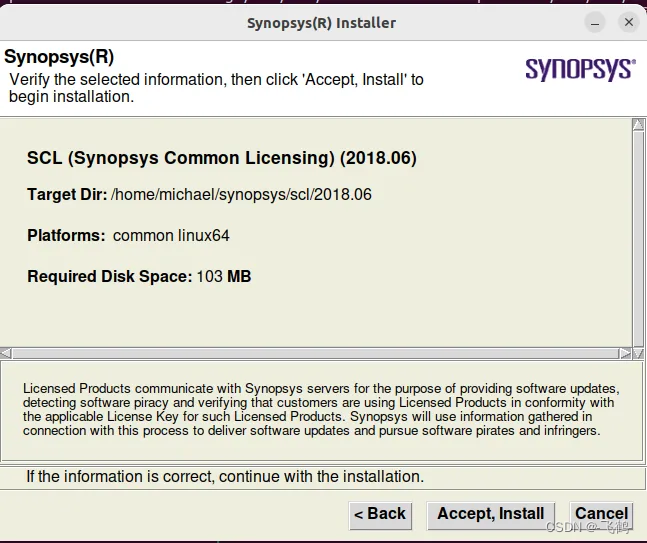

选择安装组件(勾选所有): 选择Next直到下图,点击Accept,Install进入安装:

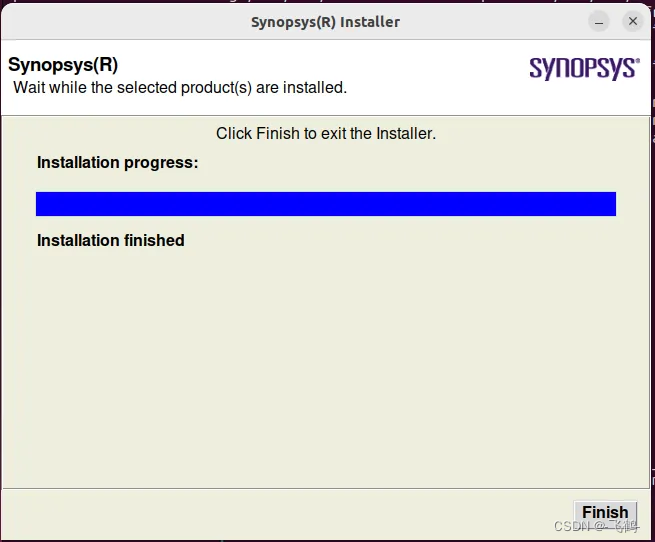

选择Next直到下图,点击Accept,Install进入安装: 安装结束,显示下图,点击Finish:

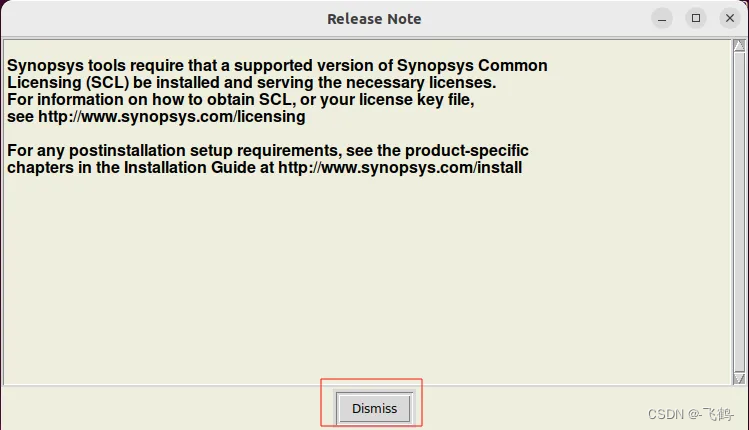

安装结束,显示下图,点击Finish: 出现下图,点击Dismiss结束安装。

出现下图,点击Dismiss结束安装。 用同样的方式分别安装目录下的vcs_vO-2018.09-SP2、vcs_mx_vO-2018.09-SP2、verdi-2018.9。

用同样的方式分别安装目录下的vcs_vO-2018.09-SP2、vcs_mx_vO-2018.09-SP2、verdi-2018.9。

2.3. 破解

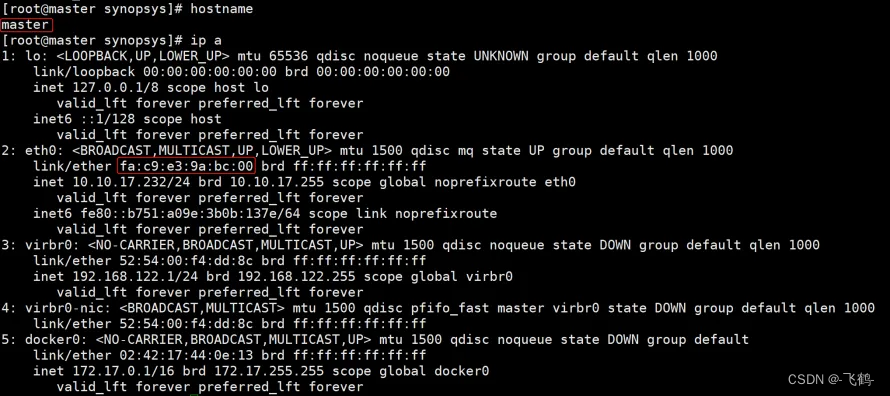

- 获取Hostname和MAC地址:

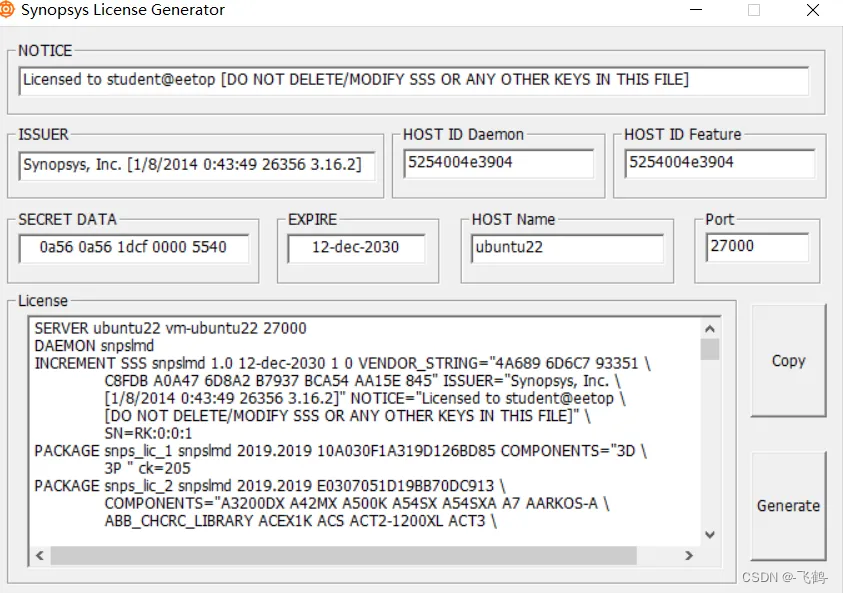

- 在Windows下运行scl_keygen_2030/scl_keygen.exe,配置获取的hostname和mac地址,点击Generate生成授权信息文件Synopsys.dat。

- 将文件拷贝进Ubuntu的/home/michael/synopsys/license/Synopsys.dat

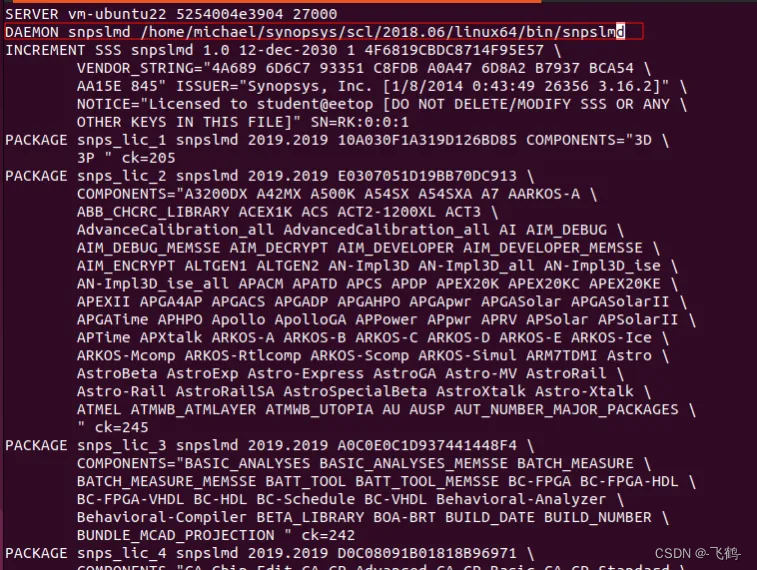

- 打开Synopsys.dat文件,在第2行添加/home/michael/synopsys/scl/2018.06/linux64/bin/snpslmd。

- 启用授权服务

sudo mkdir /usr/tmp sudo mkdir /usr/tmp/.flexlm /home/michael/synopsys/scl/2018.06/linux64/bin/lmgrd -c /home/michael/synopsys/license/Synopsys.dat

2.4. 环境路径配置

打开~/.bashrc,在最后面添加如下内容,路径根据安装情况相应修改,27000@ubuntu22的ubuntu22修改为相应的HostName。

#export export SYNOPSYS="/usr/software/synopsys"

export VCS_TARGET_ARCH="amd64"

export DVE_HOME="/home/michael/synopsys/vcs/O-2018.09-SP2/gui/dve"

#export PATH="/home/michael/synopsys/vcs/O-2018.09-SP2/bin:"$PATH

export PATH="/home/michael/synopsys/vcs-mx/O-2018.09-SP2/bin:"$PATH

#export VCS_HOME="/home/michael/synopsys/vcs/O-2018.09-SP2"

export VCS_HOME="/home/michael/synopsys/vcs-mx/O-2018.09-SP2"

#export VCS_ARCH_OVERRIDE="linux"

#verdi

export PATH="/home/michael/synopsys/verdi/Verdi_O-2018.09-SP2/bin:"$PATH

export VERDI_HOME="/home/michael/synopsys/verdi/Verdi_O-2018.09-SP2"

export LD_LIBRARY_PATH="/home/michael/synopsys/verdi/Verdi_O-2018.09-SP2/share/PLI/lib/LINUX64":$LD_LIBRARY_PATH

export VERDI_DIR="/home/michael/synopsys/verdi/Verdi_O-2018.09-SP2"

export NOVAS_INST_DIR="/home/michael/synopsys/verdi/Verdi_O-2018.09-SP2"

export NPI_PLATFORM="LINUX64_GNU_472"

export LD_LIBRARY_PATH="$NOVAS_INST_DIR/share/NPI/lib/LINUX64_GNU_520":$LD_LIBRARY_PATH

export NOVAS_HOME="/home/michael/synopsys/verdi/Verdi_O-2018.09-SP2"

#LICENSE

export SNPSLMD_LICENSE_FILE="/home/michael/synopsys/license/Synopsys.dat"

export SNPSLMD_LICENSE_FILE=27000@ubuntu22

export LM_LICENSE_FILE="/home/michael/synopsys/license/Synopsys.dat"

alias lmli="/home/michael/synopsys/scl/2018.06/linux64/bin/lmgrd -c /home/michael/synopsys/license/Synopsys.dat"

#SCL

export PATH=/home/michael/synopsys/scl/2018.06/linux64/bin:$PATH

alias dve="dve -full64 &"

alias vcs64="vcs -full64"

alias vcs="vcs -full64"

alias verdi="verdi -full64 &"

2.5. 验证License

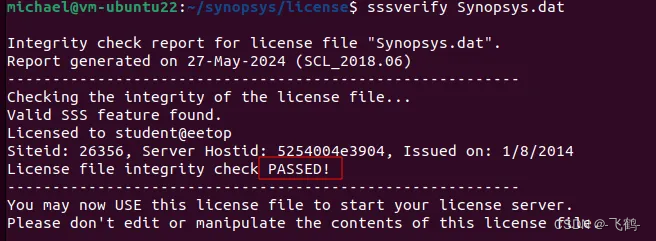

sssverify 自己的license路径

出现下面信息表示License生成正确。

2.6. 开机自动开启授权服务

在/etc/profile.d/目录下创建lmli.sh

cd /etc/profile.d/

sudo touch lmli.sh

sudo chmod 777 lmli.sh在lmli.sh文件中添加如下内容:

`/home/michael/synopsys/scl/2018.06/linux64/bin/lmgrd -c /home/michael/synopsys/license/Synopsys.dat -l /home/michael/synopsys/scl/2018.06/linux64/bin/lmgrd.log`

2.7. 解决异常

1. libpng12.so.0 cannot read

sudo ln -s /home/michael/synopsys/vcs-mx/O-2018.09-SP2/vcfca/linux64/vcst/lib/libpng12.so.0.31.0 /usr/lib/x86_64-linux-gnu/libpng12.so.02. undefined reference to `pthread_yield'

cd /home/michael/synopsys/vcs-mx/O-2018.09-SP2/linux64/lib

mv vcs_save_restore_new.o vcs_save_restore_new.o.bak

objcopy --redefine-sym pthread_yield=sched_yield ./vcs_save_restore_new.o.bak ./vcs_save_restore_new.o3. Failedto open the TcP port number in thelicense

lmdown

killall lmgrd4. Can't make directory/usr/tmp/.flexlm

cd /usr

sudo mkdir tmp

cd local

sudo mkdir flexlm

cd flexlm

sudo mkdir licenses5. /bin/sh:0: illegal option –h

sudo rm -f /bin/sh

sudo ln -s /bin/bash /bin/sh3. 验证

3.1. VCS

VCS有两个版本,分别为vcs和vcs-mx,vcs-mx在vcs的基础上更好地支持SystemVerilog和SystemC。像在使用UMV/UVMC时,就必须使用vcs-mx。另外,在64位系统上,推荐使用64位的vcs,性能更好,通过-full64来指定。

3.1.1. top文件

module add (

input [20:0] A ,

input signed [17:0] B ,

output signed [22:0] C);

wire signed [21:0] A_signed;

assign A_signed = {1'b0,A};

assign C = A_signed + B;

endmodule3.1.2. testbench文件

`timescale 1ns/1ns

module test;

reg clk;

reg rst_n;

reg [20:0] A;

reg signed [17:0] B;

wire signed [22:0] C;

initial begin

clk = 0;

rst_n = 0;

A = 21'b0;

B = 18'b0;

#10;

rst_n = 1;

repeat(80) @(posedge clk) begin

A = A + 21'b1;

end

#2000;

$finish;

end

always #5 clk = ~clk;

initial begin

$fsdbDumpfile("./rtl.fsdb");

$fsdbDumpvars("+all");

end

add add_inst(

.A(A),

.B(B),

.C(C));

endmodule

3.1.3. 源文件列表

vcs中以.f文件为源文件列表,其中每一行记录一个verilog/SystemVerilog源文件。

filelist.f文件内容如下:

top.v

tb.v

3.1.4. Makefile文件

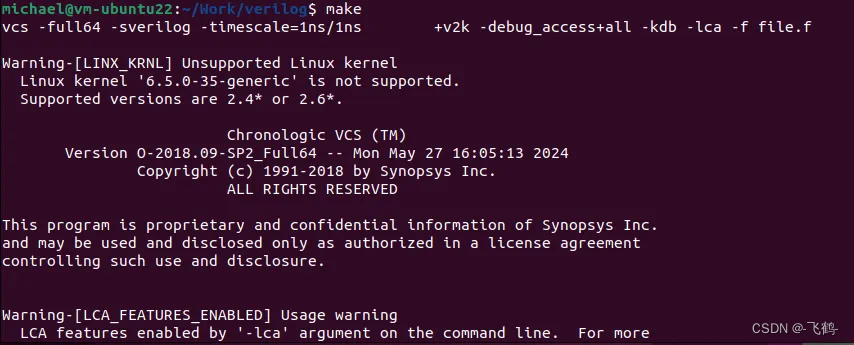

VCS = vcs -full64 -sverilog -timescale=1ns/1ns \

+v2k \

-debug_access+all -kdb -lca\

-f file.f

comp:

$(VCS)

.PHONY:verdi clean sim

verdi:

verdi -ssf rtl.fsdb

sim:

./simv

verdi:

verdi -ssf rtl.fsdb

clean:

rm -rf csrc simv* *.lib *.lib++ nLint*

rm -rf *.log *.vpd *.fsdb* *.key *log rtl.fsdb*

3.1.5. 编译

make

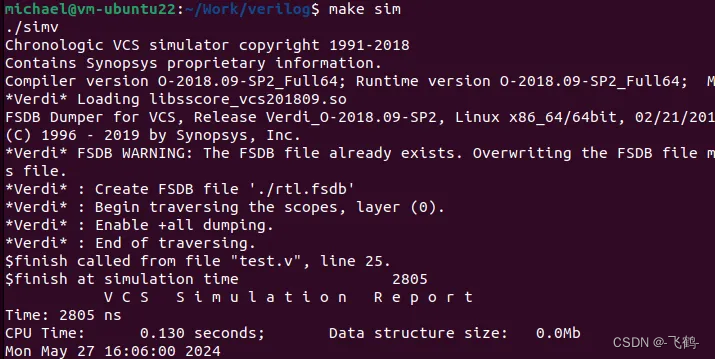

3.1.6. 仿真

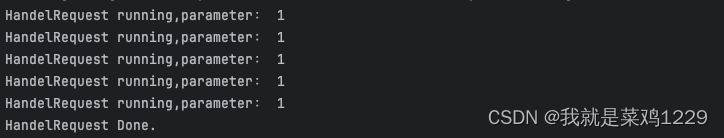

make sim

3.1.7. verdi查看波形

make verdi