目录

1.摘要

2.最终实现的ModelSim仿真

3.Matlab仿真和MoselSim仿真进行对比

4.完整工程

1.摘要

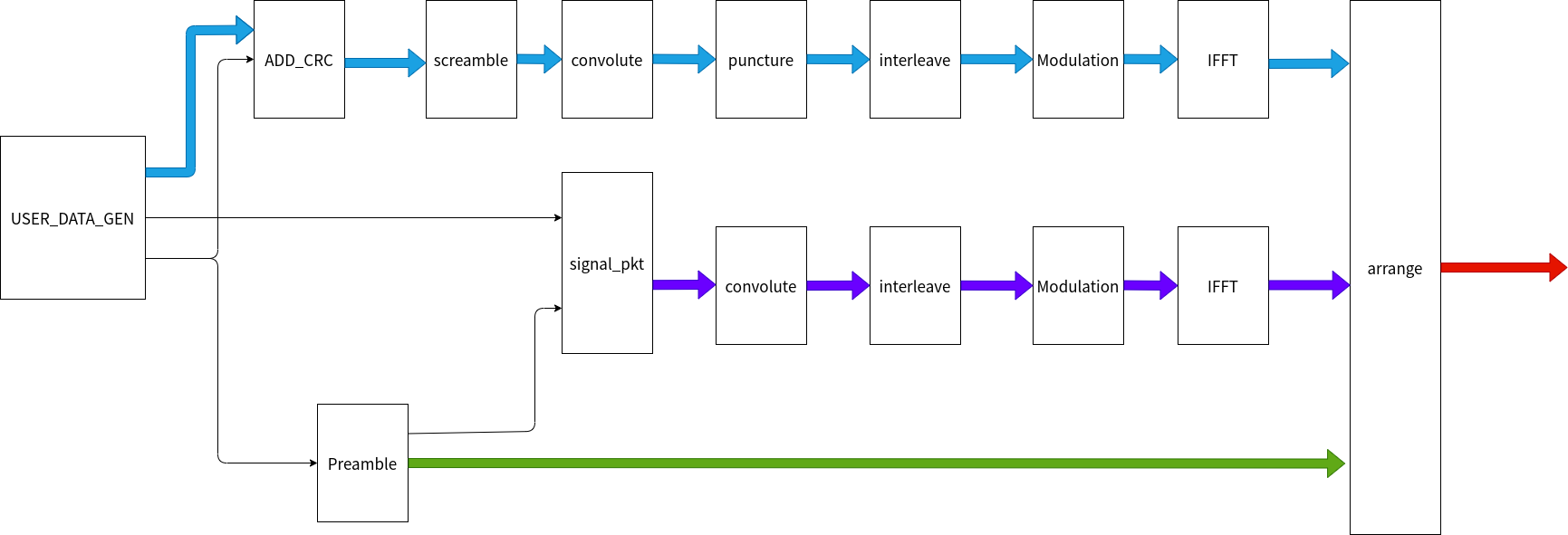

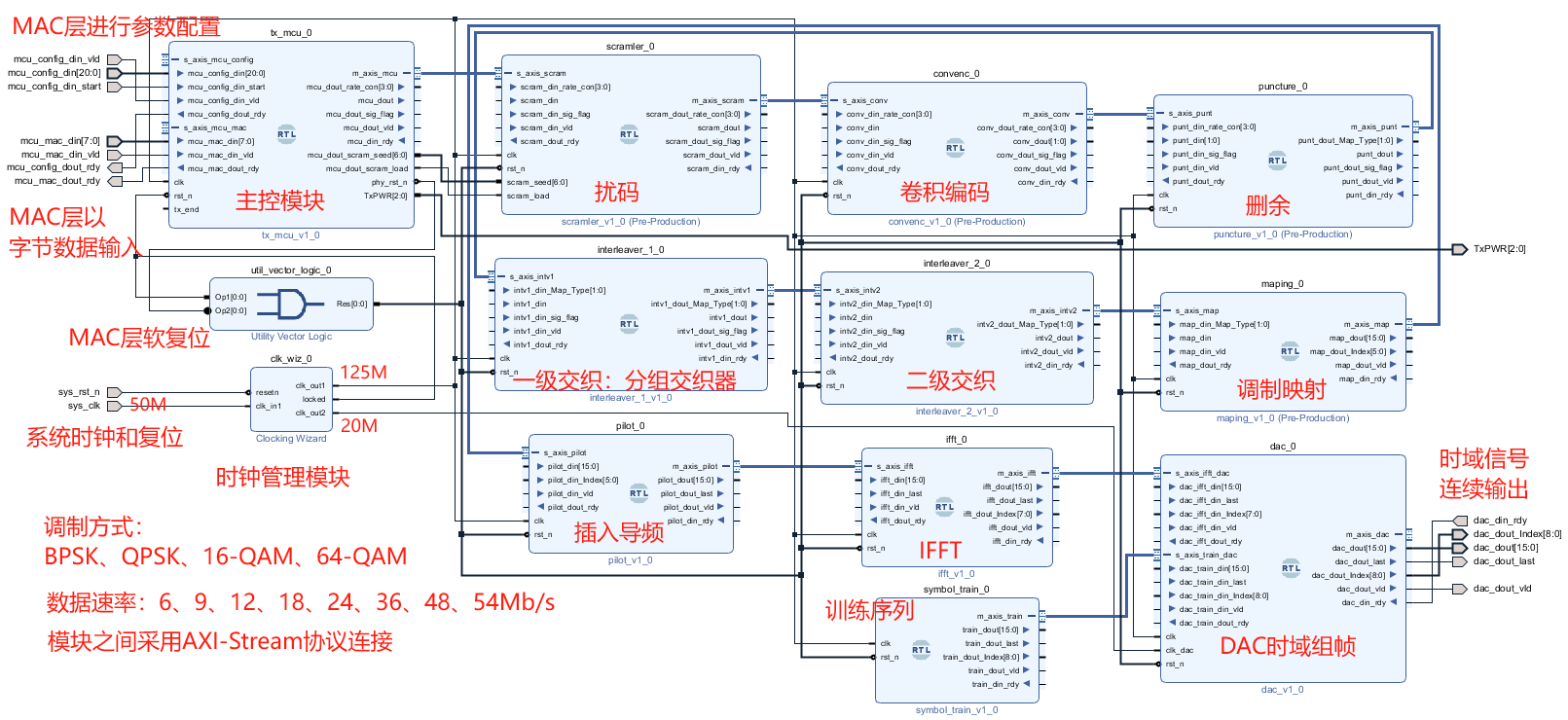

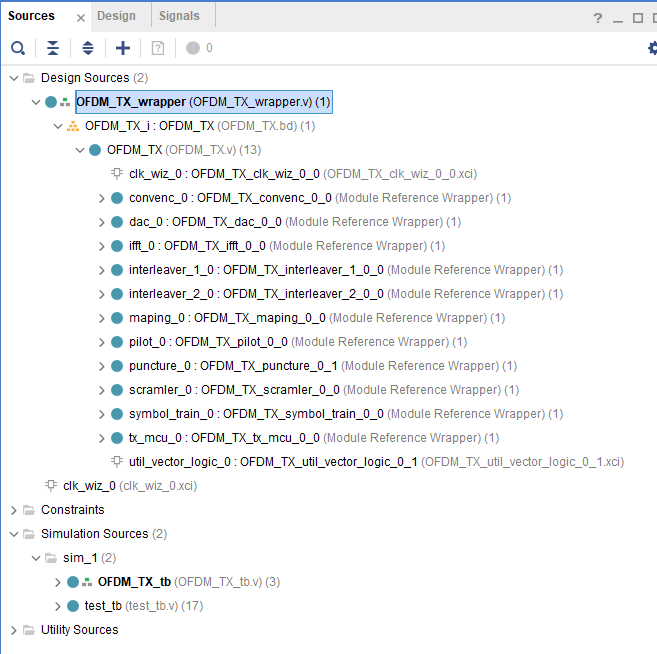

本系统在Xilinx的zynq 7000系列FPGA芯片上实现了一个基于IEEE 802.11a协议的OFDM基带处理发射机的功能。本系统包含了整个发射机的所有功能,包括序列训练符号、Siganl符号和Data符号等的实现过程。实现了data域的数据处理过程:由MAC层传来字节数据->并串转换->扰码->卷积编码->删余->一级交织->二级交织->调制映射->插入导频->IFFT->DAC。

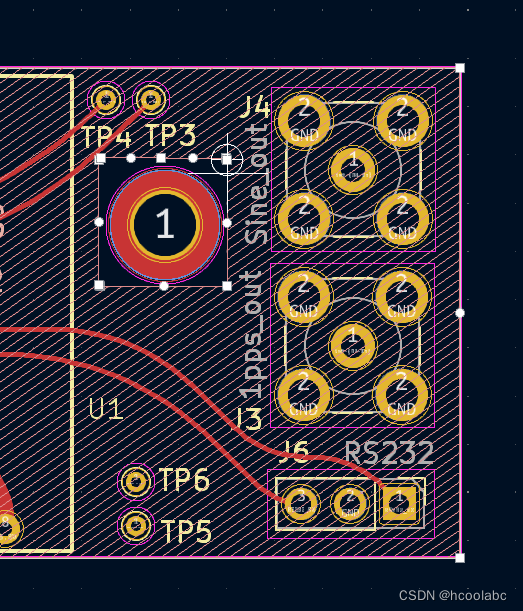

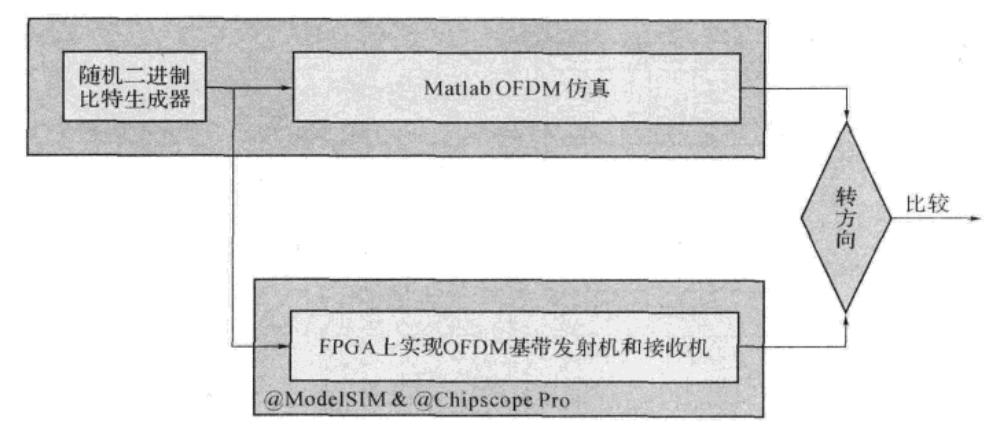

发射机整体构架

系统采用125M时钟,DAC采用20M时钟,数据处理时使用AXI-Stream协议,让整个系统工作在流水线状态下,且最终保证了送往DAC的数据以20M的速率无间隙的连续输出,相比《基于Xilinx FPGA的OFDM通信系统基带设计》使用多重跨时钟域,本系统更稳定可靠。

系统硬件框图

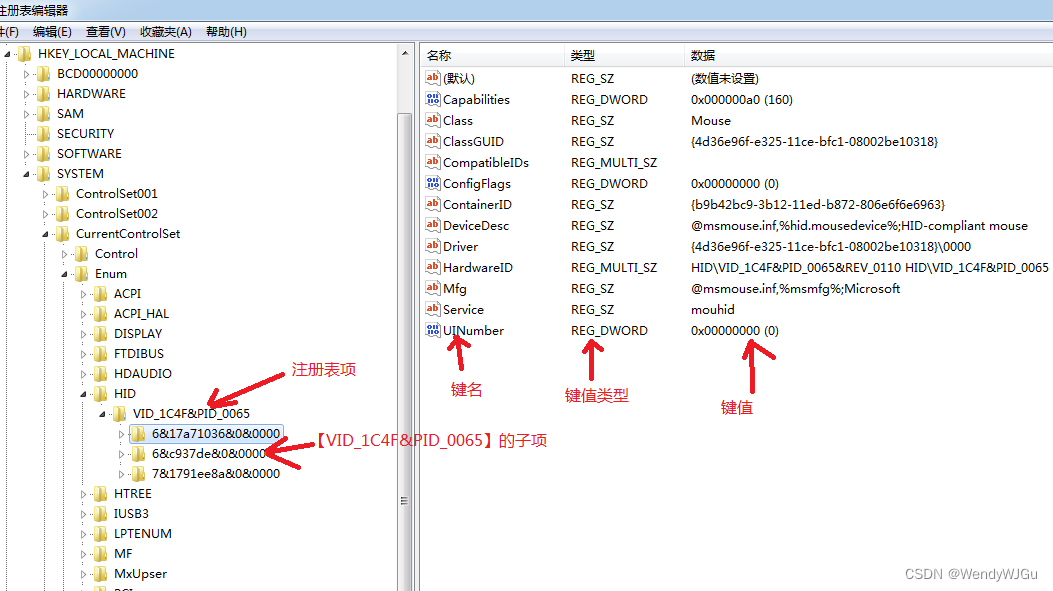

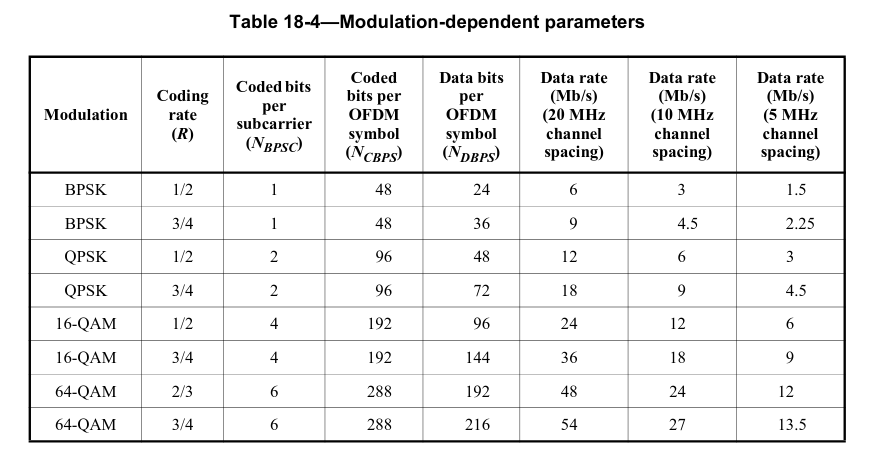

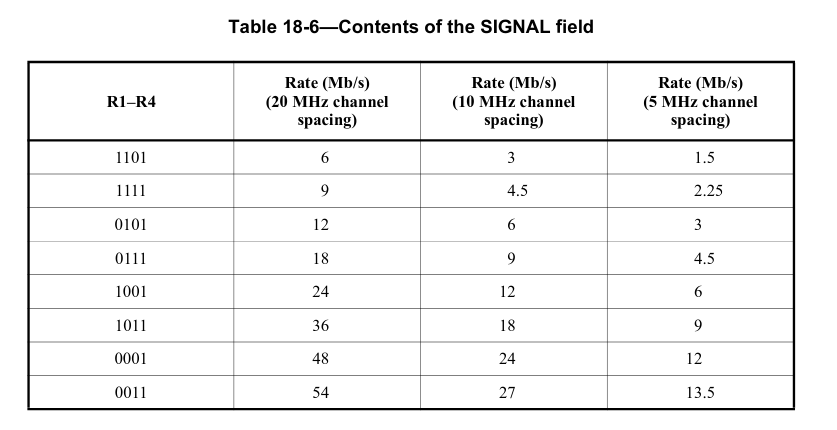

系统实现了IEEE 802.11a协议里面的BPSK、QPSK、16-QAM、64-QAM调制。

调制方式

实现了数据速率6、9、12、18、24、36、48、54Mb/s。

数据速率

该设计完成了,Matlab和ModelSim仿真闭环测试对比。

Matlab和ModelSim仿真闭环测试对比

2.最终实现的ModelSim仿真

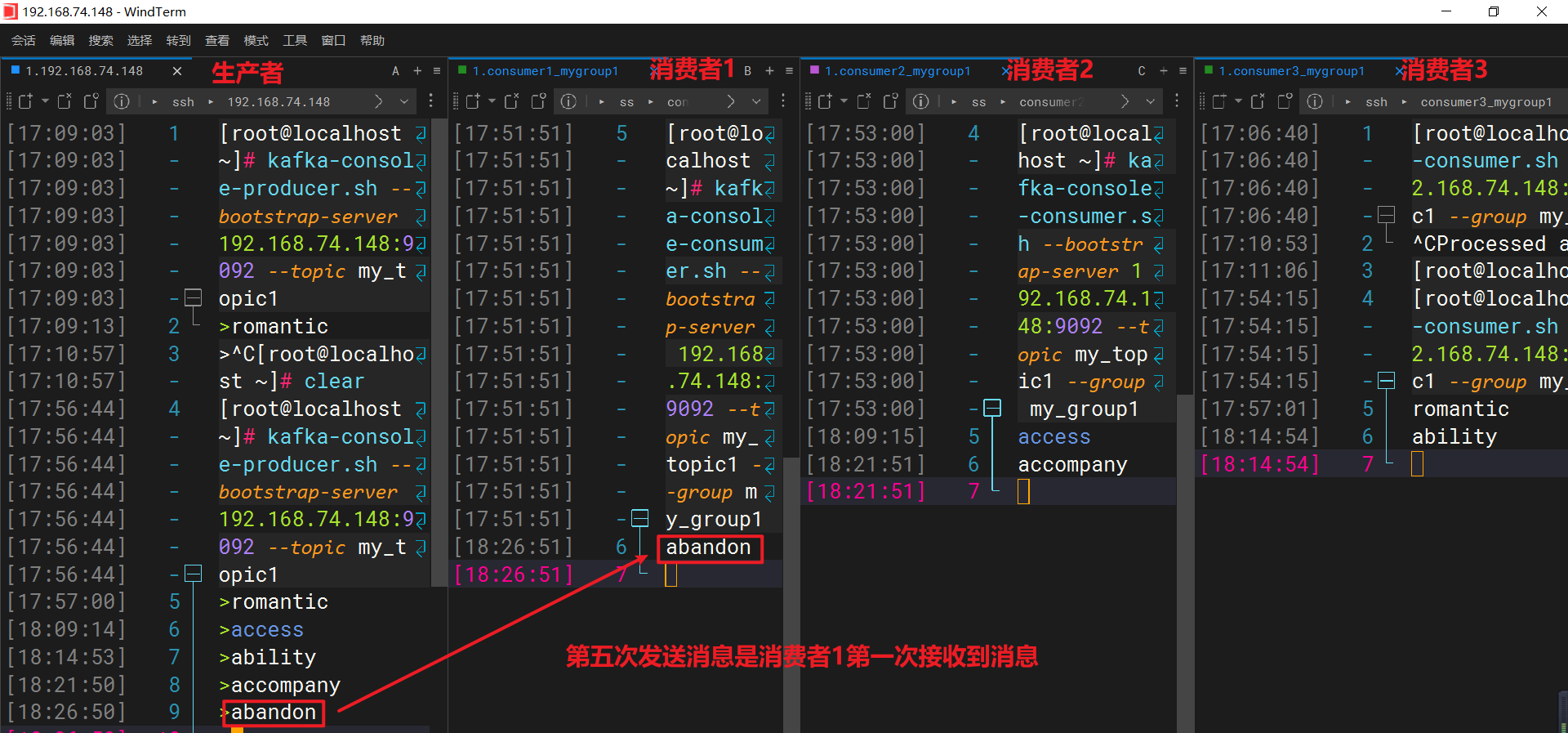

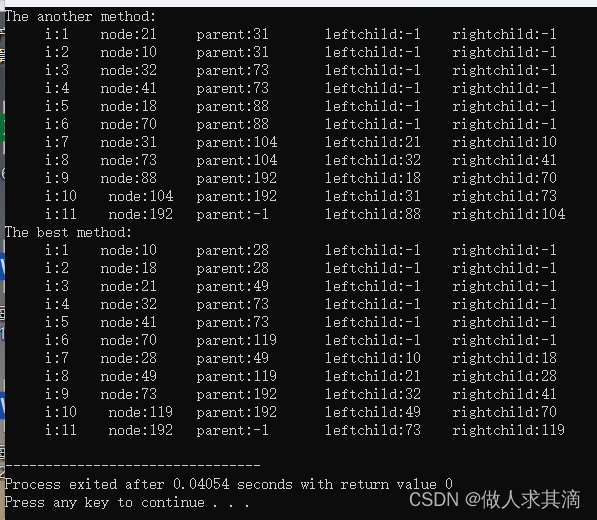

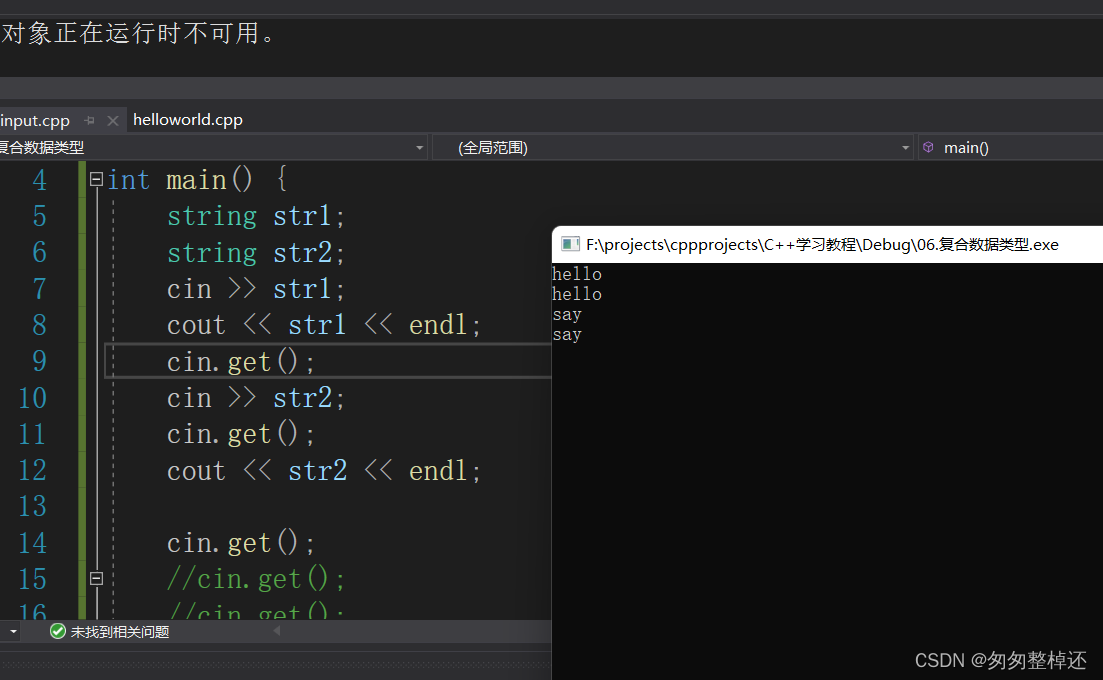

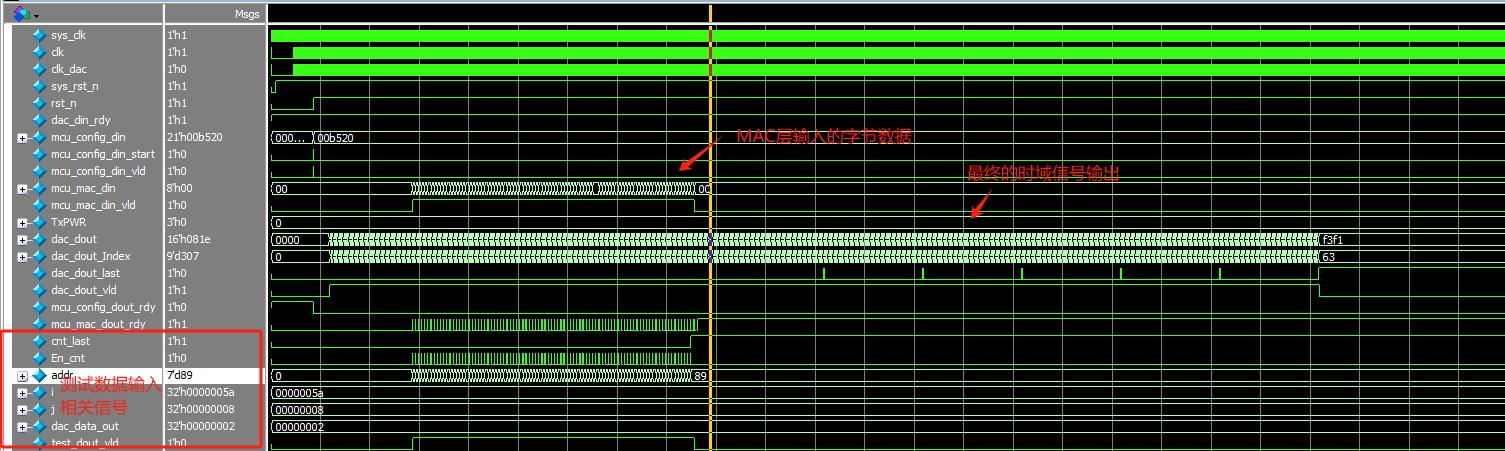

测试时,数据速率设为36,即16-QAM调制,编码效率3/4。测试数据使用5个OFDM符号,720个bit,即90byte。

下图显现了顶层输入输出的仿真效果,addr=0-89对应测试数据的字节地址:

下图显示了DAC时域组帧模块仿真效果:

DAC时域组帧模块仿真

3.Matlab仿真和MoselSim仿真进行对比

clc;

close all;

PATH = 'D:/FPGA/OFDM_802.11a_my/TX/matlab/OFDM_802_11a_TX/';

FPGA_dac_dout = readlines([PATH,'dac_data_out.txt'],'EmptyLineRule','skip')';

display(FPGA_dac_dout);

FPGA_Im_dac_dout = extractBefore(FPGA_dac_dout,9);

FPGA_Re_dac_dout = extractAfter(FPGA_dac_dout,8);

display(FPGA_Re_dac_dout);

display(FPGA_Im_dac_dout);

q = quantizer('fixed','round','saturate',[8,6]);

FPGA_Re_dac_dout = bin2num(q,FPGA_Re_dac_dout);

FPGA_Im_dac_dout = bin2num(q,FPGA_Im_dac_dout);

FPGA_Re_dac_dout = cell2mat(FPGA_Re_dac_dout);

FPGA_Im_dac_dout = cell2mat(FPGA_Im_dac_dout);

FPGA_dac_dout = FPGA_Re_dac_dout + 1j*FPGA_Im_dac_dout;

preamble_out = preamble_out / max(abs(preamble_out ));

FPGA_dac_dout = FPGA_dac_dout /max(abs(FPGA_dac_dout));%归一化

display(preamble_out );

display(FPGA_dac_dout);

figure;

subplot(2,1,1);

plot(real(preamble_out ));title('Matlab仿真输出实部');

subplot(2,1,2);

plot(real(FPGA_dac_dout));title('FPGA仿真输出后实部');

figure;

subplot(2,1,1);

plot(imag(preamble_out ));title('Matlab仿真输出后虚部');

subplot(2,1,2);

plot(imag(FPGA_dac_dout));title('FPGA仿真输出后虚部');

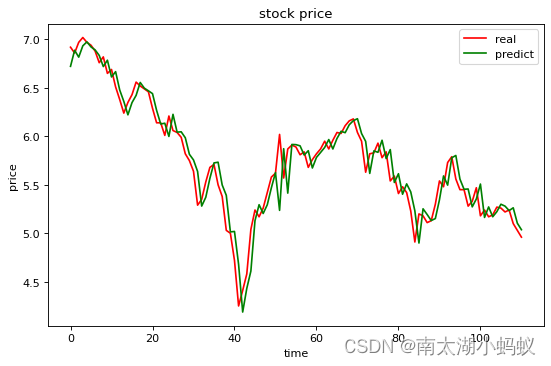

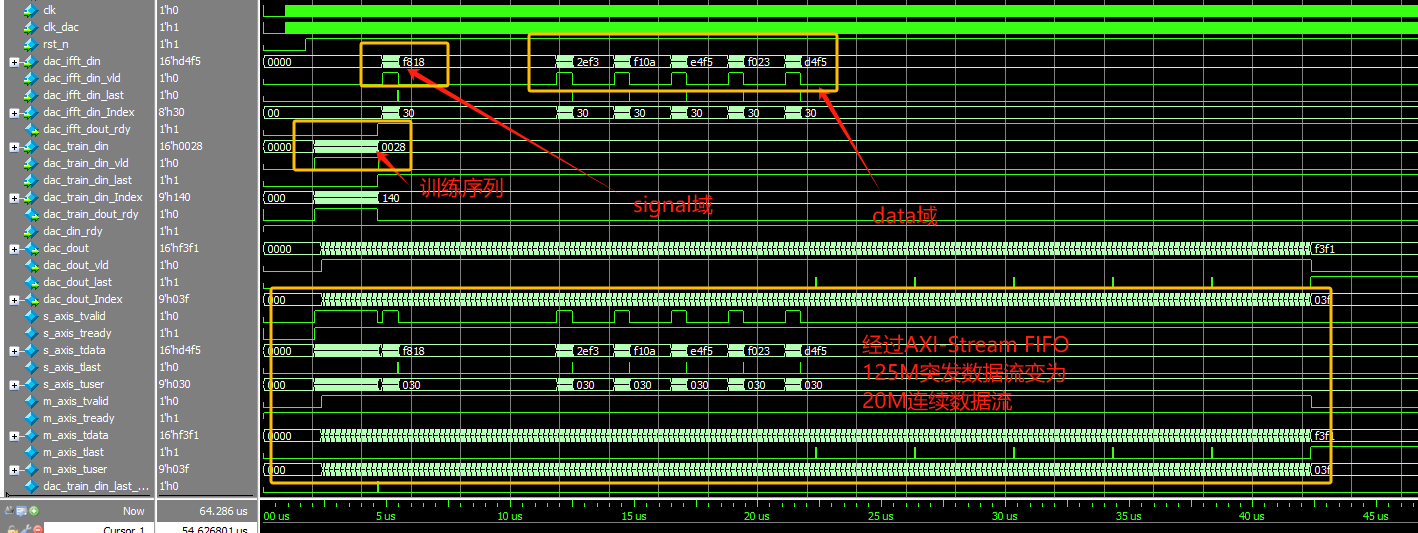

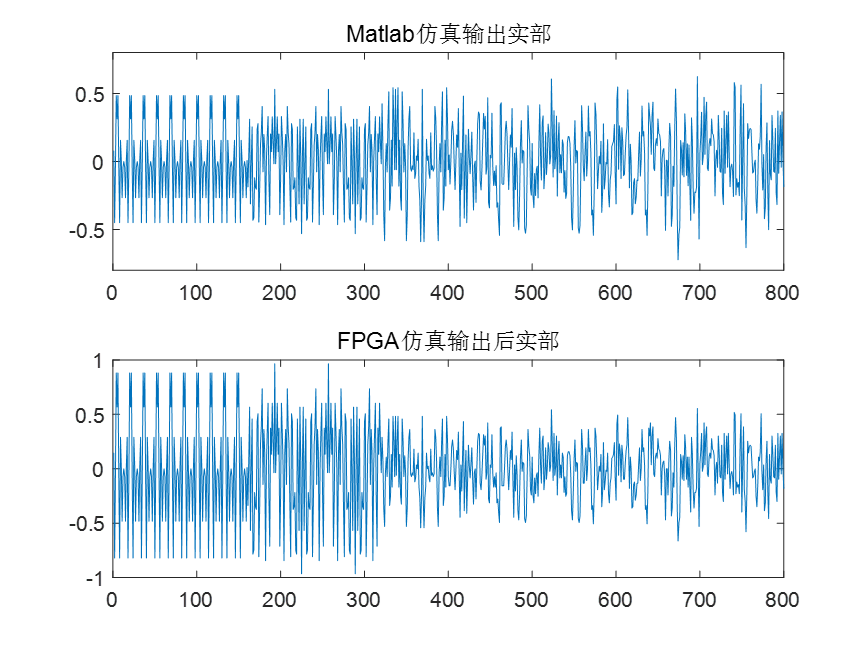

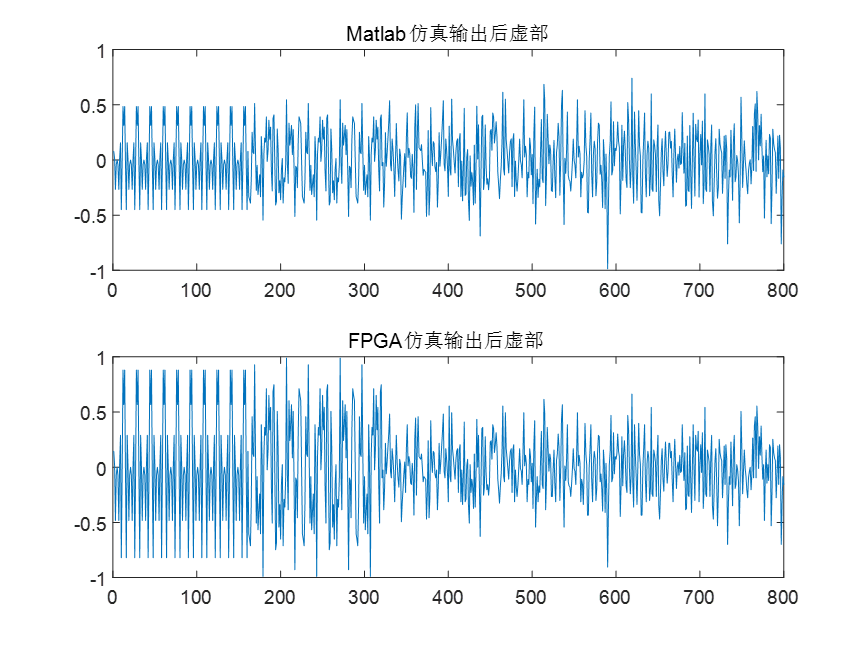

matlab对比结果:

实部

虚部

图形走势是一致的,只是幅度不相等,可能是IFFT核计算时会进行缩放,与Matlab仿真设置的缩放不一样,不过不影响。

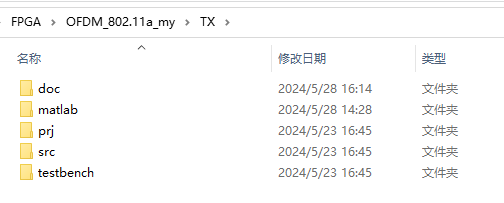

4.完整工程

获取完整工程链接:点此跳转,或者点击阅读原文跳转

完整工程包括,matlab仿真代码、matlab自动化对比代码、verilog HDL代码、仿真测试激励文件

完整工程

src文件夹里面包含所有的verilog HDL代码:

关注微信公众号获取完整工程: