目录

1. 布局

2. 布线

时钟电路做为产品内部的强辐射源,在设计阶段已经选用展频或者分频方案后,见另外接下来就需要对PCB的耦合路径进行规划设计。时钟电路具体的PCB设计具体要求如下:

1. 布局

结构干涉:时钟电路的晶振和法拉电容通常具有一定的元器件高度,比如如下图示的直插晶振长为6mm,直径2mm。这类直插晶振若垂直放置会倾斜,生产过程中在中转运输中发生碰撞导致晶振引脚断或靠近其它元器件导致电路短路的风险。该晶振的外壳为金属材质。所以这类晶振需要在PCB板上放倒放置,并与其它元器件3mm以上间距,并用电子固定胶固定。

因此时钟电路的PCB布局除EMC要求,还需要考虑结构干涉。这一点必须结合整个电路所用元器件的数据手册和产品的结构图纸来设计,元器件限高区需要在图纸上明确标注出来。通用要求是元器件与外壳间距至少3mm以上,若满足不了,需要酌情综合评估。

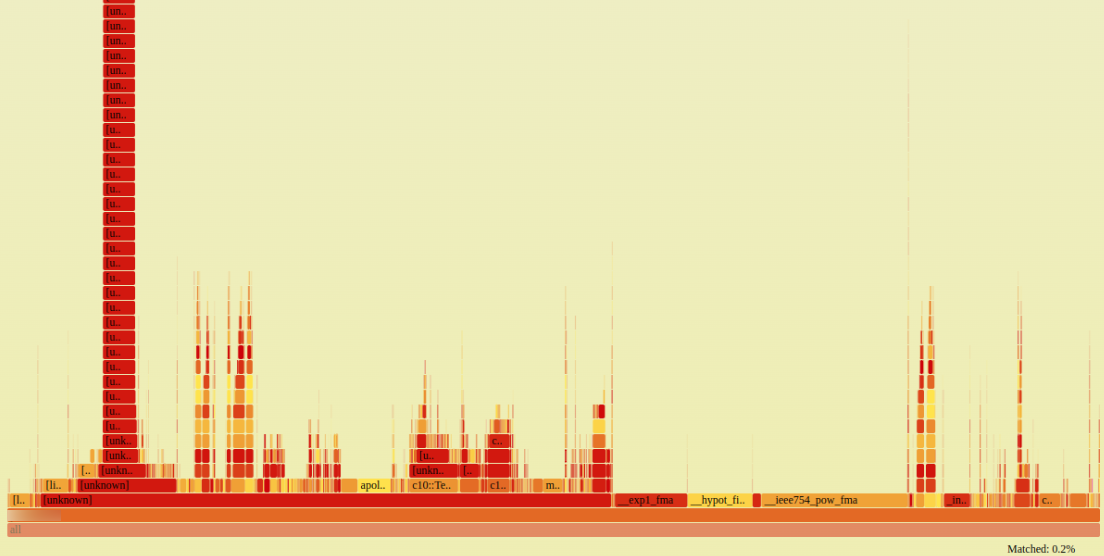

PCB布局位置:时钟电路尽量放在PCB板中心位置,不要放在板边。这样对于多个共用时钟的IC,可以避免某一个单一时钟线走线过长。而对于单一时钟电路,时钟电路在板内,地线可以对时钟线磁力线起的干扰起隔断作用。如下图示是时钟电路放在板边与板内的区别,可以看到放置板边的辐射源对外辐射量远大于放在PCB板中。这个规则对多数的辐射源都有效。

晶振及振荡电容尽可能靠近芯片引脚放置。时钟电路布局时应与芯片放置在同一层,尽量不要不同层,如下图示。这样的布局设计方案可使时钟信号的走线环路尽可能的小,根据公式远场的辐射电场E=AFI,其中A为环路面积,F为高频信号频率,I为高频信号电流。信号环路面积的A大小与远场的辐射电场E成正比,因此所有的类似时钟信号这类强辐射源的信号环路越小越好。

2. 布线

以避免打过孔,增加走线电感,走线尽量的短粗,满足长宽比<3为好。按长宽比等于3的计算,设长度为3mm,宽为1mm,铜厚为1盎司36um。

根据公式R=ρ*len/A,其中ρ为金属材料体电阻率,len为走线长度,单位mm;A为走线横截面积。按此公式试算后,上述例子的走线电阻约为3.75mΩ。如下图示

若设长度为10mm,宽为0.254mm时,其走线电阻将大幅增加至约0.5Ω。可见走线的长宽比对走线电阻是成反比的。

若结构或空间导致时钟电路与芯片放置在不同层,应尽可能的将晶振与振荡电容放置在芯片时钟引脚下方,过孔也只能打1个。因为过孔的存在会增加走线的寄生电感,从而加大信号振铃幅值。

晶振及时钟走线需要全程包地处理,包地线通常每隔200~300mil至少添加一个GND过孔。若频率较高的,根据时钟频率的带宽对应波长1/12间距打过孔。同时晶振本体四周可进行包地环设计,过孔打法与时钟线一致。如下图示。

时钟线的正下方投影区禁止布线,特别是平行走线,此方案的目的是减小时钟线的线间耦合。高频信号以最低阻抗路径返回,走线正下方投影区即是高频信号的最低阻抗路径。

本博客持续更新中,欢迎大家收藏与关注!

![正点原子[第二期]Linux之ARM(MX6U)裸机篇学习笔记-16讲 EPIT定时器](https://img-blog.csdnimg.cn/direct/2c1364a5c1894b57b6167b3832854144.png)