GPIO简介

GPIO(General Purpose Input Output)通用输入输出口

引脚电平:0V~3.3V,部分引脚可容忍5V

输出模式下可控制端口输出高低电平,用以驱动LED、控制蜂鸣器、模拟通信协议输出时序等

输入模式下可读取端口的高低电平或电压,用于读取按键输入、外接模块电平信号输入、ADC电压采集、模拟通信协议接收数据等

可配置为8种输入输出模式

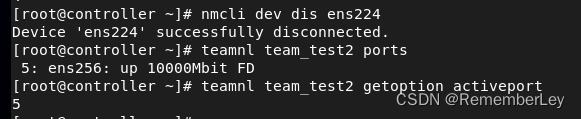

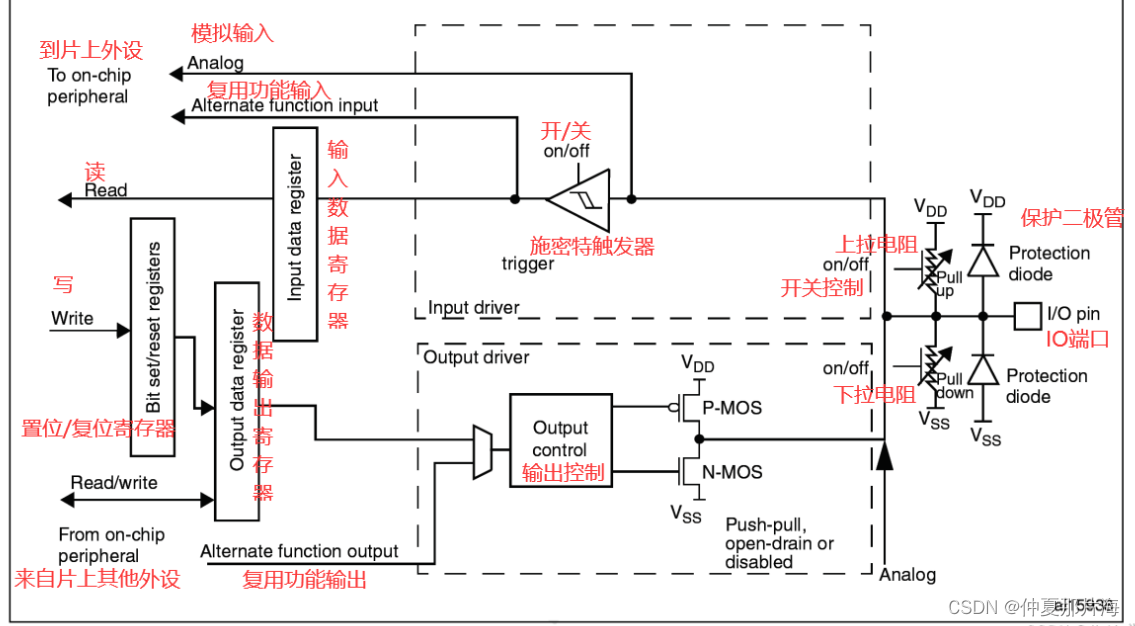

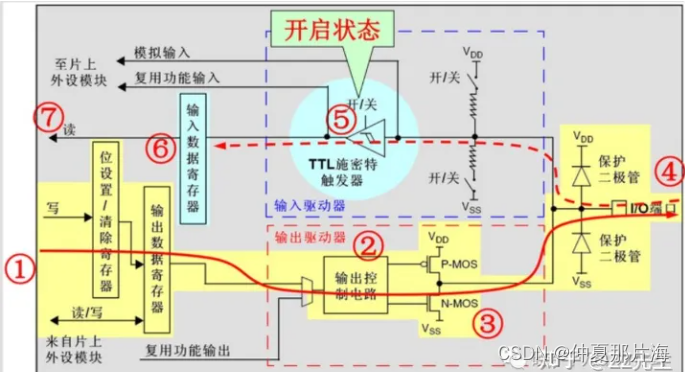

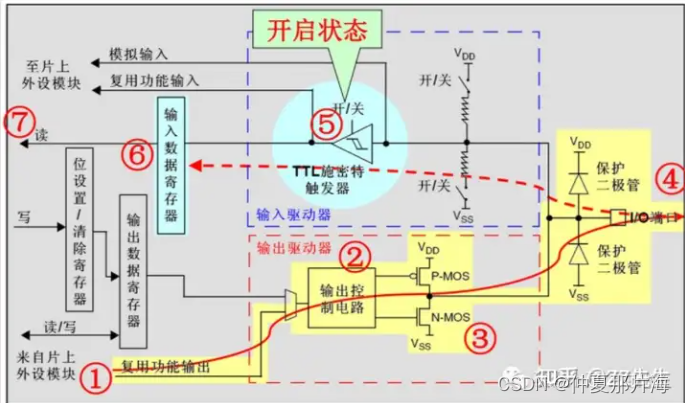

IO结构框图

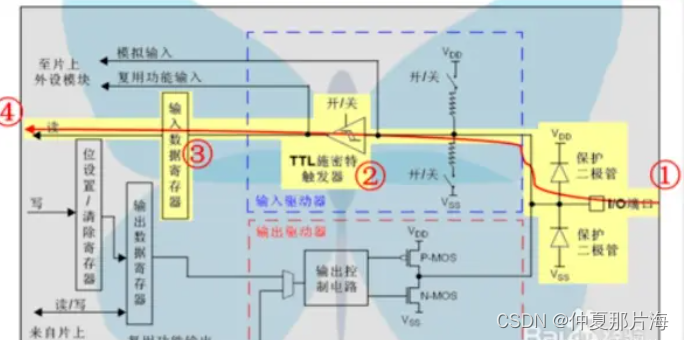

浮空输入

浮空输入(Floating Input)是一种引脚配置模式,用于接收外部信号,当没有外部信号输入时,引脚处于高阻抗状态。在这种状态下,引脚不连接到特定的电源或地,并且没有外部电阻将其固定在特定电平上。

浮空输入通常用于读取外部设备的信号,例如传感器或开关。当外部设备产生信号时,信号会通过电路连接到引脚上,从而改变引脚的电平状态。然而,当外部设备没有产生信号时,引脚没有被连接到特定的电平上,因此可能会受到电磁干扰的影响,导致引脚处于不确定的状态。为了避免不确定性,可以使用上拉电阻或下拉电阻来将引脚拉高或拉低,使其保持在已定义的电平上。

外部的电平信号通过左边编号1的I/O端口进入MCU,经过编号2的施密特触发器的整形送入编号3的“输入数据寄存器”,在“输入数据寄存器”的另一端(编号4),CPU可以随时读出I/O端口的电平状态。

【来源:https://zhuanlan.zhihu.com/p/377009763】

浮空输入在数字电路中是常见的配置模式,用于读取外部信号的状态,如按钮按下或开关状态。在使用浮空输入时,需要注意对引脚的电平状态进行适当的判断和处理,以确保正确读取外部信号并避免不确定性的影响。

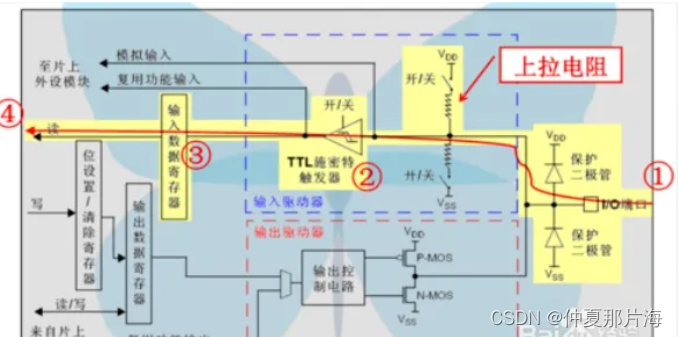

上拉输入

上拉输入(Pull-Up Input)是一种引脚配置模式,用于将引脚连接到正极电源(如VCC)通过一个上拉电阻,以确保引脚在没有外部信号输入时保持在高电平(通常是逻辑高)。

在上拉输入模式下,引脚的电路连接如下:

- 引脚通过一个大约几千欧姆的上拉电阻连接到正极电源(VCC)。

- 当没有外部信号输入时,上拉电阻将引脚拉高,使其保持在高电平状态。

上拉输入常用于读取外部设备的信号,例如开关或按钮。当外部设备没有产生信号时,引脚通过上拉电阻被拉高到逻辑高电平,从而确保引脚在没有输入时有一个已定义的状态。当外部设备通过连接到引脚来拉低引脚时,可以改变引脚的状态,例如按下按钮或改变开关状态。

输入上拉模式;与前面的浮空输入模式相比,仅仅是在数据通道上部,接入了一个上拉电阻,同样,CPU可以随时在“输入数据寄存器”的另一端,读出I/O端口的电平状态。

【来源:https://zhuanlan.zhihu.com/p/377009763】

需要注意的是,在使用上拉输入时,如果外部设备连接到引脚并拉低引脚,外部设备应具备足够的驱动能力以克服上拉电阻的作用,以确保引脚能够稳定地被拉低。

上拉输入是数字电路中常见的配置模式之一,用于提供引脚的默认状态和读取外部信号。在使用上拉输入时,需要根据具体的硬件和信号要求选择适当的上拉电阻值,并进行合适的信号处理和判断。

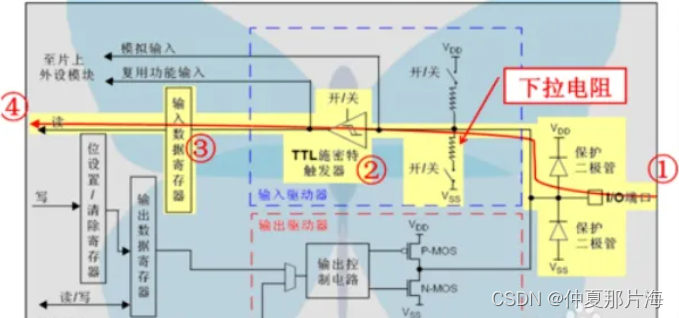

下拉输入

下拉输入(Pull-Down Input)是一种引脚配置模式,用于将引脚连接到地(GND)通过一个下拉电阻,以确保引脚在没有外部信号输入时保持在低电平(通常是逻辑低)。

在下拉输入模式下,引脚的电路连接如下:

- 引脚通过一个大约几千欧姆的下拉电阻连接到地(GND)。

- 当没有外部信号输入时,下拉电阻将引脚拉低,使其保持在低电平状态。

下拉输入常用于读取外部设备的信号,例如开关或按钮。当外部设备没有产生信号时,引脚通过下拉电阻被拉低到逻辑低电平,从而确保引脚在没有输入时有一个已定义的状态。当外部设备通过连接到引脚来拉高引脚时,可以改变引脚的状态,例如按下按钮或改变开关状态。

输入下拉模式;数据通道的下部,接入了一个下拉电阻。

【来源:https://zhuanlan.zhihu.com/p/377009763】

需要注意的是,在使用下拉输入时,如果外部设备连接到引脚并拉高引脚,外部设备应具备足够的驱动能力以克服下拉电阻的作用,以确保引脚能够稳定地被拉高。

下拉输入是数字电路中常见的配置模式之一,用于提供引脚的默认状态和读取外部信号。在使用下拉输入时,需要根据具体的硬件和信号要求选择适当的下拉电阻值,并进行合适的信号处理和判断。

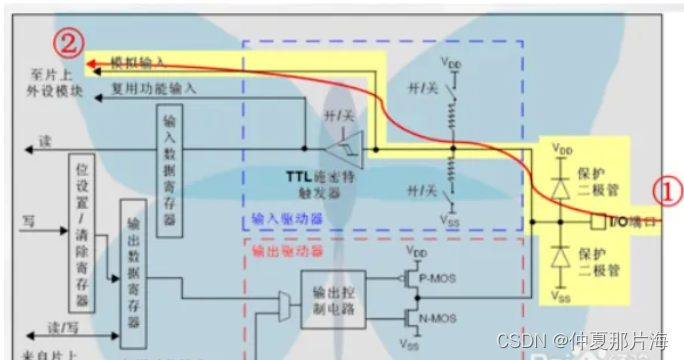

模拟输入

模拟输入(Analog Input)是一种引脚配置模式,用于读取外部模拟信号的电压或电流,并将其转换为数字形式以供处理。

在模拟输入模式下,引脚被连接到外部设备或传感器,以接收连续变化的模拟信号。引脚通常与一个模拟到数字转换器(ADC)相结合,该转换器将模拟信号转换为数字形式,以便后续的数字信号处理。

模拟输入可以用于测量各种类型的模拟信号,如温度、光强、声音等。外部设备或传感器将模拟信号传递给引脚,引脚通过ADC将模拟信号转换为数字值。这些数字值可以通过处理和分析,用于监测、控制或生成相应的反馈信号。

模拟输入模式;信号从左边编号1的端口进入,从右边编号2的一端直接进入ADC模块。这里我们看到所有的上拉、下拉电阻和施密特触发器,均处于断开状态,因此“输入数据寄存器”将不能反映端口上的电平状态,也就是说,模拟输入配置下,CPU不能在“输入数据寄存器”上读到有效的数据。

【来源:https://zhuanlan.zhihu.com/p/377009763】

在使用模拟输入时,需要考虑以下几点:

- 确保引脚的电压或电流范围与外部模拟信号相匹配。

- 选择合适的ADC分辨率和采样率,以满足应用需求。

- 进行适当的信号处理和滤波,以提高信号质量和减小噪声干扰。

需要注意的是,模拟输入与数字输入(Digital Input)有所不同。数字输入是读取逻辑高或逻辑低的离散信号,而模拟输入读取连续变化的模拟信号。模拟输入通常需要更高的精度和处理复杂性,以满足对模拟信号的准确测量和分析的要求。

开漏输出

开漏输出(Open-Drain Output)是一种引脚输出配置模式,其中引脚可以连接到外部负载或电路,但只能拉低(连接到地)而不能主动拉高(连接到电源)。

在开漏输出模式下,引脚的输出状态可以分为两种:

- 拉低状态:引脚处于低电平状态,连接到地,形成一个低阻抗通路,允许电流从引脚流过,从而将外部负载拉低。

- 高阻状态:引脚处于高阻抗状态,不连接到任何电源或地,形成一个高阻抗断路,外部负载不受引脚控制。

开漏输出常用于驱动外部负载或与其他开漏输出设备进行电平兼容的通信,如I2C总线。通过使用外部上拉电阻,可以将开漏输出与其他设备或电路相连接,以实现协调的电平转换。

开漏输出模式;当CPU在左边的编号1端通过位设置/清除寄存器,或输出数据寄存器写入数据后,该数据位将通过编号2的输出控制电路传送到编号4的I/O端口,如果CPU写入的是逻辑“1”,则编号3的N-MOS管将处于关闭状态,此时I/O端口的电平将由外部的上拉电阻决定,如果CPU写入的是逻辑“0”,则编号3的N-MOS管将处于开启状态,此时I/O端口的电平被编号3的N-MOS管拉到了VSS的零电位。在图的上半部,施密特触发器处于开启状态,这意味着CPU可以在“输入数据寄存器”的另一端,随时监控I/O端口的状态;通过这个特性,还实现了虚拟的I/O端口双向通信:只要CPU输出逻辑“1”,由于编号3的N-MOS管处于关闭状态,I/O端口的电平将完全由外部电路决定,因此,CPU可以在“输入数据寄存器”读到外部电路的信号,而不是它自己输出的逻辑“1”。

【来源:https://zhuanlan.zhihu.com/p/377009763】

在使用开漏输出时,需要注意以下几点:

- 引脚在拉低状态时可以提供较大的输出电流,但在拉高状态时不能提供输出电流。因此,需要通过外部上拉电阻将引脚拉高到所需的电平。

- 在连接多个开漏输出设备时,需要确保只有一个设备处于拉低状态,以避免短路和冲突。

- 开漏输出可以实现电平的逻辑与或非操作,但不能直接实现逻辑与非操作,因为无法主动拉高。

总的来说,开漏输出提供了一种灵活的输出模式,适用于与其他设备或电路进行电平兼容的通信和驱动外部负载的应用场景。

推挽输出

推挽输出(Push-Pull Output)是一种引脚输出配置模式,其中引脚可以主动拉高(连接到电源)和拉低(连接到地),以提供全面的输出控制能力。

在推挽输出模式下,引脚的输出状态可以分为两种:

拉高状态:引脚处于高电平状态,连接到电源(如VCC),提供正向电压和电流输出。

拉低状态:引脚处于低电平状态,连接到地(GND),提供零电压和电流输出。

推挽输出允许引脚在不同电平之间切换,可以主动驱动外部负载或与其他设备进行电平兼容的通信。它提供了较低的输出阻抗,因此可以提供较高的输出电流能力,适用于驱动各种类型的负载。

推免输出模式;在开漏输出模式的基础上,推挽输出模式仅仅是在编号2的输出控制电路之后,增加了一个P-MOS管。当输出逻辑“1”时,编号3处的P-MOS管导通,而下方的N-MOS管截止,达到输出高电平的目的。当输出逻辑“0”时,编号3处的P-MOS管截止,而下方的N-MOS管导通,达到输出低电平的目的。在这个模式下,CPU仍然可以从“输入数据寄存器”读到外部电路的信号。

【来源:https://zhuanlan.zhihu.com/p/377009763】

在使用推挽输出时,需要注意以下几点:

- 确保引脚的输出电流能力与所驱动的负载要求相匹配。

- 在与其他设备进行通信时,确保推挽输出与相应设备的输入电平兼容。

- 避免短路和冲突,确保在同时连接多个推挽输出设备时只有一个设备处于拉高状态。

推挽输出是最常见和常用的输出模式,可广泛应用于数字电路、微控制器和集成电路中,用于驱动各种外部负载和与其他设备进行可靠的通信。

推挽复用输出模式,同样的道理,编号2的输出控制电路的输入,与复用功能的输出端相连,此时输出数据寄存器被从输出通道断开了。

【来源:https://zhuanlan.zhihu.com/p/377009763】

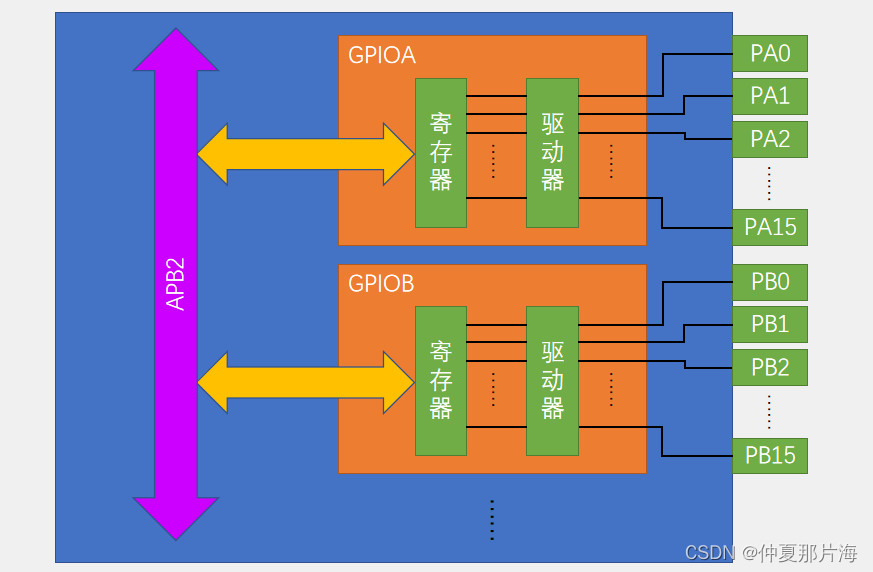

GPIO基本结构

GPIO相关寄存器

4 个 32 位 配 置 寄 存 器

GPIOx_MODER 模式寄存器

GPIOx_OTYPER 输出模式寄存器

GPIOx_ OSPEEDR 输出速度寄存器

GPIOx_PUPDR 上拉下拉寄存器

2 个 32 位数据寄存器

GPIOx_IDR 输入数据寄存器

GPIOx_ODR 输出数据寄存器

1个 32 位置位 / 复位寄存器

GPIOx_BSRR 置位 / 复位寄存器

2 个 32 位复用功能寄存器

GPIOx_AFRH

GPIOx_AFRL

GPIO库函数点灯

库函数版

//1打开时钟

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOC, ENABLE);

//2设置输入输出模式

GPIO_InitTypeDef GPIO_InitStructure;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP;

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_13;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_10MHz;

GPIO_Init(GPIOC, &GPIO_InitStructure);

//3输出高低电平

GPIO_ResetBits(GPIOC, GPIO_Pin_13);//输出低电平

GPIO_SetBits(GPIOC, GPIO_Pin_13);//输出高电平

![[GXYCTF 2019]Ping Ping Ping(内联执行)、[鹤城杯 2021]EasyP ($_SERVER)](https://img-blog.csdnimg.cn/direct/c982ab4ff8aa4db59ec4fdc727bda19a.png)