目录

1.MTU基本功能

2.MBIST

3.小结

1.MTU基本功能

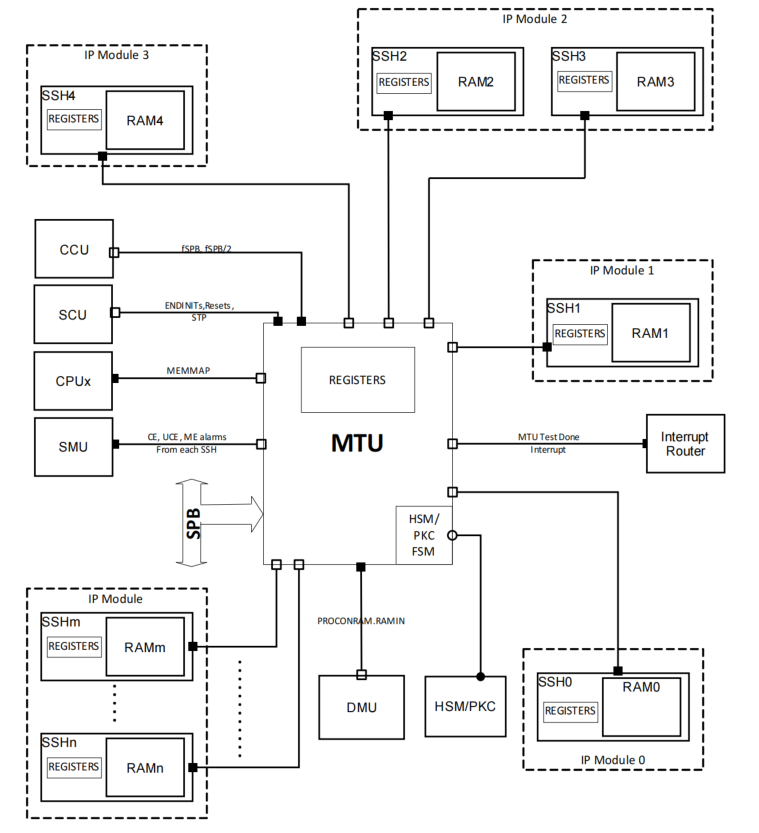

在TC3xx中,MTU(Memory Unit Test)被用来管理控制芯片内部各种RAM的测试、初始化和数据完整性检查。

既然MTU主要是管理和控制,那干活的想必另有他人。所以在该平台中,我们可以看到SRAM周围设计了特别的数字逻辑电路,称之为SRAM Support Hardware(SSH);SSH主要用于控制其关联SRAM的ECC、MBIST(Memory Built In Self Test)等。

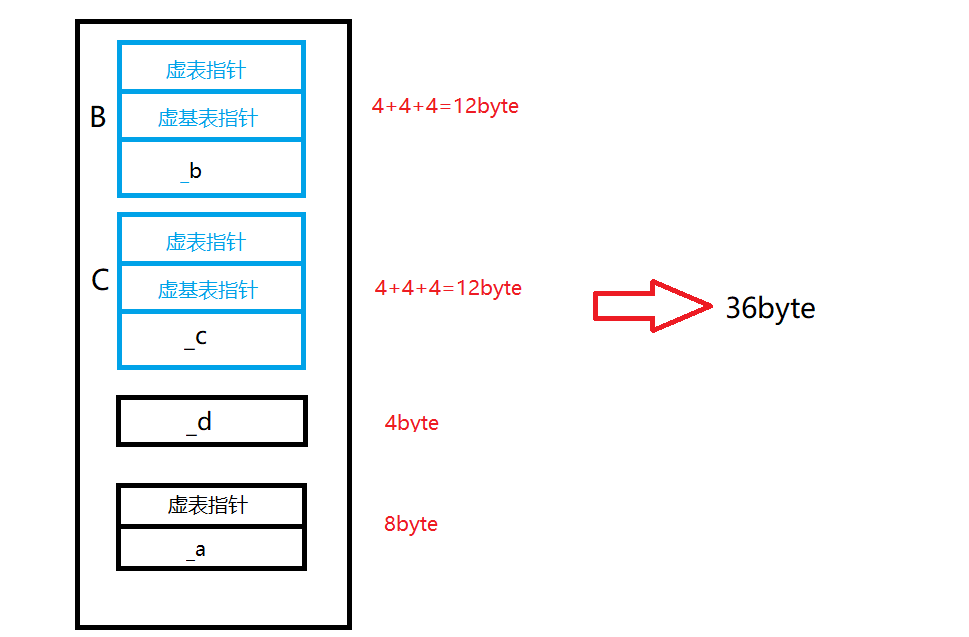

因此MTU、SSH、RAM在TC3xx的结构示意如下:

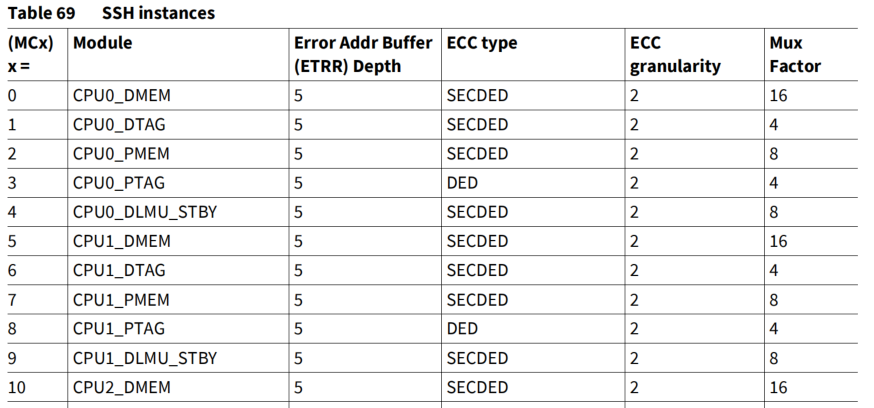

其中,CPU通过SPB总线访问MTU;MTU针对每个SSH又都有一套独立寄存器,可以配置不同的SRAM测试类型、控制SSH的功能运行。 根据TC39x-B UserManual描述,在该平台中设计了多达96个SSH(包括预留),截图如下:

这意味着,在不同IP的内部SRAM也可以通过MTU和SSH配置进行测试,即使CPU不能直接访问该SRAM。

值得注意的是,SSH寄存器只能通过MTU->SSH这样的路径进行访问,因此在访问效率上会比直接通过SPB访问寄存器要慢一些。

2.MBIST

MBIST是一种功能安全机制,用于检查SRAM内部Cell是否出现永久随机硬件失效。TC3xx使用MTU来实现MBIST,在UserMannul里仅提供了Non-Destructive Test的实现方法、功耗和耗时。

这是为什么呢?

因为在ISO26262中,SRAM的Cell故障被认为是潜伏故障,而在一次驾驶循环内至少得有一次测试用于覆盖潜伏故障,所以使用者有权决定在MCU启动、APP运行和下电这三个阶段任意时刻进行MBIST,因此这种非破坏性测试(NDT)是最为友好。

NDT允许在程序运行时进行memory的测试,并且不会破坏当前memory里的应用数据。之所以能这样,是因为该算法的运行逻辑如下:

- 从SRAM读取一个word,包括数据+ECC bits,记为"r" ;

- 对上述word取反,并写回SRAM,记为 “w*”;

- 再次读取word,记为 “ r* ”;

- 对上述word再次取反,写回SRAM,记为“w”;

其中 “ * ”表示始终对原始数据相反,可以看到要保证应用数据不被污染,写"w"的次数必须是偶数次,因此NDT的算法在时间复杂度上至少为4N。

执行MBIST期间,每次发生读访问,SRAM自身的ECC机制会计算此次读出数据的校验码,并检查该校验码是否与存入该数据时计算的校验码一致。如果不一致,则会产生错误并通知SMU或者产生中断。

不过,在执行MBIST前还需要注意如下事项:

- 测试期间,被测试SRAM不可访问;

- 测试前,SRAM应该被正确初始化。

这些事项与我们设计Online Bist任务息息相关。

在CP AUTOSAR RamTst模块里提出了Foreground Test和Background Test两个概念;其中Foreground Test是同步测试,不可以被中断;Backgroud Test由OS或者调度器周期调度,它可以在每个测试序列完成时被打断。

由于Background Test涉及到数据一致和中断概念,目前用的比较少,比较常见的就是在上电前执行NDT,运行期间选择关键memory进行测试。

3.小结

本篇我们讲解了MTU基本功能和MBIST基本概念,下一篇我们继续讲解MTU如何配置NDT算法。

![[CR]厚云填补_M3R-CR Dataset and Align-CR](https://img-blog.csdnimg.cn/direct/be43083524d644cf829a629fdf15c377.png)