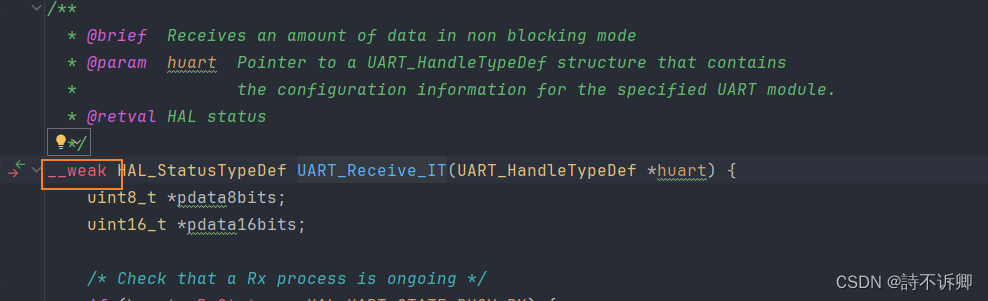

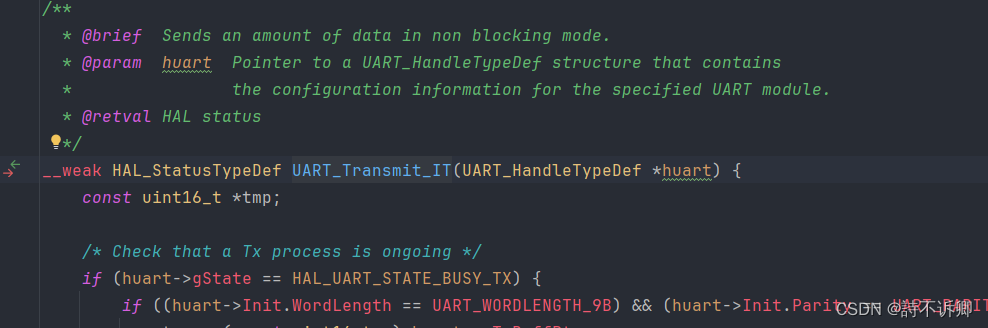

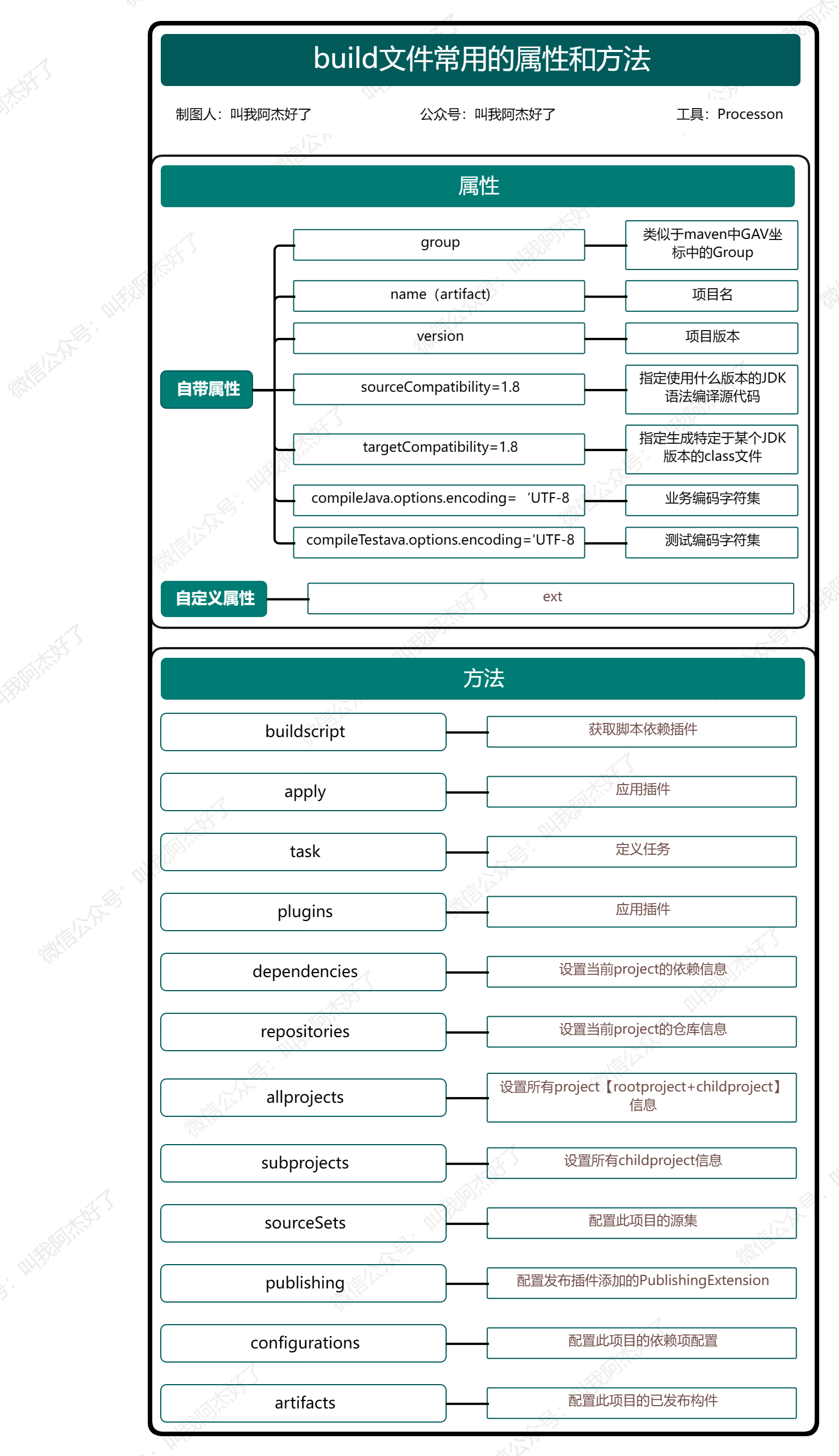

结合hal库封装的中断处理函数 使用rt-thread内部的rt-ringbuffer数据结构源码 改造hal库串口部分的源码,将内部静态方法变为弱引用的函数,方便重写 标志位采用信号量或变量的两种方式,内部数据分配方式采用动态和静态两种方式

# ifndef TX_STM32_F4_DRV_UART_OS_H # define TX_STM32_F4_DRV_UART_OS_H # include "drv_common.h" # define UART_USE_OS_FLAG ( 0 ) # define UART_BUF_STATIC_METHOD ( 1 ) # ifndef UART_CONTROLLER_NUM # define UART_CONTROLLER_NUM 1 # endif # define BAUD_RATE_2400 2400 # define BAUD_RATE_4800 4800 # define BAUD_RATE_9600 9600 # define BAUD_RATE_19200 19200 # define BAUD_RATE_38400 38400 # define BAUD_RATE_57600 57600 # define BAUD_RATE_115200 115200 # define BAUD_RATE_230400 230400 # define BAUD_RATE_460800 460800 # define BAUD_RATE_500000 500000 # define BAUD_RATE_921600 921600 # define BAUD_RATE_2000000 2000000 # define BAUD_RATE_2500000 2500000 # define BAUD_RATE_3000000 3000000 # define DATA_BITS_5 5 # define DATA_BITS_6 6 # define DATA_BITS_7 7 # define DATA_BITS_8 8 # define DATA_BITS_9 9 # define STOP_BITS_1 0 # define STOP_BITS_2 1 # define STOP_BITS_3 2 # define STOP_BITS_4 3 # define PARITY_NONE 0 # define PARITY_ODD 1 # define PARITY_EVEN 2 # define SERIAL_FLOWCONTROL_CTSRTS 1 # define SERIAL_FLOWCONTROL_NONE 0 # define UART_FLAG_IT_TX ( 1 << 1 ) # define UART_FLAG_IT_RX ( 1 << 2 ) # define UART_FLAG_IT_TX_RX ( UART_FLAG_IT_TX| UART_FLAG_IT_RX) # define UART_FLAG_DMA_TX ( 1 << 3 ) # define UART_FLAG_DMA_RX ( 1 << 4 ) # define UART_FLAG_DMA_TX_RX ( UART_FLAG_DMA_TX| UART_FLAG_DMA_RX) struct uart_configuration {

uint32_t baud_rate;

uint32_t data_bits: 4 ;

uint32_t stop_bits: 2 ;

uint32_t parity: 2 ;

uint32_t flowcontrol: 1 ;

uint32_t reserved: 23 ;

} ;

typedef struct stm32_uart_controller * uart_controller_t ;

typedef void ( * uart_rx_notify) ( uart_controller_t controller, uint32_t size) ;

typedef void ( * uart_tx_cpt_notify) ( uart_controller_t controller) ;

struct stm32_uart_controller {

UART_HandleTypeDef handle;

# if UART_USE_OS_FLAG * tx_sem;

TX_SEMAPHORE * rx_sem;

# else volatile uint32_t tx_sem_flag;

volatile uint32_t rx_sem_flag;

# endif ;

uart_tx_cpt_notify tx_complete;

struct rt_ringbuffer * tx_buffer;

struct rt_ringbuffer * rx_buffer;

} ;

void bsp_UartParDefaultSet ( USART_TypeDef * uart) ;

void bsp_UartParSet ( USART_TypeDef * uart, struct uart_configuration * configuration) ;

void bsp_UartParNotifySet ( USART_TypeDef * uart, uart_rx_notify rx_notify, uart_tx_cpt_notify tx_cpt_notify) ;

void bsp_UartParSemSet ( USART_TypeDef * uart, uint8_t rx_sem_flag, uint8_t tx_sem_flag) ;

void bsp_InitUart ( USART_TypeDef * uart, uint16_t tx_size, uint16_t rx_size) ;

void bsp_DeInitUart ( USART_TypeDef * uart) ;

uint16_t uart_read_data ( USART_TypeDef * uart, uint8_t * data, uint16_t len) ;

uint16_t uart_write_data ( USART_TypeDef * uart, uint8_t * data, uint16_t len) ;

# endif

# include "drv_common.h" # include "drv_uart_os.h" # define SEM_NOTIFY_FLAG ( 1 ) # define SET_UN_NOTIFY_FLAG ( 0 ) # define uart_idx_check ( uart) do { idx = stm32_uart_controller_idx_get ( uart) ; if ( idx < 0 || idx >= UART_CONTROLLER_NUM) return ; } while ( 0 ) enum {

UART1_IDX,

UART2_IDX,

UART3_IDX,

UART4_IDX,

UART5_IDX,

UART6_IDX,

} ;

# if ( UART_BUF_STATIC_METHOD) # if ( UART_CONTROLLER_NUM >= 1 ) # define COM1_TX_LEN 2048 # define COM1_RX_LEN 2048 static uint8_t buf_0_tx[ COM1_TX_LEN] , buf_0_rx[ COM1_RX_LEN] ;

static struct rt_ringbuffer ringbuffer_tx_0 = { . buffer_size= COM1_TX_LEN} ;

static struct rt_ringbuffer ringbuffer_rx_0 = { . buffer_size= COM1_RX_LEN} ;

# endif # if ( UART_CONTROLLER_NUM >= 2 ) # define COM2_TX_LEN 1024 # define COM2_RX_LEN 1024 static uint8_t buf_1_tx[ COM2_TX_LEN] , buf_1_rx[ COM2_RX_LEN] ;

static struct rt_ringbuffer ringbuffer_tx_1= { . buffer_size= COM2_TX_LEN} ;

static struct rt_ringbuffer ringbuffer_rx_1= { . buffer_size= COM2_RX_LEN} ;

# endif # if ( UART_CONTROLLER_NUM >= 3 ) # define COM3_TX_LEN 1024 # define COM3_RX_LEN 1024 static uint8_t buf_2_tx[ COM3_TX_LEN] , buf_2_rx[ COM3_RX_LEN] ;

static struct rt_ringbuffer ringbuffer_tx_2= { . buffer_size= COM3_TX_LEN} ;

static struct rt_ringbuffer ringbuffer_rx_2= { . buffer_size= COM3_RX_LEN} ;

# endif # if ( UART_CONTROLLER_NUM >= 4 ) # define COM4_TX_LEN 1024 # define COM4_RX_LEN 1024 static uint8_t buf_3_tx[ COM4_TX_LEN] , buf_3_rx[ COM4_RX_LEN] ;

static struct rt_ringbuffer ringbuffer_tx_3= { . buffer_size= COM4_TX_LEN} ;

static struct rt_ringbuffer ringbuffer_rx_3= { . buffer_size= COM4_RX_LEN} ;

# endif static uint8_t * uart_static_buf[ ] [ 4 ] = {

# define buf_item ( tx, rx, tx_buf, rx_buf) ( uint8_t * ) & ( tx) , ( uint8_t * ) & ( rx) , tx_buf, rx_buf# if ( UART_CONTROLLER_NUM >= 1 ) { buf_item ( ringbuffer_tx_0, ringbuffer_rx_0, buf_0_tx, buf_0_rx) } ,

# endif # if ( UART_CONTROLLER_NUM >= 2 ) { buf_item ( ringbuffer_tx_1, ringbuffer_rx_1, buf_1_tx, buf_1_rx) } ,

# endif # if ( UART_CONTROLLER_NUM >= 3 ) { buf_item ( ringbuffer_tx_2, ringbuffer_rx_2, buf_2_tx, buf_2_rx) } ,

# endif # if ( UART_CONTROLLER_NUM >= 4 ) { buf_item ( ringbuffer_tx_3, ringbuffer_rx_2, buf_3_tx, buf_3_rx) } ,

# endif } ;

# endif static struct stm32_uart_controller controllers[ UART_CONTROLLER_NUM] = { 0 } ;

static inline int stm32_uart_controller_idx_get ( USART_TypeDef * uart) {

# define idx_return ( val) { return val; } switch ( ( uint32_t ) uart) {

case ( uint32_t ) USART1: idx_return ( UART1_IDX)

case ( uint32_t ) USART2: idx_return ( UART2_IDX)

case ( uint32_t ) USART3: idx_return ( UART3_IDX)

case ( uint32_t ) UART4: idx_return ( UART4_IDX)

case ( uint32_t ) UART5: idx_return ( UART5_IDX)

case ( uint32_t ) USART6: idx_return ( UART6_IDX)

}

# undef idx_return return - 1 ;

}

static inline void stm32_uart_irq_enable_cnf ( USART_TypeDef * uart) {

# define uart_irq_cnf ( irq, pp, sp) { HAL_NVIC_SetPriority ( irq, pp, sp) ; HAL_NVIC_EnableIRQ ( irq) ; } switch ( ( uint32_t ) uart) {

case ( uint32_t ) USART1: uart_irq_cnf ( USART1_IRQn, 0 , 0 )

case ( uint32_t ) USART2: uart_irq_cnf ( USART2_IRQn, 0 , 0 )

case ( uint32_t ) USART3: uart_irq_cnf ( USART3_IRQn, 0 , 0 )

case ( uint32_t ) UART4: uart_irq_cnf ( UART4_IRQn, 0 , 0 )

case ( uint32_t ) UART5: uart_irq_cnf ( UART5_IRQn, 0 , 0 )

case ( uint32_t ) USART6: uart_irq_cnf ( USART6_IRQn, 0 , 0 )

}

# undef uart_irq_cnf }

static inline void stm32_uart_irq_disable_cnf ( USART_TypeDef * uart) {

# define uart_irq_disable_cnf ( irq) { HAL_NVIC_DisableIRQ ( irq) ; } switch ( ( uint32_t ) uart) {

case ( uint32_t ) USART1: uart_irq_disable_cnf ( USART1_IRQn)

case ( uint32_t ) USART2: uart_irq_disable_cnf ( USART2_IRQn)

case ( uint32_t ) USART3: uart_irq_disable_cnf ( USART3_IRQn)

case ( uint32_t ) UART4: uart_irq_disable_cnf ( UART4_IRQn)

case ( uint32_t ) UART5: uart_irq_disable_cnf ( UART5_IRQn)

case ( uint32_t ) USART6: uart_irq_disable_cnf ( USART6_IRQn)

}

# undef uart_irq_disable_cnf }

void bsp_UartParDefaultSet ( USART_TypeDef * uart) {

struct uart_configuration default_cnf = {

. baud_rate= BAUD_RATE_115200,

. parity= PARITY_NONE,

. data_bits= DATA_BITS_8,

. flowcontrol= SERIAL_FLOWCONTROL_NONE,

. stop_bits = STOP_BITS_1

} ;

bsp_UartParSet ( uart, & default_cnf) ;

bsp_UartParSemSet ( uart, 1 , 1 ) ;

}

void bsp_UartParSet ( USART_TypeDef * uart, struct uart_configuration * cfg) {

int idx;

uart_idx_check ( uart) ;

if ( cfg == NULL ) return ;

controllers[ idx] . handle. Instance = uart;

controllers[ idx] . handle. Init. BaudRate = cfg-> baud_rate;

controllers[ idx] . handle. Init. Mode = UART_MODE_TX_RX;

controllers[ idx] . handle. Init. OverSampling = UART_OVERSAMPLING_16;

{

switch ( cfg-> flowcontrol) {

case SERIAL_FLOWCONTROL_NONE:

controllers[ idx] . handle. Init. HwFlowCtl = UART_HWCONTROL_NONE;

break ;

case SERIAL_FLOWCONTROL_CTSRTS:

controllers[ idx] . handle. Init. HwFlowCtl = UART_HWCONTROL_RTS_CTS;

break ;

default :

controllers[ idx] . handle. Init. HwFlowCtl = UART_HWCONTROL_NONE;

break ;

}

switch ( cfg-> data_bits) {

case DATA_BITS_8:

if ( cfg-> parity == PARITY_ODD || cfg-> parity == PARITY_EVEN)

controllers[ idx] . handle. Init. WordLength = UART_WORDLENGTH_9B;

else

controllers[ idx] . handle. Init. WordLength = UART_WORDLENGTH_8B;

break ;

case DATA_BITS_9:

controllers[ idx] . handle. Init. WordLength = UART_WORDLENGTH_9B;

break ;

default :

controllers[ idx] . handle. Init. WordLength = UART_WORDLENGTH_8B;

break ;

}

switch ( cfg-> stop_bits) {

case STOP_BITS_1:

controllers[ idx] . handle. Init. StopBits = UART_STOPBITS_1;

break ;

case STOP_BITS_2:

controllers[ idx] . handle. Init. StopBits = UART_STOPBITS_2;

break ;

default :

controllers[ idx] . handle. Init. StopBits = UART_STOPBITS_1;

break ;

}

switch ( cfg-> parity) {

case PARITY_NONE:

controllers[ idx] . handle. Init. Parity = UART_PARITY_NONE;

break ;

case PARITY_ODD:

controllers[ idx] . handle. Init. Parity = UART_PARITY_ODD;

break ;

case PARITY_EVEN:

controllers[ idx] . handle. Init. Parity = UART_PARITY_EVEN;

break ;

default :

controllers[ idx] . handle. Init. Parity = UART_PARITY_NONE;

break ;

}

}

}

void bsp_UartParNotifySet ( USART_TypeDef * uart, uart_rx_notify rx_notify, uart_tx_cpt_notify tx_cpt_notify) {

int idx;

uart_idx_check ( uart) ;

TX_INTERRUPT_SAVE_AREA

TX_DISABLE

controllers[ idx] . rx_indicate = rx_notify;

controllers[ idx] . tx_complete = tx_cpt_notify;

TX_RESTORE

}

void bsp_UartParSemSet ( USART_TypeDef * uart, uint8_t rx_sem_flag, uint8_t tx_sem_flag) {

int idx;

uart_idx_check ( uart) ;

# if UART_USE_OS_FLAG if ( tx_sem_flag) {

controllers[ idx] . tx_sem = tx_malloc ( sizeof ( TX_SEMAPHORE) ) ;

tx_semaphore_create ( controllers[ idx] . tx_sem, "tx_sem" , 1 ) ;

}

if ( rx_sem_flag) {

controllers[ idx] . rx_sem = tx_malloc ( sizeof ( TX_SEMAPHORE) ) ;

tx_semaphore_create ( controllers[ idx] . rx_sem, "rx_sem" , 1 ) ;

}

# else [ idx] . tx_sem_flag = SET_UN_NOTIFY_FLAG;

controllers[ idx] . rx_sem_flag = SET_UN_NOTIFY_FLAG;

# endif }

void bsp_InitUart ( USART_TypeDef * uart, uint16_t tx_size, uint16_t rx_size) {

int idx;

uart_idx_check ( uart) ;

void * buf;

HAL_UART_Init ( & ( controllers[ idx] . handle) ) ;

if ( tx_size != 0 || rx_size != 0 ) {

stm32_uart_irq_enable_cnf ( uart) ;

}

if ( tx_size != 0 ) {

# if UART_BUF_STATIC_METHOD [ idx] . tx_buffer = ( struct rt_ringbuffer * ) uart_static_buf[ idx] [ 0 ] ;

rt_ringbuffer_init ( controllers[ idx] . tx_buffer, uart_static_buf[ idx] [ 2 ] ,

controllers[ idx] . tx_buffer-> buffer_size) ;

# else [ idx] . tx_buffer = tx_malloc ( sizeof ( struct rt_ringbuffer ) ) ;

buf = tx_malloc ( tx_size) ;

rt_ringbuffer_init ( controllers[ idx] . tx_buffer, buf, tx_size) ;

# endif }

if ( rx_size != 0 ) {

# if UART_BUF_STATIC_METHOD [ idx] . rx_buffer = ( struct rt_ringbuffer * ) uart_static_buf[ idx] [ 1 ] ;

rt_ringbuffer_init ( controllers[ idx] . rx_buffer, uart_static_buf[ idx] [ 3 ] ,

controllers[ idx] . rx_buffer-> buffer_size) ;

# else [ idx] . rx_buffer = tx_malloc ( sizeof ( struct rt_ringbuffer ) ) ;

buf = tx_malloc ( tx_size) ;

rt_ringbuffer_init ( controllers[ idx] . rx_buffer, buf, rx_size) ;

# endif if ( controllers[ idx] . handle. Init. Parity != UART_PARITY_NONE) {

__HAL_UART_ENABLE_IT ( & controllers[ idx] . handle, UART_IT_PE) ;

}

__HAL_UART_ENABLE_IT ( & controllers[ idx] . handle, UART_IT_ERR) ;

__HAL_UART_ENABLE_IT ( & controllers[ idx] . handle, UART_IT_RXNE) ;

}

}

void bsp_DeInitUart ( USART_TypeDef * uart) {

int idx;

uart_idx_check ( uart) ;

if ( controllers[ idx] . rx_buffer || controllers[ idx] . tx_buffer) {

stm32_uart_irq_disable_cnf ( uart) ;

}

HAL_UART_DeInit ( & ( controllers[ idx] . handle) ) ;

# if UART_BUF_STATIC_METHOD # else if ( controllers[ idx] . rx_buffer) tx_free ( controllers[ idx] . rx_buffer) ;

if ( controllers[ idx] . tx_buffer) tx_free ( controllers[ idx] . tx_buffer) ;

# endif # if UART_USE_OS_FLAG if ( controllers[ idx] . rx_sem) {

tx_semaphore_delete ( controllers[ idx] . rx_sem) ;

tx_free ( controllers[ idx] . rx_sem) ;

}

if ( controllers[ idx] . tx_sem) {

tx_semaphore_delete ( controllers[ idx] . tx_sem) ;

tx_free ( controllers[ idx] . tx_sem) ;

}

# endif memset ( controllers + idx, 0 , sizeof ( struct stm32_uart_controller ) ) ;

}

uint16_t uart_read_data ( USART_TypeDef * uart, uint8_t * data, uint16_t len) {

int idx;

idx = stm32_uart_controller_idx_get ( uart) ;

if ( idx < 0 || idx >= UART_CONTROLLER_NUM) return 0 ;

if ( controllers[ idx] . rx_buffer) {

return rt_ringbuffer_get ( controllers[ idx] . rx_buffer, data, len) ;

}

HAL_UART_Receive ( & ( controllers[ idx] . handle) , data, len, HAL_MAX_DELAY) ;

return len;

}

uint16_t uart_write_data ( USART_TypeDef * uart, uint8_t * data, uint16_t len) {

int idx;

idx = stm32_uart_controller_idx_get ( uart) ;

if ( idx < 0 || idx >= UART_CONTROLLER_NUM) return 0 ;

if ( controllers[ idx] . tx_buffer) {

# if ( UART_USE_OS_FLAG == 0 ) [ idx] . tx_sem_flag = SEM_NOTIFY_FLAG;

# endif rt_ringbuffer_put ( controllers[ idx] . tx_buffer, data, len) ;

__HAL_UART_ENABLE_IT ( & ( controllers[ idx] . handle) , UART_IT_TXE) ;

# if UART_USE_OS_FLAG if ( controllers[ idx] . tx_sem) {

tx_semaphore_get ( ( controllers[ idx] . tx_sem) , TX_WAIT_FOREVER) ;

} else {

while ( controllers[ idx] . handle. gState != HAL_UART_STATE_READY) ;

}

# else while ( controllers[ idx] . tx_sem_flag != SEM_NOTIFY_FLAG) {

}

# endif } else {

HAL_UART_Transmit ( & controllers[ idx] . handle, data, len, HAL_MAX_DELAY) ;

}

return len;

}

void USART1_IRQHandler ( void ) {

TX_INTERRUPT_SAVE_AREA

TX_DISABLE

HAL_UART_IRQHandler ( & controllers[ UART1_IDX] . handle) ;

TX_RESTORE

}

void USART2_IRQHandler ( void ) {

TX_INTERRUPT_SAVE_AREA

TX_DISABLE

HAL_UART_IRQHandler ( & controllers[ UART2_IDX] . handle) ;

TX_RESTORE

}

void USART3_IRQHandler ( void ) {

TX_INTERRUPT_SAVE_AREA

TX_DISABLE

HAL_UART_IRQHandler ( & controllers[ UART3_IDX] . handle) ;

TX_RESTORE

}

HAL_StatusTypeDef UART_Receive_IT ( UART_HandleTypeDef * huart) {

uint8_t pdata8bits;

uint16_t pdata16bits;

rt_size_t ( * write_call) ( struct rt_ringbuffer * rb, const rt_uint8_t * ptr, rt_uint32_t length) ;

write_call = rt_ringbuffer_put;

struct stm32_uart_controller * control = rt_container_of ( huart, struct stm32_uart_controller , handle) ;

if ( rt_ringbuffer_data_len ( control-> rx_buffer) == control-> rx_buffer-> buffer_size) {

write_call = rt_ringbuffer_put_force;

}

if ( ( huart-> Init. WordLength == UART_WORDLENGTH_9B) && ( huart-> Init. Parity == UART_PARITY_NONE) ) {

pdata16bits = ( uint16_t ) ( huart-> Instance-> DR & ( uint16_t ) 0x01FF ) ;

write_call ( control-> rx_buffer, ( const rt_uint8_t * ) & pdata16bits, 2 ) ;

} else {

if ( ( huart-> Init. WordLength == UART_WORDLENGTH_9B) ||

( ( huart-> Init. WordLength == UART_WORDLENGTH_8B) && ( huart-> Init. Parity == UART_PARITY_NONE) ) ) {

pdata8bits = ( uint8_t ) ( huart-> Instance-> DR & ( uint8_t ) 0x00FF ) ;

} else {

pdata8bits = ( uint8_t ) ( huart-> Instance-> DR & ( uint8_t ) 0x007F ) ;

}

write_call ( control-> rx_buffer, ( const rt_uint8_t * ) & pdata8bits, 1 ) ;

}

uint32_t data_len = rt_ringbuffer_data_len ( control-> rx_buffer) ;

if ( data_len == control-> rx_buffer-> buffer_size) {

# if UART_USE_OS_FLAG if ( control-> rx_sem) {

tx_semaphore_put ( control-> rx_sem) ;

}

# else -> rx_sem_flag = SEM_NOTIFY_FLAG;

# endif }

if ( data_len && control-> rx_indicate) {

control-> rx_indicate ( control, data_len) ;

}

return HAL_OK;

}

HAL_StatusTypeDef UART_Transmit_IT ( UART_HandleTypeDef * huart) {

struct stm32_uart_controller * control = rt_container_of ( huart, struct stm32_uart_controller , handle) ;

{

# if 0 static uint8_t tmp;

if ( rt_ringbuffer_getchar ( ( control-> tx_buffer) , ( rt_uint8_t * ) & tmp) ) {

huart-> Instance-> DR = tmp;

} else {

__HAL_UART_DISABLE_IT ( huart, UART_IT_TXE) ;

__HAL_UART_ENABLE_IT ( huart, UART_IT_TC) ;

}

# else static uint16_t tmp;

static uint8_t read_cnt;

if ( ( huart-> Init. WordLength == UART_WORDLENGTH_9B) && ( huart-> Init. Parity == UART_PARITY_NONE) ) {

read_cnt = 2 ;

} else {

read_cnt = 1 ;

}

if ( rt_ringbuffer_get ( control-> tx_buffer, ( rt_uint8_t * ) & tmp, read_cnt) == read_cnt) {

huart-> Instance-> DR = read_cnt == 2

? ( uint16_t ) ( tmp & ( uint16_t ) 0x01FF )

: ( uint8_t ) ( tmp & ( uint8_t ) 0x00FF ) ;

} else {

__HAL_UART_DISABLE_IT ( huart, UART_IT_TXE) ;

__HAL_UART_ENABLE_IT ( huart, UART_IT_TC) ;

}

# endif return HAL_OK;

}

}

void HAL_UART_TxCpltCallback ( UART_HandleTypeDef * huart) {

struct stm32_uart_controller * control = rt_container_of ( huart, struct stm32_uart_controller , handle) ;

if ( huart-> hdmatx == NULL ) {

# if UART_USE_OS_FLAG if ( control-> tx_sem) {

tx_semaphore_put ( control-> tx_sem) ;

}

# else -> tx_sem_flag = SEM_NOTIFY_FLAG;

# endif if ( control-> tx_complete) {

control-> tx_complete ( control) ;

}

} else {

}

}

void HAL_UART_TxHalfCpltCallback ( UART_HandleTypeDef * huart) {

UNUSED ( huart) ;

}

void HAL_UART_RxCpltCallback ( UART_HandleTypeDef * huart) {

if ( huart-> hdmarx != NULL ) {

}

}

void HAL_UART_RxHalfCpltCallback ( UART_HandleTypeDef * huart) {

UNUSED ( huart) ;

}

void HAL_UART_ErrorCallback ( UART_HandleTypeDef * huart) {

UNUSED ( huart) ;

struct stm32_uart_controller * control = rt_container_of ( huart, struct stm32_uart_controller , handle) ;

if ( huart-> hdmarx == NULL ) {

# if UART_USE_OS_FLAG if ( control-> rx_sem) {

tx_semaphore_put ( control-> rx_sem) ;

}

# else -> rx_sem_flag = SEM_NOTIFY_FLAG;

# endif if ( huart-> Init. Parity != UART_PARITY_NONE) {

__HAL_UART_ENABLE_IT ( huart, UART_IT_PE) ;

}

__HAL_UART_ENABLE_IT ( huart, UART_IT_ERR) ;

__HAL_UART_ENABLE_IT ( huart, UART_IT_RXNE) ;

}

if ( huart-> hdmatx == NULL ) {

# if UART_USE_OS_FLAG if ( control-> tx_sem) {

tx_semaphore_put ( control-> tx_sem) ;

}

# else -> tx_sem_flag = SEM_NOTIFY_FLAG;

# endif }

}

void HAL_UART_AbortCpltCallback ( UART_HandleTypeDef * huart) {

UNUSED ( huart) ;

}

void HAL_UART_AbortTransmitCpltCallback ( UART_HandleTypeDef * huart) {

UNUSED ( huart) ;

}

void HAL_UART_AbortReceiveCpltCallback ( UART_HandleTypeDef * huart) {

UNUSED ( huart) ;

}

void HAL_UARTEx_RxEventCallback ( UART_HandleTypeDef * huart, uint16_t Size) {

UNUSED ( huart) ;

UNUSED ( Size) ;

}

# include "drv_common.h" void HAL_UART_MspInit ( UART_HandleTypeDef * huart) {

GPIO_InitTypeDef GPIO_InitStruct = { 0 } ;

switch ( ( uint32_t ) huart-> Instance) {

case ( uint32_t ) USART1:

__HAL_RCC_USART1_CLK_ENABLE ( ) ;

__HAL_RCC_GPIOA_CLK_ENABLE ( ) ;

GPIO_InitStruct. Pin = GPIO_PIN_9 | GPIO_PIN_10;

GPIO_InitStruct. Mode = GPIO_MODE_AF_PP;

GPIO_InitStruct. Pull = GPIO_NOPULL;

GPIO_InitStruct. Speed = GPIO_SPEED_FREQ_HIGH;

GPIO_InitStruct. Alternate = GPIO_AF7_USART1;

HAL_GPIO_Init ( GPIOA, & GPIO_InitStruct) ;

break ;

case ( uint32_t ) USART2:

__HAL_RCC_USART2_CLK_ENABLE ( ) ;

__HAL_RCC_USART2_CLK_ENABLE ( ) ;

__HAL_RCC_GPIOA_CLK_ENABLE ( ) ;

GPIO_InitStruct. Pin = GPIO_PIN_2 | GPIO_PIN_3;

GPIO_InitStruct. Mode = GPIO_MODE_AF_PP;

GPIO_InitStruct. Pull = GPIO_NOPULL;

GPIO_InitStruct. Speed = GPIO_SPEED_FREQ_VERY_HIGH;

GPIO_InitStruct. Alternate = GPIO_AF7_USART2;

HAL_GPIO_Init ( GPIOA, & GPIO_InitStruct) ;

break ;

default :

break ;

}

}

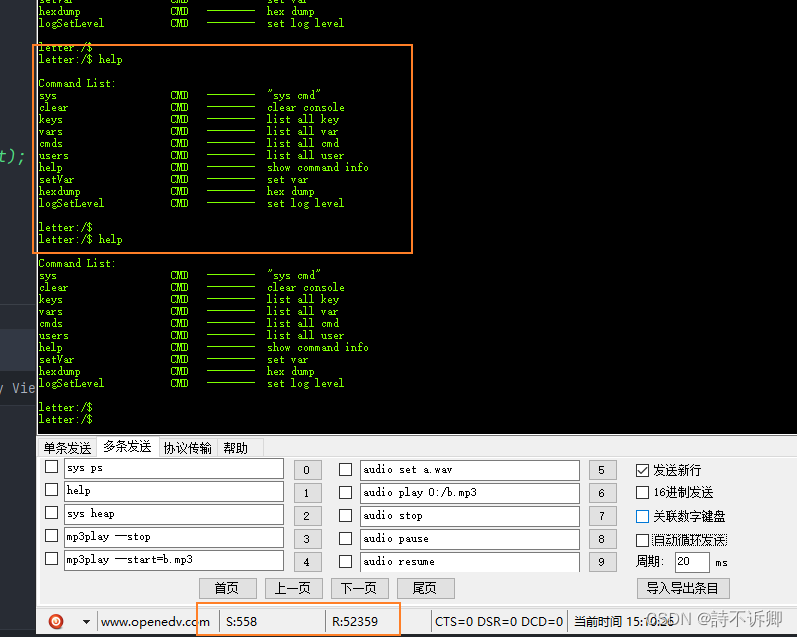

bsp_UartParDefaultSet ( USART1) ;

bsp_UartParSemSet ( USART1, 0 , 1 ) ;

bsp_InitUart ( USART1, 2048 , 2048 ) ;

如果是裸机的话,只需要改动hal库源码,把对应的函数改成弱引用,由外部重写。并使用静态分配的方式和内部变量的标志位。 驱动依赖了一个缓冲数据结构体,将hal库内部的数据指针的部分替换为使用循环缓冲区进行存取,驱动只涉及到中断的方式,dma的方式,可通过对应的回调函数中进行添加(dma和中断共用一套回调函数,通过判断串口内部dma指针的引用是否为NULL进行推断使用的是中断还是dma方式即可)