一、时钟

DC工具在进行综合时,需要根据一个时钟进行时序分析。

因此我们需要通过SDC给DC提供一个时钟。

时钟创建是必须的,在创建时钟的同时对时钟进行约束,从而确定整个设计的性能和限制外部时钟。

二、时钟创建

时钟约束通过creat_clock进行,其语法为:

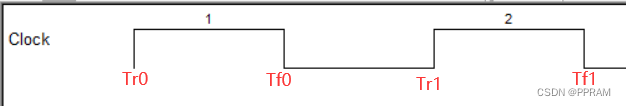

creat_clock [-name clock_name] [-period period_value] [-waveform {Tr0 Tf0 Tr1 Tf1....}] [clock_object]

参数说明:

-name:创建的时钟名。

-period:创建的时钟周期。

-waveform:由上升沿到达时间和下降沿到达时间组成的列表,描述波形。

clock_object:时钟对象。

需要注意的是,-period指定的时钟周期单位通常为ns,这是由工艺库的决定的。-waveform是针对设置的时钟周期而言的,描述了一个周期内时钟的变化。描述是通过列表进行的,如{Tr0 Tf0 Tr1 Tf1}表示在Tr0时钟上升沿,Trf0下降,Tr1上升,Tf1下降。

如:设置串口的参考时钟频率为10Mhz,占空比50%。

如:设置串口的参考时钟频率为10Mhz,占空比50%。

creat_clock -name ref_clk -period 100 -waveform {0 50}] [get_ports ref_clk]