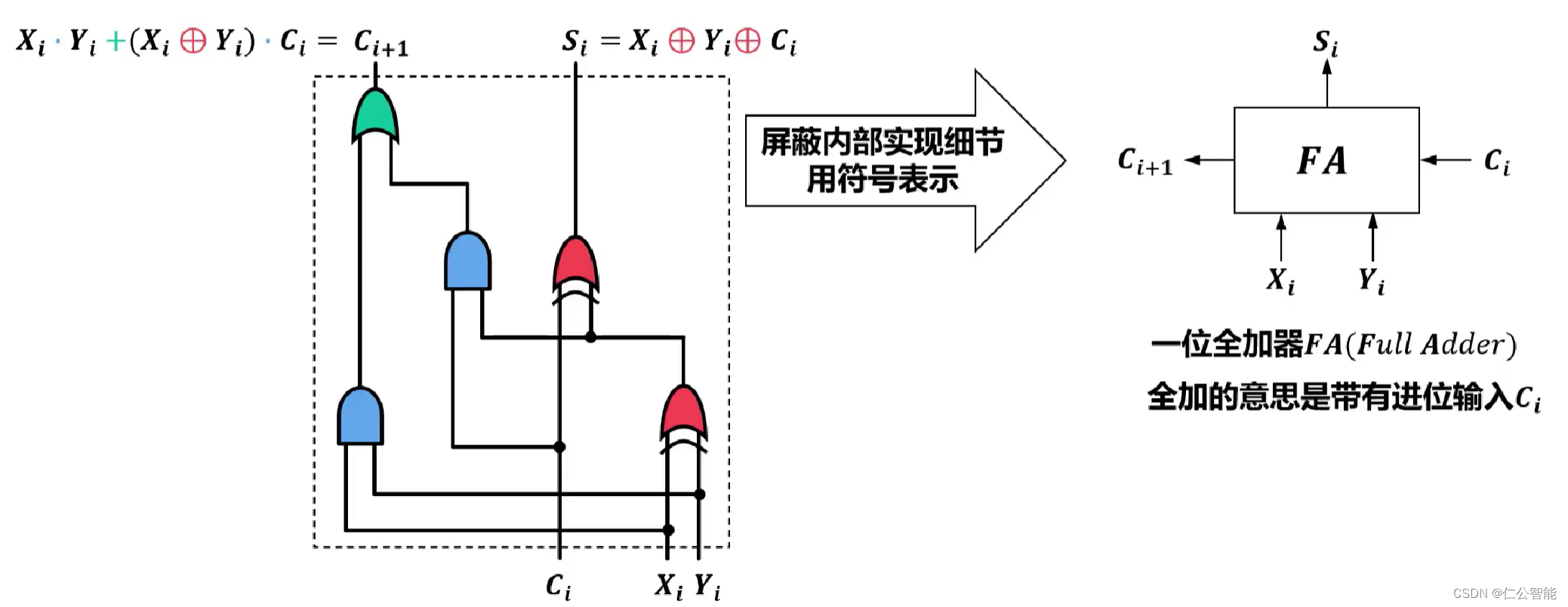

一、一位全加器的设计

视频学习链接:3-2-4 定点数的加法和减法运算 — 一位全加器的硬件逻辑实现_哔哩哔哩_bilibili

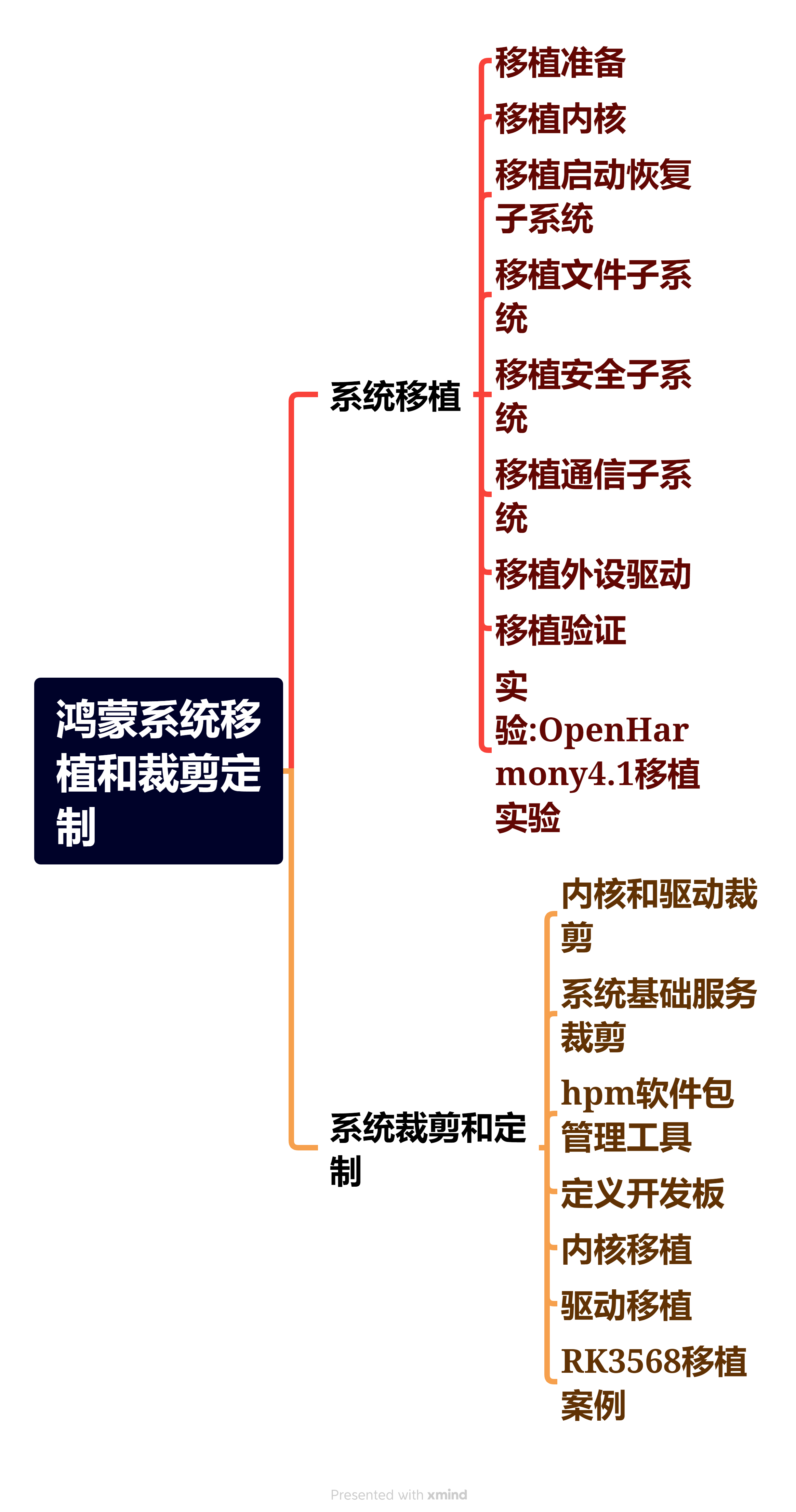

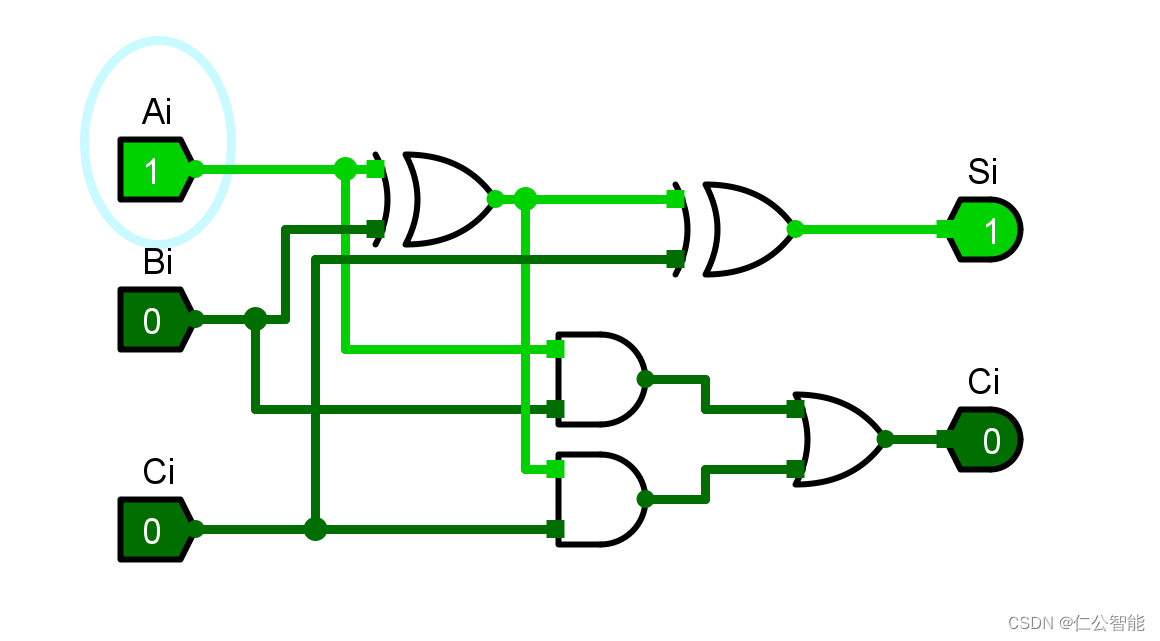

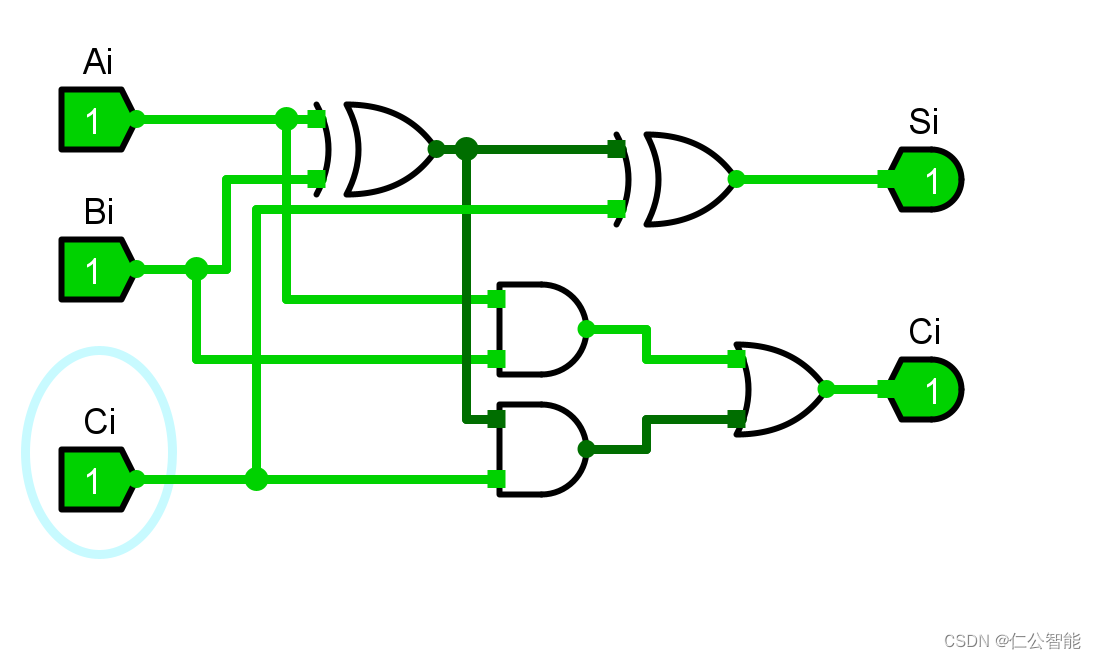

仿真电路图:

总结:奇数个1时Si输出为1,偶数个1输出为0;1的个数大于等于2时,Ci输出1

实现封装:

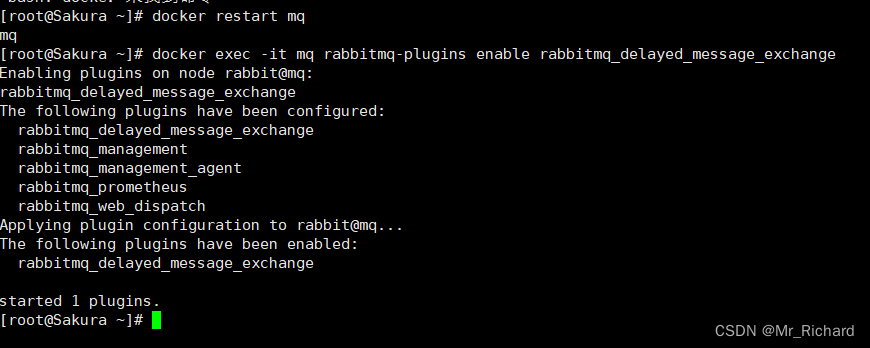

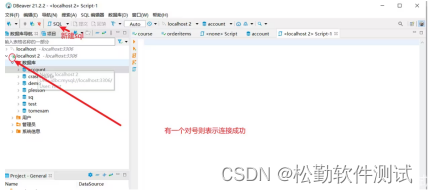

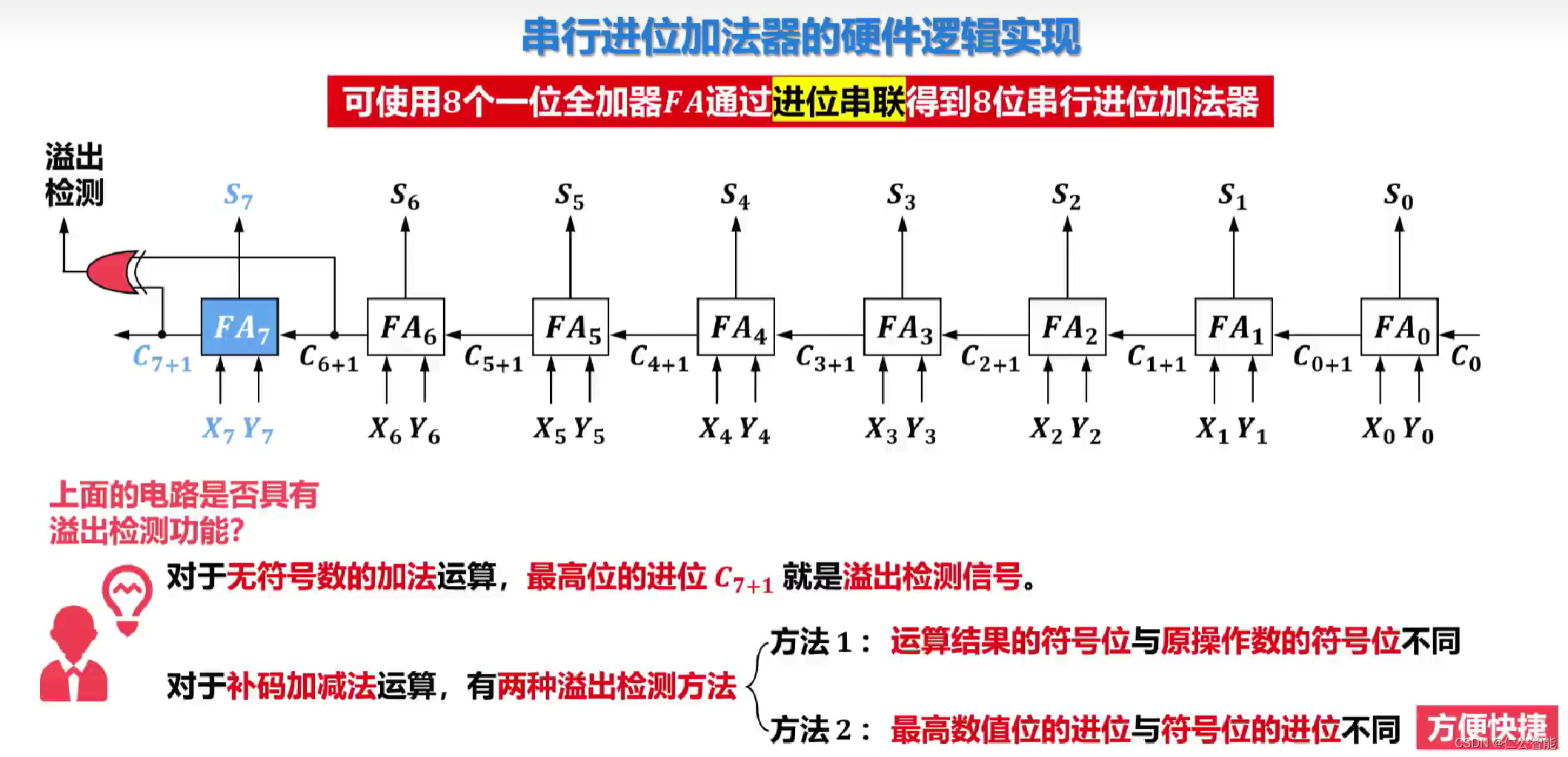

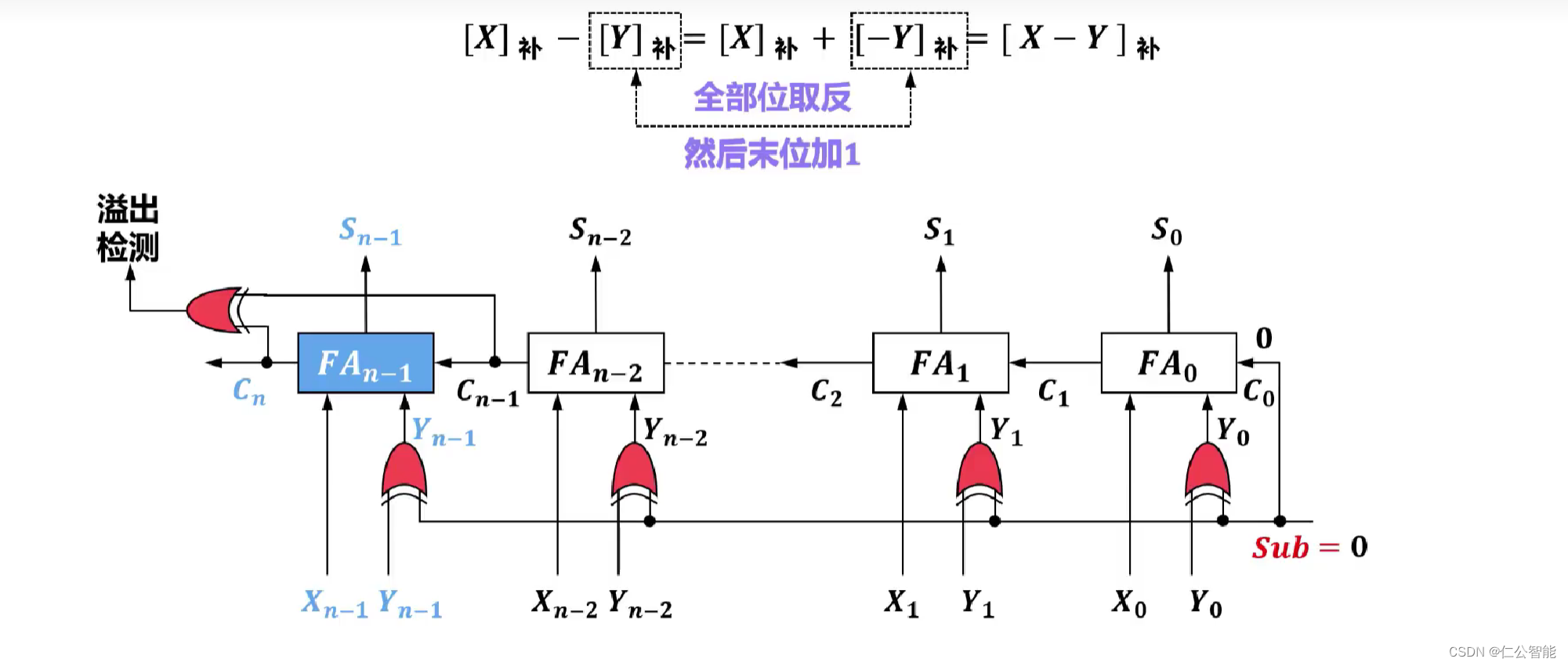

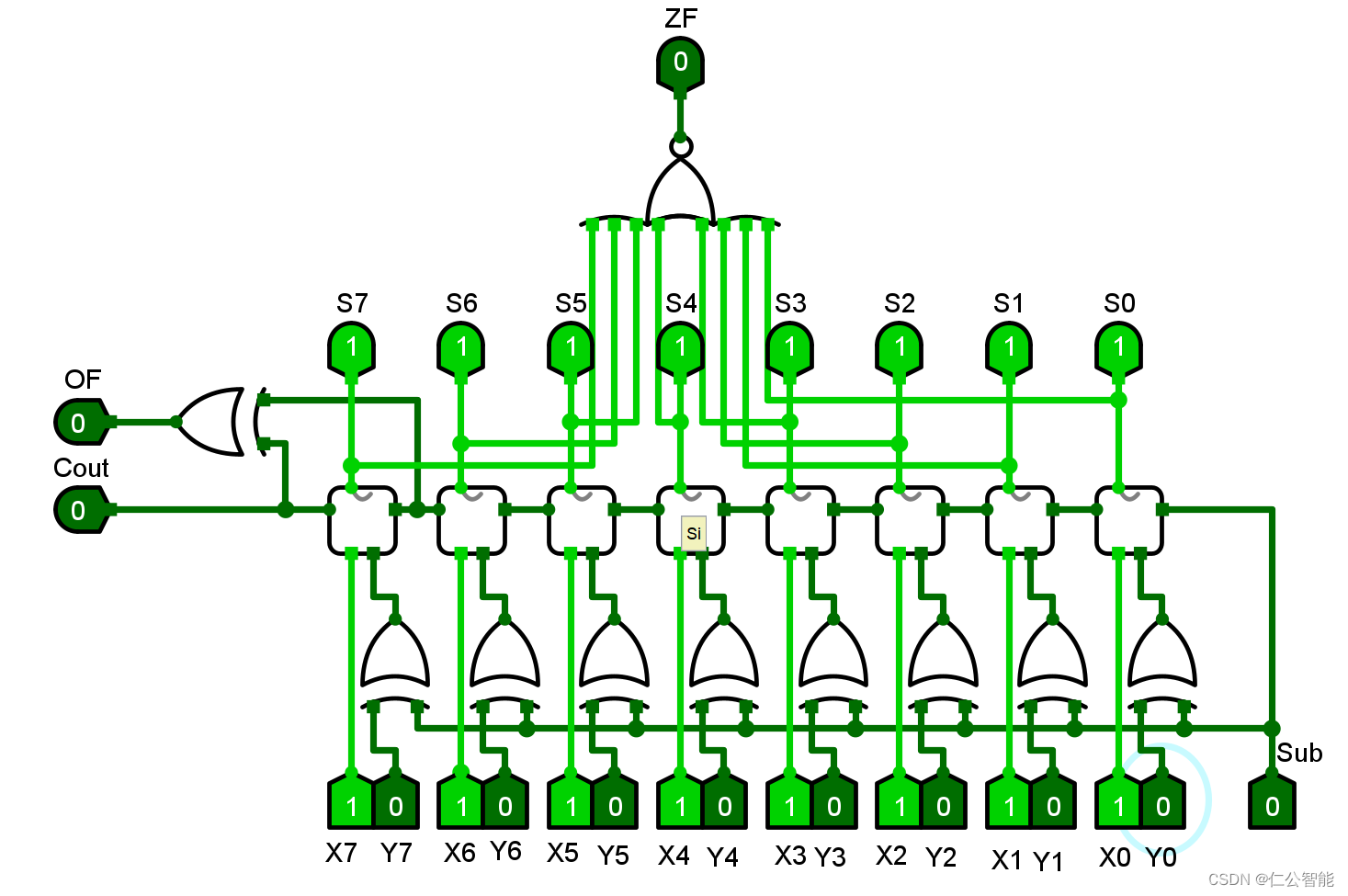

二、多位串行可控的加减法电路设计

视频学习链接:3-2-5 定点数的加法和减法运算 — 串行进位加法器的硬件逻辑实现_哔哩哔哩_bilibili

加上零标志,当结果为全零时,ZF输出为1。

七、思考题

1.假设门电路的延迟时间为 T,1 位全加器的延迟时间是多少,4 位串行全加器的延

迟时间是多少?为什么?

答:

2.为什么计算机中采用补码表示带符号的整数?8 位补码定点整数,数据范围是多

少?

答:因为补码的符号位和数值位一起参与运算,可以简化加减法运算,同时避免了正负数的处理问题,使得计算机在进行整数运算时更加高效和方便。对于8位补码定点整数,数据范围是-128到127。其中,最高位为符号位,0表示正数,1表示负数。

3.有符号加法和减法的溢出检测逻辑有何区别?

答: