Chisel Explanation width !x逻辑非 1 x && y 逻辑与 1 x||y 逻辑或 1

Chisel Explanation width in Verilog ~x 位反 w(x) ~ signal_x x & y 位与 max(w(x), w(y)) signal_x & signal_y x | y 位或 max(w(x), w(y)) signal_x | signal_y x ^ y 按位异或 max(w(x), w(y)) signal_x ^ signal_y x(n) bit 索引, 0 is LSB 1 signal[n] x(n, m) 字段提取 n - m + 1 signal [n:m] x << n 左移 w(x) + n << x >> n 右移 w(x) - n >> (补零) Fill(n, x) 重复拼接 n * w(x) {n{signal_x}} Cat(x, y) 拼接 w(x) + w(y) {signal_x,signal_y} Mux(c, x, y) 三元操作 max(w(x), w(y)) signal_c ? signal_x : signal_y v.andR 位与 1 (Bool) & signal_v v.orR 位或 1 (Bool) | signal_v v.xorR 位异或 1(Bool) ^ signal_v

Chisel Explanation width in Verilog x === y 相等(triple equals) 1 signal_x == signal_y x != y 不等 1 signal_x != signal_y x =/= y 不等 1 signal_x != signal_y x > y 大于 1 signal_x > signal_y x >= y 大于等于 1 signal_x >= signal_y x < y 小于 1 signal_x < signal_y x <= y 小于等于 1 signal_x <= signal_y

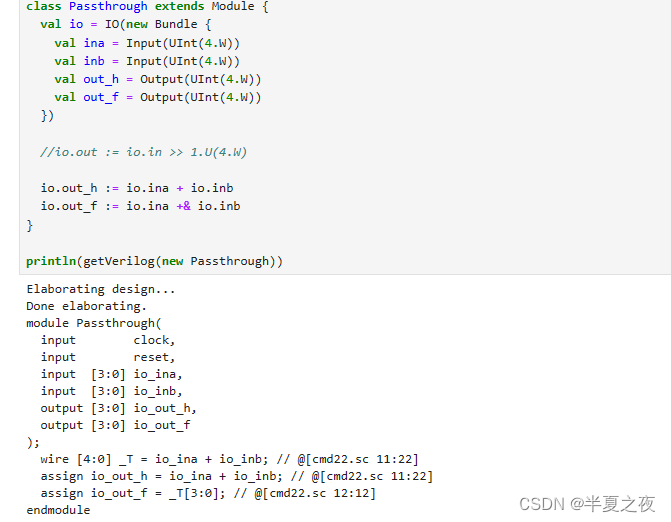

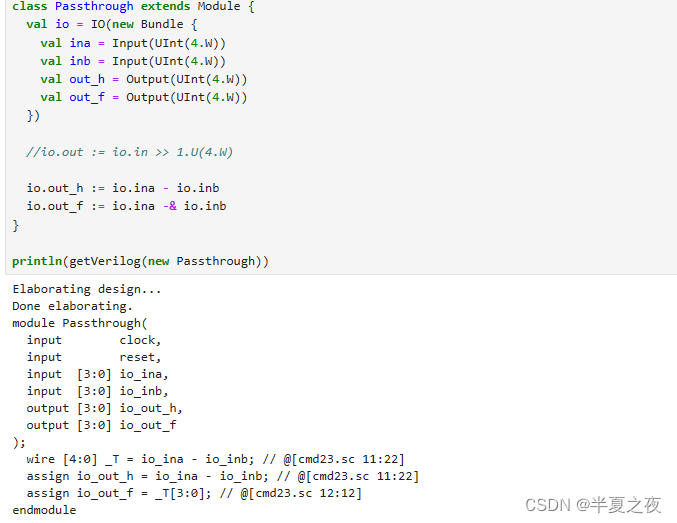

Chisel Explanation width in Verilog x + y 加 max(w(x),w(y)) signal_x + signal_y x +% y 加 max(w(x),w(y)) signal_x + signal_y x +& y 位扩加 max(w(x),w(y))+1 NULL x - y 减 max(w(x),w(y)) signal_x - signal_y x -% y 减 max(w(x),w(y)) signal_x - signal_y x -& y 位扩减 max(w(x),w(y))+1 NULL x * y 乘 w(x)+w(y) signal_x * signal_y x / y 除 w(x) signal_x */ signal_y x % y 取余 bits(maxVal(y)-1) signal_x % signal_y

在chisel 中,以下运算符与Verilog/ SystemVerilog有所不同:

位拼接 位索引 简化与 : v.andR简化或 : v.orR简化异或 : v.xorR相等 不等 扩展加 : +&扩展减 : -&