此篇记录FPGA的静态时序分析,在学习FPGA的过程中,越发觉得对于时序约束只是懂了个皮毛。现在记录一下自己的学习过程。

本文摘自《VIVADO从此开始》高亚军

为什么要进行约束?约束的目的是什么?

简单来说,就是需要在FPGA芯片中的电路,从输入到输出的时间,要系统的时钟周期内完成。

约束的管理

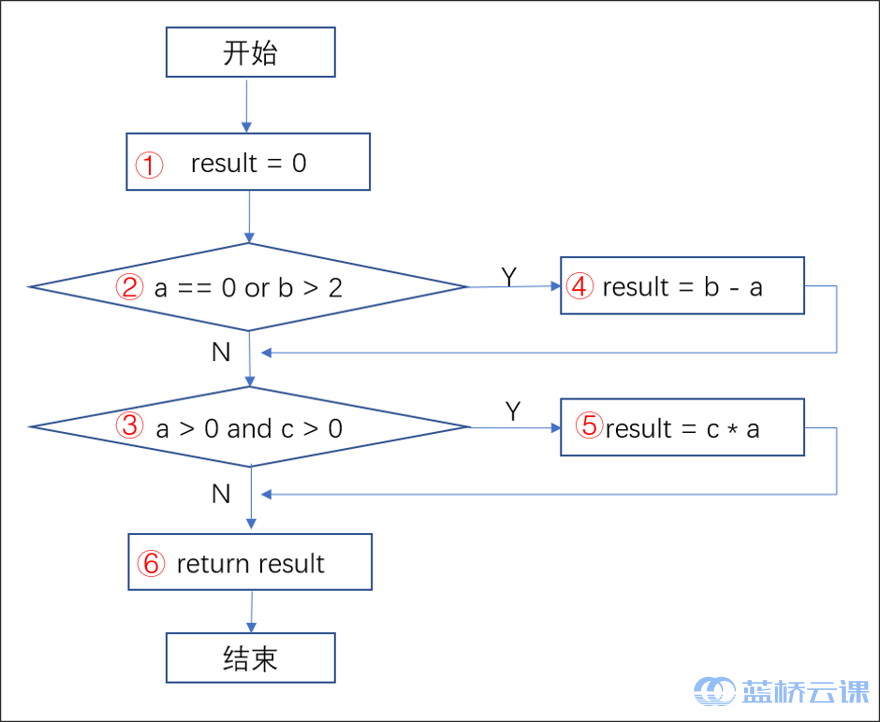

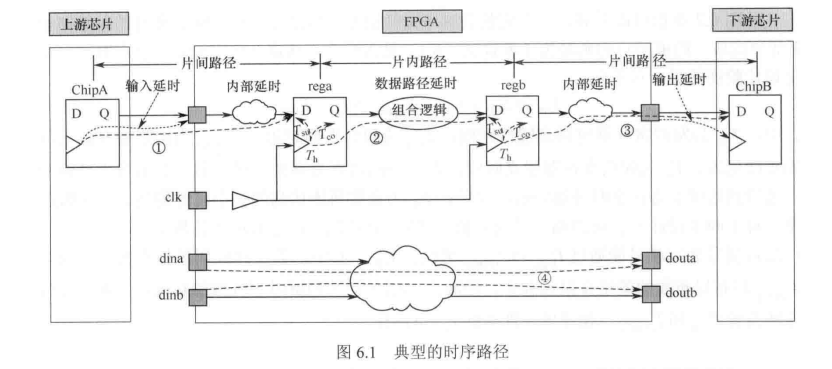

典型的时序路径有4类。

分为

片外路径

片内路径

| 时序路径 | 起点 | 终点 | 应用约束 |

| 1、输入端口到FPGA内部第一级触发器的路径 | ChipA/clk | Rega/D | Set_input_delay |

| 2、FPGA内部触发器之间的路径 | Rega/clk | Regb/D | Create_clock |

| 3、FPGA内部末级触发器到输出端口的路径 | Regb/clk | ChipB/D | Set_output_delay |

| 4、FPGA输入端口到输出端口的路径 | 输入端口 | 输出端口 | Set_max_delay |

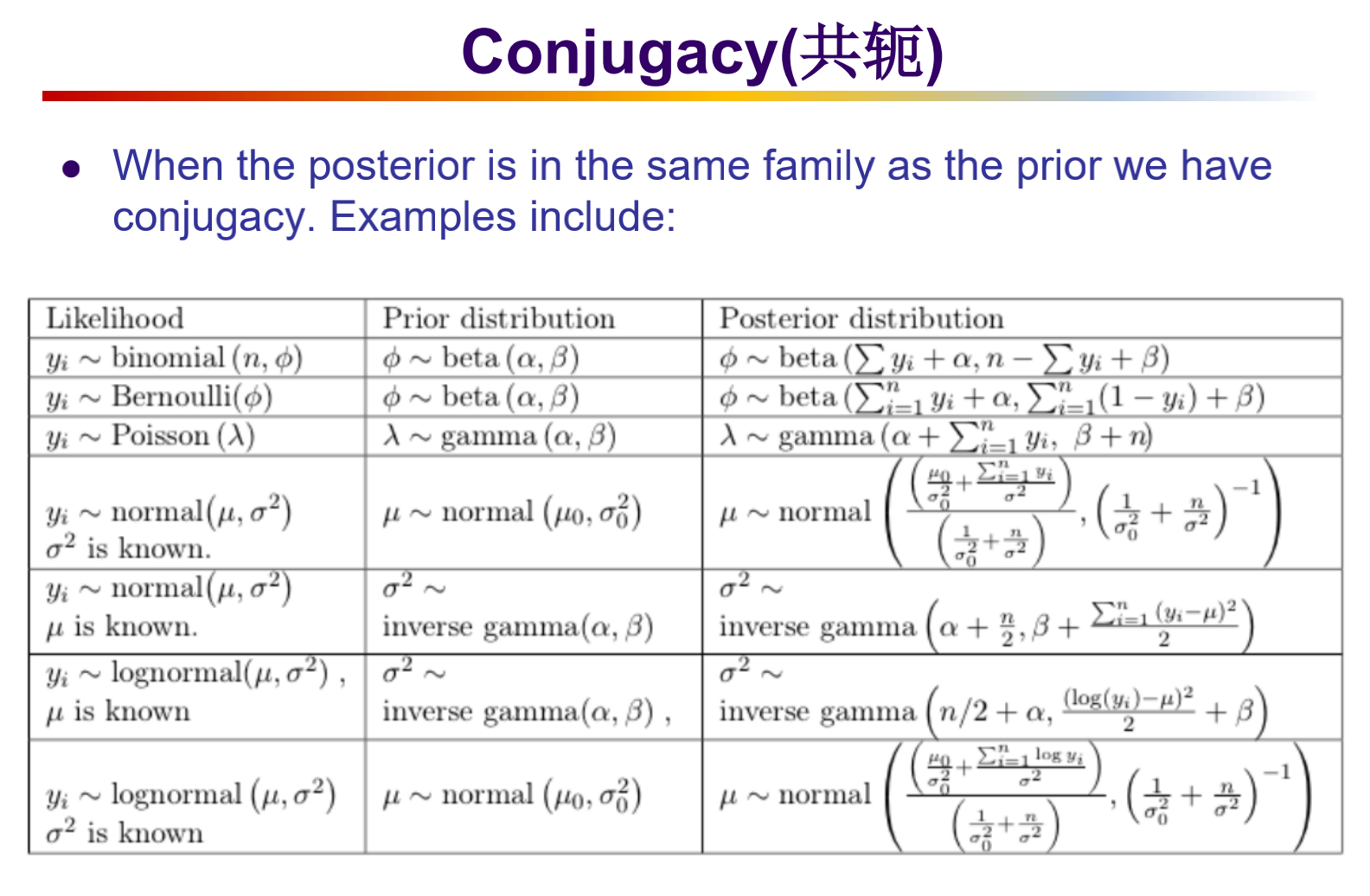

这四类路径中,最为核心的标记是2同步时序路径。

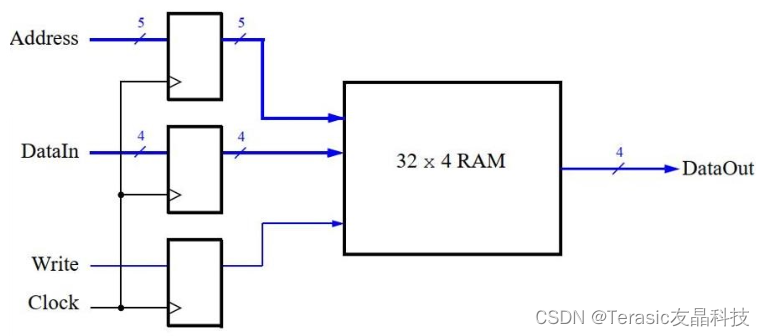

这类路径起点模块和终点模块均为同一时钟驱动的时序逻辑(通常为寄存器,寄存器可以是SLICE中的,也可以是BRAM或者DSP48内部)。如果把PCB看成一个大的系统,标记1,2,3所示的路径可以归纳为一个统一模型。触发器+组合逻辑+触发器。

从图中可以看出,一个完整的时序路径由源时钟路径,数据路径和目的时钟路径三部分构成。约束的目的是验证

公式是否成立。

| Tco | 发端寄存器时钟到输出时间 |

| Tlogic | 组合逻辑延迟 |

| Trouting | 为两级寄存器之间布线延迟 |

| Tsu | 为收端寄存器建立时间 |

| Tskew | 为两级寄存器时钟歪斜,值等于时钟同一边沿到达两个寄存器时钟端口的时间差 |

| Tclk | 系统所能达到的最小时钟周期 |

在FPGA中,对于同步设计Tskew可以忽略。Tco和Tsu取决于芯片工艺。因此一旦选定芯片型号就只能通过Tlogic和Trouting来改善Tclk。其中Tlogic和代码风格有很大关系。Trouting和布局布线策略有关系。

即我们通过约束改善时序收敛的目的。就是通过改善Tlogic和Trouting来让系统在期望的Tclk下运行。

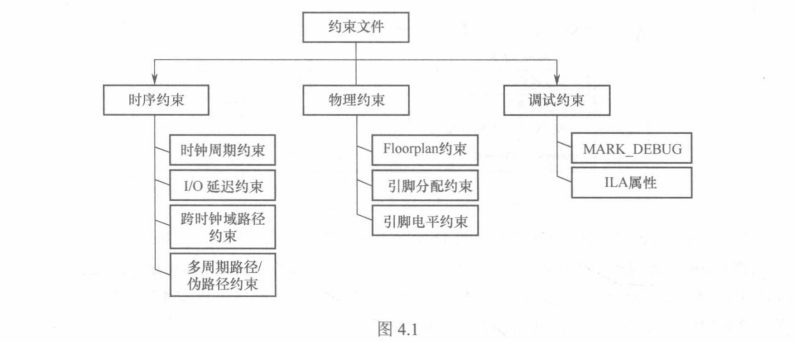

对于一个完整的FPGA设计。既要有时序约束,也要有物理约束(引脚位置,电平,驱动能力等等)。在工程进行的过程中,需要对FPGA功能进行调试,因此在调试阶段会使用到调试约束。所以一个完整的工程往往会包含时序约束,物理约束,调试约束。

该书还介绍了设置约束生效的阶段,是在综合阶段和实现阶段有效。还是均有效。以及查看位置约束是否生效的方式。

下面我将一一学习上述约束。

![[MySQL]数据库原理8——喵喵期末不挂科](https://img-blog.csdnimg.cn/direct/03e367a251574527ba182ce281cd459b.png)