1. 引言

随着市场对更高图像质量的需求不断增加,成像技术持续发展,各种新兴技术(例如3D、计算、运动和红外线)的不断涌现。如今的成像应用对高质量、易用性、能耗效率、高集成度、快速上市和成本效益提出了全面要求。为了满足这些要求,STM32 MCU 内置的数字照相机接口(DCMI),能够高效连接并行照相机模块。

对于使用 STM32 DCMI 开发相机应用的客户,经常有以下问题:STM32 DCMI 最大支持的像素时钟是多少?STM32F4/F7/H7/U5 能支持 1280×720 的相机分辨率吗?最大的帧率是多少?如何判断所设计的应用产生的带宽是否能充足?相机输出是选择 8 位、10位、12 位、还是 14 位?

针对这些问题,本文档从 DCMI 使用的几个方面,介绍了 STM32 DCMI 在连续抓取模式下带宽的估算,以及提升性能需要注意的事项。客户在设计相机应用时可以参考。

2. STM32 DCMI

STM32 数字照相机接口(DCMI)采用同步并行数据总线。它可以轻松集成并适应相机的特殊应用要求。DCMI 可连接 8、10、12 和 14 位 CMOS 照相机模块,并支持多种数据格式:8/10/12/14 位逐行视频、YCbCr4:2:2 逐行视频、RGB565 逐行视频、JPEG 等。

像素最大支持 16 位色深。

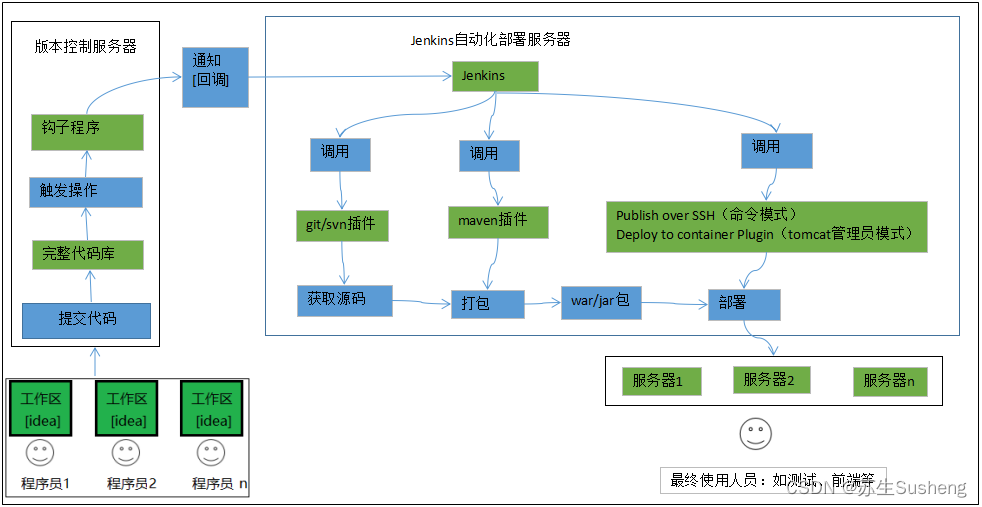

2.1. STM32 智能架构中的 DCMI

DCMI 应用需要用帧缓冲区来存储采集的图像。必须根据图像大小和传输速度使用合适的目标存储区。在某些应用中,必须连接外部存储器(SDRAM),以便提供较大的数据存储空间。对于支持 DMA2D(Chrom-ART Accelerator™控制器)的 STM32 系列,也可以用它做色彩空间转换(例如 RGB565 至 ARGB8888),或使用 DMA 从一个存储区到另一个存储区的数据转移。

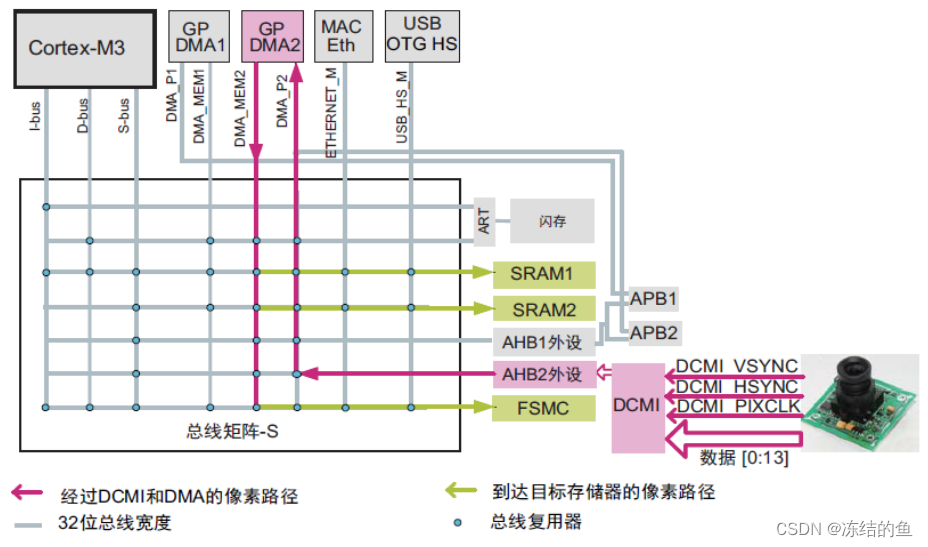

下面图 1 是 STM32F2x7 系列智能架构中 DCMI 的例子。这里 DCMI 通过 AHB2 外设总线连接到 AHB 总线矩阵。DMA2 主控访问 DCMI,将 DCMI 接收到的图像数据传输到内部 RAM 或外部 SDRAM 中,具体目标位置取决于应用。

图1.STM32F2x7 系列智能架构中的 DCMI 从设备 AHB2 外设

2.2. DCMI 最大像素时钟频率

STM32 DCMI 支持的像素时钟频率,与 AHB 时钟频率比值必须小于 0.4。具体的像素时钟频率最大值要查询所用 STM32 的数据手册。下面表 1 中列出了部分 STM32 系列DCMI 最大像素时钟频率及相关可用资源的信息。如需更详细信息,请参考相应的参考手册/数据手册。

表1. DCMI 及相关可用资源

2.3. DCMI 支持的图像分辨率

STM32 DCMI 仅对输入像素时钟频率有硬件限制(DCMI_PCLK / fHCLK 最大 0.4),对图像的分辨率没有限制。DCMI 连续抓取模式下,图像分辨率会影响帧率(帧率的大小会影响视频的流畅度)。在固定的像素时钟频率下,高分辨率图像的带宽需求较高,对应的帧率则会下降。或者说,在相同的图像分辨率下,提高帧率需要相应地提高像素时钟频率。

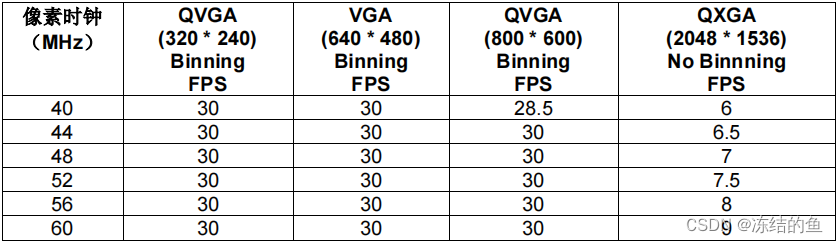

例如下表 2(摘自三星 S5K5CAGA CMOS Image Sensor 的数据手册)所示,大家可以从中了解 S5K5CAGA 的像素频率、图像分辨率、帧率的关系(非 RGB888,16 位色深)。另外,图像分辨率主要通过设置相机的输出格式进行修改。

表2. S5K5CAGA YUV/RGB565 像素时钟频率与帧率

对于中高分辨率的图像,一般采用双缓冲区或多缓冲区模式。这个主要原因是因为DCMI 使用的 DMA 计数寄存器 SxNDTR 使用了 16 位用于计数。最大 0xFFFF,即65535 ,单位为 32 位 Word,当图像分辨率超过 65535 Words(262140 字节)时,则要使用双缓冲区或多缓冲区模式。双缓冲区地址由 DMA_SxM0AR/DMA_SxM1AR 设定。多缓冲区时,则需要动态交替 DMA_SxM0AR/DMA_SxM1AR,使之指向图像缓冲区的不同存储位置,相当于分块存储。

2.4. DCMI 带宽与性能

使用 DCMI 的相机应用,使用连续抓取模式,功能往往是由相机连续输出所摄图像数据流到 STM32,STM32 DCMI 捕获视频流后,再输出到屏幕显示(如监控)或做图像数据处理、传输等。如果相机输出的是高像素高色深高帧率的视频流,DCMI 在接收过程中,如不能及时处理,DCMI FIFO 即会产生溢出错误(Overrun),进而导致图像数据丢失,帧率下降等问题。

2.4.1. DCMI 带宽与性能

DCMI 带宽计算公式为:带宽 = 分辨率 * 色深 * 帧率。

以三星 S5K5CAGA 为例,如表 2 中第 1 行数据(这里相机采用 RGB565,16 位/像素,8 位输出格式),则 QXGA 输出的带宽需求 =(2048 * 1536)* 2 * 6 ≈ 38MBps。像素时钟为 40MHz,8 位输出,每 2 个 CLK 传输 1 个像素数据,对应的最大输出能力为 40MBps。则 QXGA 在 40MHz 的像素时钟频率下是可以以 6 帧/秒的帧率输入到 DCMI 的。

DCMI 捕获图像数据流,再由 DMA 传输到图像缓冲区,该例中,图像缓冲区(帧缓冲区)的大小为:2048 * 1546 * 2 ≈ 6.3 MByte。

高像素高色深的图像,对应的图像缓冲区较大。当 MCU 内置的 SRAM 不能满足DCMI 图像缓冲区需求时,则需要用外部 SDRAM 来存储。例如 STM32F469 MCU(见表1,第 6 行数据),其 FSMC 支持的最大频率为 90MHz,宽度 32 位,则 SDRAM 的带宽= 90 * 4 = 360 MBps,能够满足 DCMI 带宽的需求。

一般,DCMI 图像缓冲区中的数据是需要再次传输或由 CPU 进行计算处理的,理论上 DCMI 输入的带宽需求最大不应超过SDRAM 的带宽的 50%。这里需要注意 SDRAM 可能存在多个主控(如 CPU、DMA、LTDC 等)的访问,如遇到 SDRAM 性能瓶颈问题,可考虑下列方面进行优化:

- (1)将各主控设备访问的存储器尽量分开,以减少竞争访问;

- (2)将 CPU 访问的 SDRAM Bank 与 DCMI 图像缓冲区的 Bank 分开;

- (3)将 DCMI 图像缓冲区区域设为不可缓冲,CPU 访问的区域则可以设为可缓冲。

对于性能,另外一个重要因素是总线竞争问题。DCMI DMA 申请的 AHB 总线访问(即使在使用 FIFO 的情况下)并非长 Burst 的访问。如果 AHB 总线上存在其它长 Burst 访问(最大 1KByte),会造成 DMA 延迟访问 DCMI,令其不能及时将 DCMI FIFO 中的数据传输出去。可以认定:DCMI 需要传输数据时的总线繁忙是造成 其 FIFO 溢出错误的根源。

解决办法除了直接为设备分配不同 SDRAM 之外(将长 Burst 访问放在其他SDRAM),还可以考虑在内部 SRAM 增设 DCMI LineBuffer,化零为整,巧妙避开 AHB 长 Burst 访问造成的 DCMI 延迟问题。数据流如下:

- (1)DCMI(经 DMA)=> 内部 SRAM(LineBuffer) ;

- (2)内部 SRAM(LineBuffer)=> 外部 SDRAM(图像 Buffer)。

由 LineBuffer 到 SDRAM 的数据中转传输请求,可使用 DCMI IT_LINE 中断(行结束)触发。这里 MCU 如果是 STM32F7/H7 系列,还可使用 MDMA 充分发挥 AXI 总线的优势,但要注意 LineBuffer 最好是 8 字节的倍数(64 位总线)。

2.4.2. DCMI 图像大小调整功能

当考虑了上面的措施,仍无法满足应用对高分辨率需求时,用户可以通过设置相机,修改相机输出分辨率,配合 DCMI 调整图像大小功能,找到合适的折中方案。DCMI 提供的相关功能如下:

(1)窗口裁剪:

- 使用寄存器 DCMI_CWSTRT 指定起始坐标;

- 使用寄存器 DCMI_CWSIZE 指定窗口大小。

(2)图像数据调整(详见寄存器 DCMI_CS 中 LSM/BSM 等位域):

- 行选择:可选择 2 选 1,行数减半;

- 数据选择:字节流上可进行 2 选 1、4 选 1 已经 4 选 2 (注意:对于 RGB565格式, 只能 4 选 2 可选,2 选 1 及 4 选 1 会造成色彩数据错乱)。

2.5. DCMI 10/12/14 数据线输入

DCMI 支持最多 14 条数据线(D13 - D0),如果将 DCMI 配置为接收 10、12 或 14 位数据,DCMI 将用 2 个像素时钟周期捕获一个 32 位数据。以 12 位数据宽度为例,DCMI在第 1 个像素时钟捕获 12 位 LSB(忽略 D[13 :12]),存于 DCMI_DR 寄存器低 16 位字中低 12 位,高 4 位(D[15 :12)清零;第 2 像素时钟捕获的 12 位 LSB 则存于 DCMI_DR高 16 位字的低 12 位,高 4 位(DCMI_DR 的[31 : 28])清零。另外相机也必须配置为10/12/14 位输出。具体情况则由应用决定。

3. 小结

本文通过介绍 STM32 DCMI 支持的最大像素时钟频率,支持的图像分辨率及与帧率的关系,进而引出 DCMI 带宽与性能提升的注意事项。另外附带了 DCMI 图像大小的调整及10~14 数据线的简介,为用户遇到相关问题时提供思路参考。

参考文献

本文档参考ST官方的《【应用笔记】LAT1184+STM32+DCMI的带宽与性能介绍》文档。

参考下载地址:https://download.csdn.net/download/u014319604/88971338