存储器的介绍:

一、易失性存储器RAM:存储速度快,掉电丢失

- SRAM(静态RAM):极快

- DRAM(动态RAM):需要配一个扫描电路,进行“补电”(动态刷新)

二、非易失性存储器ROM:掉电不丢失,存储较慢

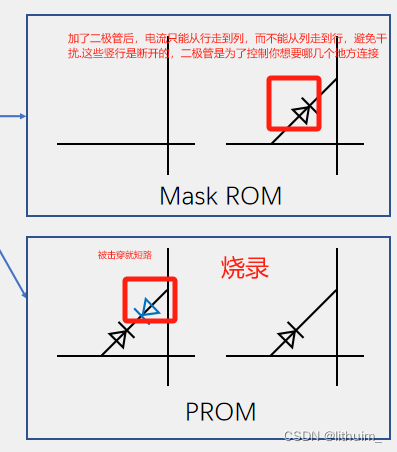

- Mask ROM(掩膜ROM):只能读不能写

- PROM(可编程ROM):只能写一次

- EPROM(可擦除可编程ROM):要用紫外线照射30分钟才能擦除

- E2PROM(电可擦除可编程ROM):用程序即可擦除

- Flash(闪存)

- 硬盘,软盘,光盘等

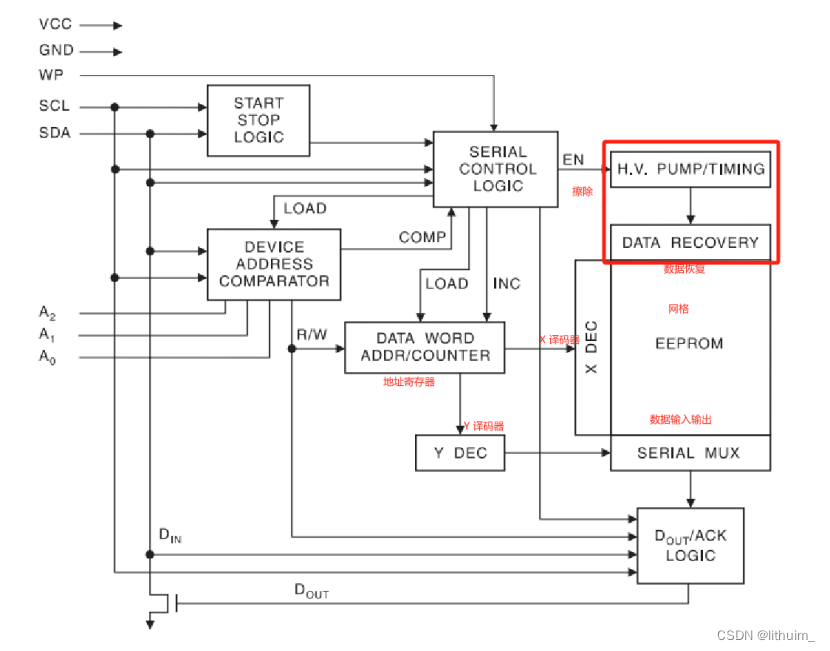

I²C总线介绍:

两根通信线:SCL,SDA(半双工就是一条线可以双向传输数据但是一个时间只能一个方向传)

好处:可以使各种设备通信标准统一

I²C电路规范:

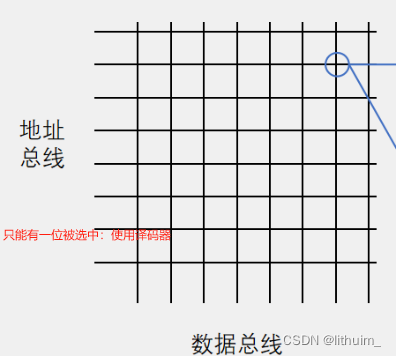

所有SCL连一起,SDA连一起

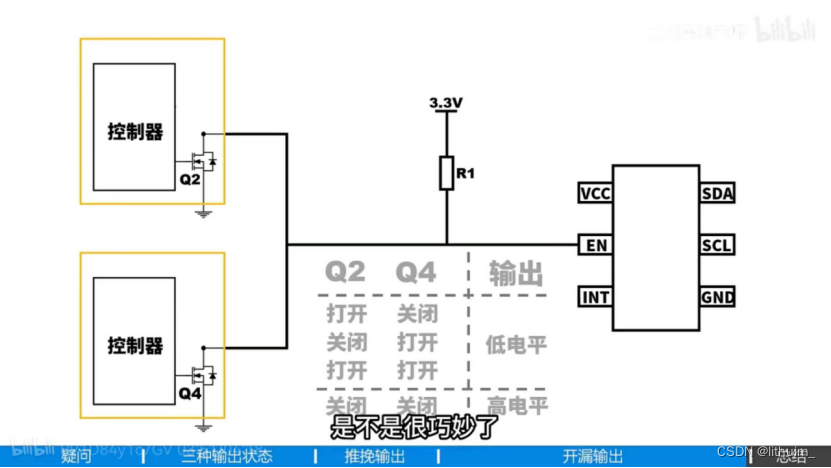

SCL和SDA均要配置成开漏输出模式。在下面每个设备引出的两条线都设一个开关,开漏输出模式输出1意思就是开关全部断开,也就是电阻无限大,又称高阻态,毫无驱动能力。

由于总线是弱上拉,设备写0的时候线会自动被拉为1;当设备写1时,设备与总线断开,但由于总线配置弱上拉,所以总线自动置1;然后不用的设备两条线全部置1 要用的设备就不断写零写一。如果cpu控制的base基级是0,那么out口会被拉低,电压因而为零,即使外界有接的vcc,vcc的电流也会被导通到ground,out端口输出仍然是0。SDA,SCL是半双工,1想象成下面开关断了,SDA,SCL靠VDD拉。当SDA,SCL为0的时候,想象成下面开关连接了,选择被控IC。

上拉电阻:【上拉电阻的通俗解释,你真正知道吗?-哔哩哔哩】【上拉电阻的通俗解释,你真正知道吗?-哔哩哔哩】![]() https://b23.tv/fEzm3J2

https://b23.tv/fEzm3J2

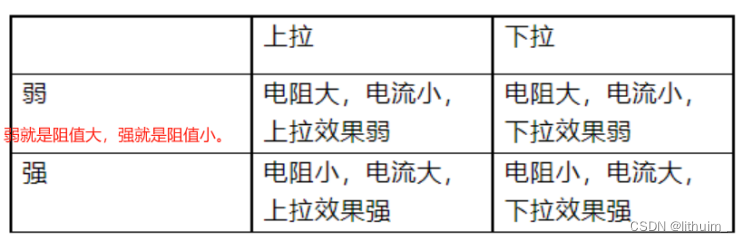

弱上拉:高电平驱动能力弱,低电平驱动能力强。上拉电阻增强了驱动能力。

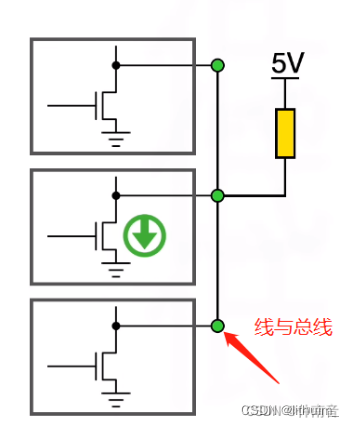

开漏输出,推挽输出:开漏的线与特性:当多个开漏输出链接到一起,当它们全部都输出高电平时,总线上才是高电平,但凡有一个开漏输出引脚上是低电平,总线就会被拉低。

【推挽 开漏 高阻 这都是谁想出来的词??-哔哩哔哩】![]() https://b23.tv/VDIqAgm

https://b23.tv/VDIqAgm

http://t.csdnimg.cn/HVG43![]() http://t.csdnimg.cn/HVG43

http://t.csdnimg.cn/HVG43

当有空闲设备部通信时,可能会影响到正在通信的设备,所以需要加上拉电阻,使其空闲设备处于一个高阻态(不是高电频也不是低电平)的情况下,这样空闲设备就会断路

I²C时序结构:

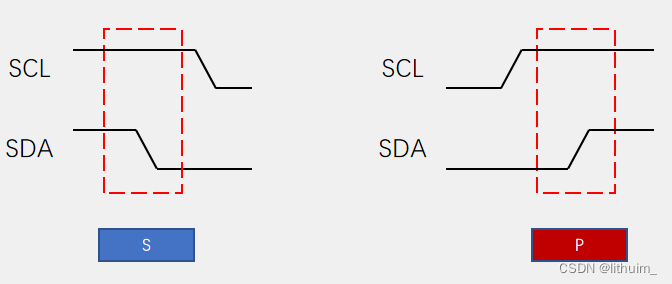

起始条件:SCL高电平期间,SDA从高电平变成低电平

终止条件:SCL高电平期间,SDA从低电平变成高电平

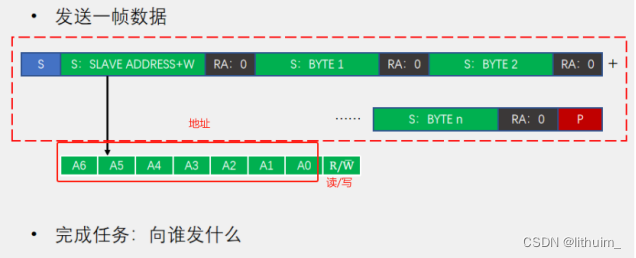

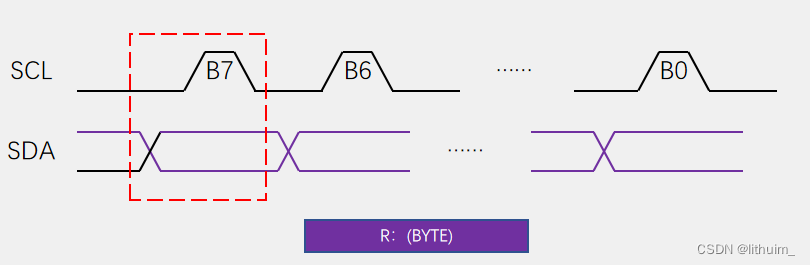

发送一个字节:SCL低电平期间,主机将数据位依次放到SDA线上(高位在前),然后拉高SCL,从机将在SCL高电平期间读取数据位,所以SCL高电平期间SDA不允许有数据变化,依次循环上述过程8次,即可发送一个字节

下面不是两根线只是两种情况根据前面SDA是处于高电平还是低电平来确定的。

接收一个字节:SCL低电平期间,从机将数据位依次放到SDA线上(高位在前),然后拉高SCL,主机将在SCL高电平期间读取数据位,所以SCL高电平期间SDA不允许有数据变化,依次循环上述过程8次,即可接收一个字节(主机在接收之前,需要释放SDA,也就是置1)

发送应答:在接收完一个字节之后,主机在下一个时钟发送一位数据,数据0表示应答,数据1表示非应答

接收应答:在发送完一个字节之后,主机在下一个时钟接收一位数据,判断从机是否应答,数据0表示应答,数据1表示非应答(主机在接收之前,需要释放SDA)

都是对主机而言的,发送应答指的是主机接收从机数据,然后主机给从机发送应答。1表示非应答是因为默认为1,如果从机根本不存在是1,从机不应答也是1,只有从机应答才是0。

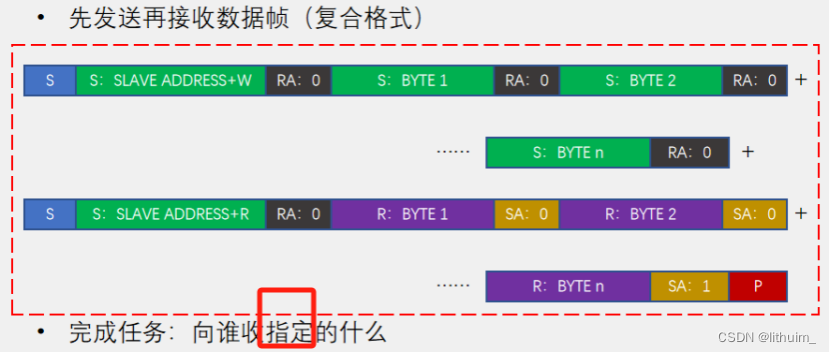

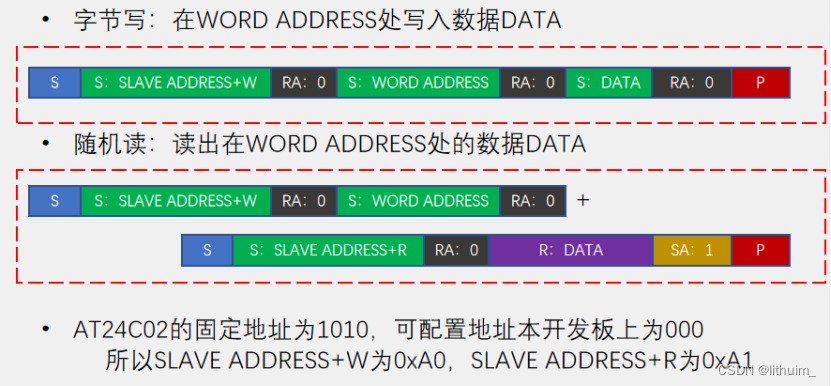

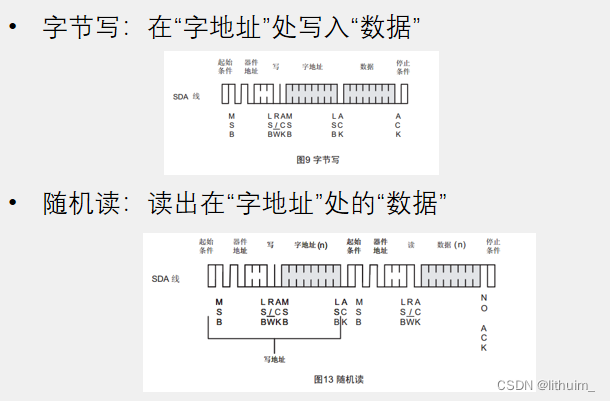

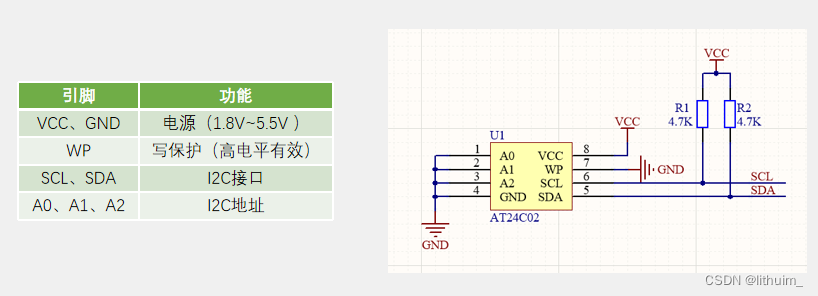

SLAVE ADDRESS 是AT24C02的地址,WORD ADDRESS是AT24C02这个设备要写入数据的地址。