Q:有编码器那对应的就会有译码器,本期我们来设计实现2线-4线二进制译码器 。

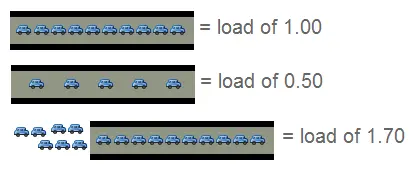

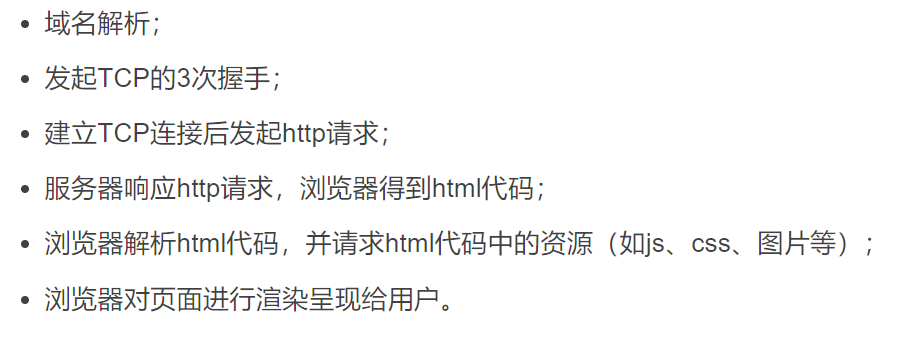

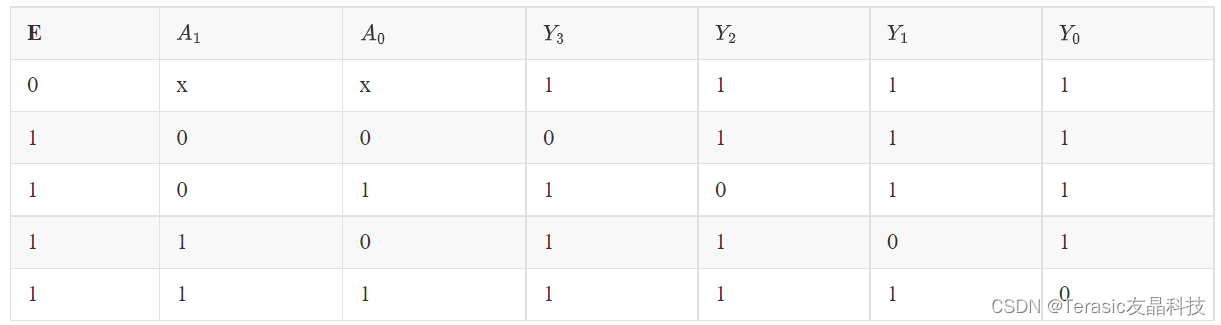

A:基本原理:译码器是编码器的逆过程,其功能是将具有特定含义的二进制码转换为对应的输出信号。2线-4线二进制译码器有2个输入共4种不同的组合状态,因此可以解码出4组输出信号。这里我们还设置使能信号,只有使能信号为“1”时译码器才会工作,否则输出全为1。

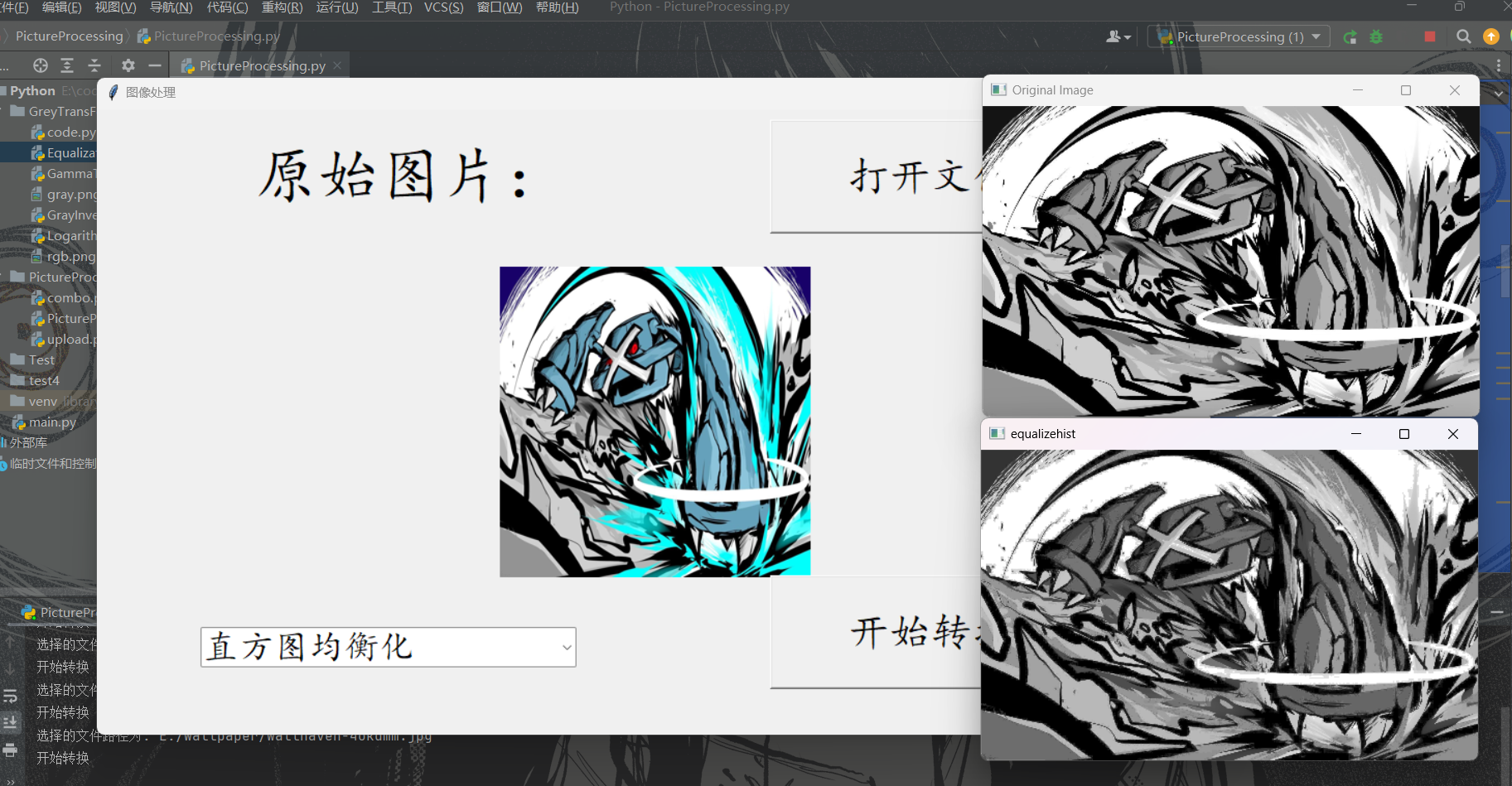

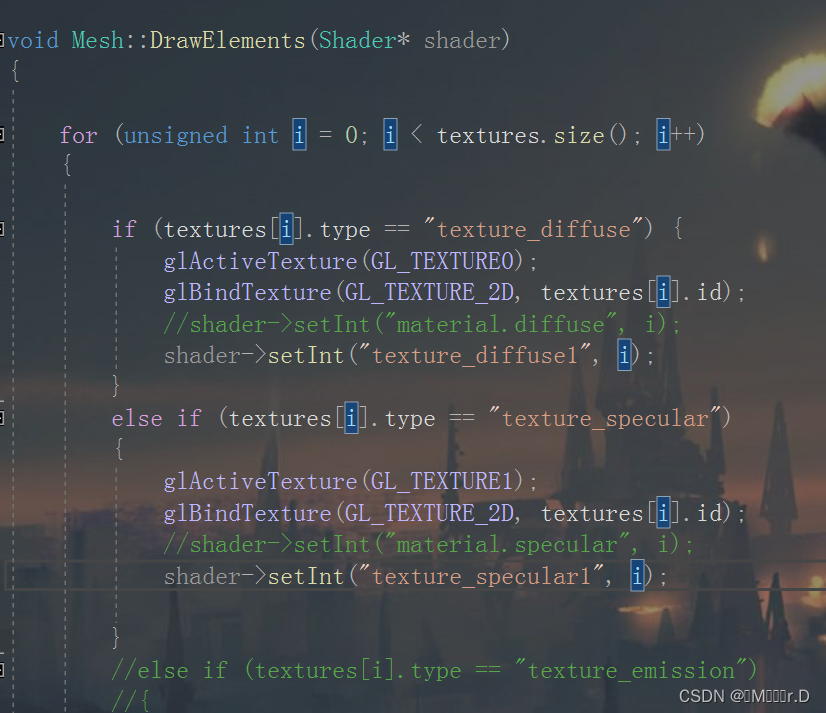

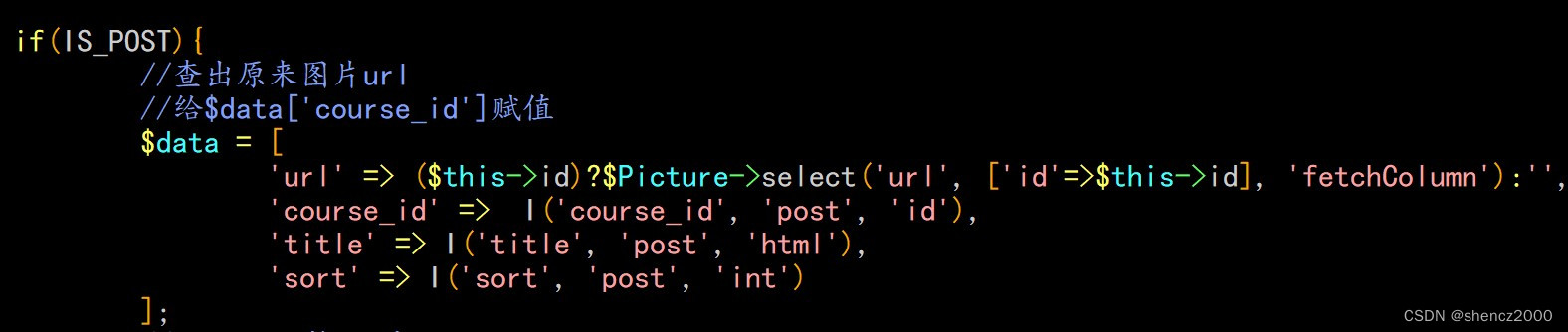

用Verilog过程结构always表示部分代码:

使用DE2-115开发板的SW[1:0]作为输入,SW[2]为使能信号输入,LEDR[3:0]显示译码器输出值,在顶层.v文件中例化2线-4线译码器。