-

主存储器,简称主存。CPU可以直接随机地对其进行访问,也可以和高速缓存器及辅助存储器交换数据。

-

2> 辅助存储器,简称辅存,不能与CPU直接相连,用来存放当前暂时不用的程序和数据

-

3> 高速缓冲存储器,位于主存和CPU之间,用来存放正在执行的程序段和数据

-

随机存储器(RAM)。存储器的任何一个存储单元的内容都可以随机存取,而且存取时间与存取单元的物理位置无关,主要用作主存或高速缓冲存储器。

2> 只读存储器(ROM)。存储器的内容只能随机读出而不能写入。。即使断电,内容也不会丢失。

3> 串行访问存储器。对存储单元进行读/写操作时,需按其物理位置的先后顺序寻址,包括顺序存取存储器(如磁带)与直接存取存储器(如磁盘)。

位扩展是地址线占用,然后扩展每位的字节,即接到数据总线上进行利用

字扩展是地址线没用完,然后把地址线进行译码器去选,可以扩充容量

位扩展扩展的是单价,字扩展扩展的是数量

1K是2^10,那么2k就是2^11

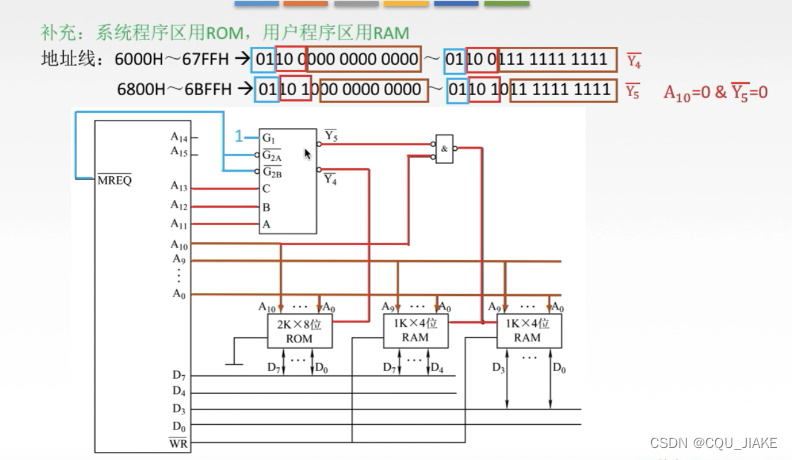

片选线就是去选哪个芯片进行操作,程序分为两种,一种是系统程序区,另一种是用户程序区,选用不同的芯片,一般系统CPU地址线数量大于芯片要求的数量,因为要实现片选,也是字扩展

主存与CPU连接,外存(辅存)不与CPU连接

这个就是算完后,系统程序区的大小比用户程序区大,所以分配给系统程序区的地址线数量就多,ROM芯片的大小也就大。一整个主存存储系统与用户,分别用RAM与ROM进行存储,然后就是CPU与这一些列芯片进行连接(这一系列芯片就是主存)。

主存地址物理上是在不同芯片的,可能是不连续的。但逻辑地址是连续的

这个就是说主存逻辑地址上是连续的一片,即6000H~6BFFH,但是划分为系统程序区以及用户程序区,用不同的芯片进行存储。对于CPU的地址线,有一些地址线通过译码驱动部分电路(即译码器)来进行对芯片片选,译码器还需要MREQ来进行使能访问,一共用三个芯片。

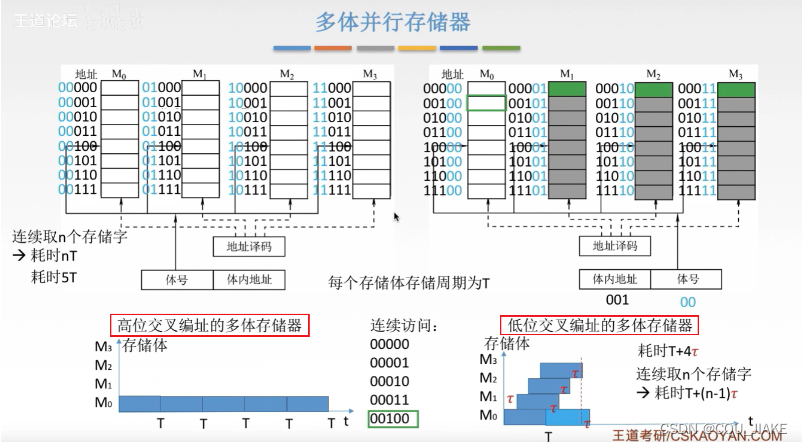

以上是说那一系列芯片构成一个主存,逻辑指令地址在一个主存上连续,可能在不同芯片不连续,但不影响。而多体并行存储器是说逻辑地址连续,但是是在不同的主存上的(不管主存内是怎么实现的),插了多个主存条后,进行编址有高位和低位,低位的话就是连续的逻辑地址访问的是不同的主存条,高位的话就不是,因此低位的话可以加快存储周期,而高位的话只是单纯的扩展内存容量。存储周期就是包含写以及恢复,如果低位的话,逻辑上的连续就可以实现存储周期等于写

交叉存储器实际上是一种模块式的存储器,它能并行执行多个独立的读/写操作。

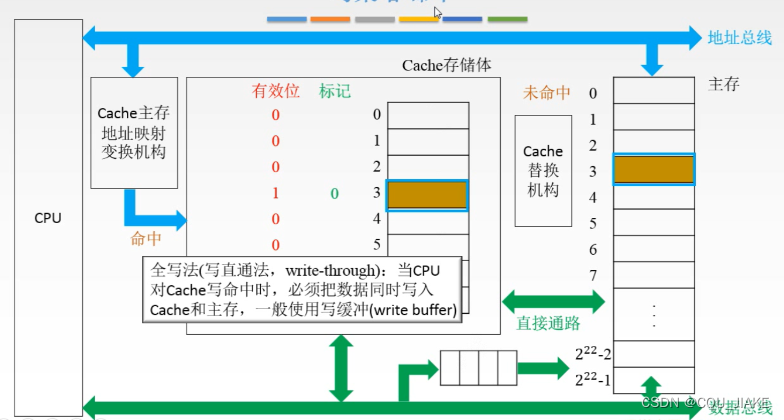

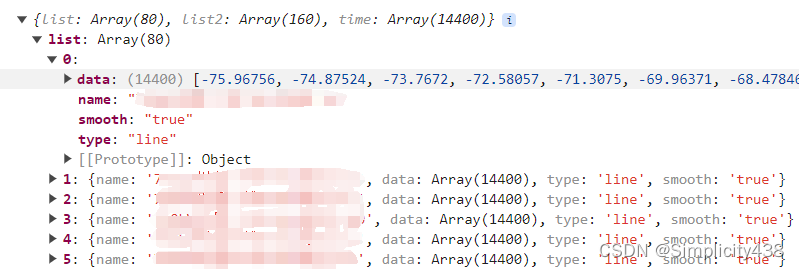

主存地址大小是256MB,1M是2^20,256=2^8,所以主存一共需要28位二进制,由于CACHE行长为64B,CHCHE里要记录主存字块标记,所以主存的字块标记有6位

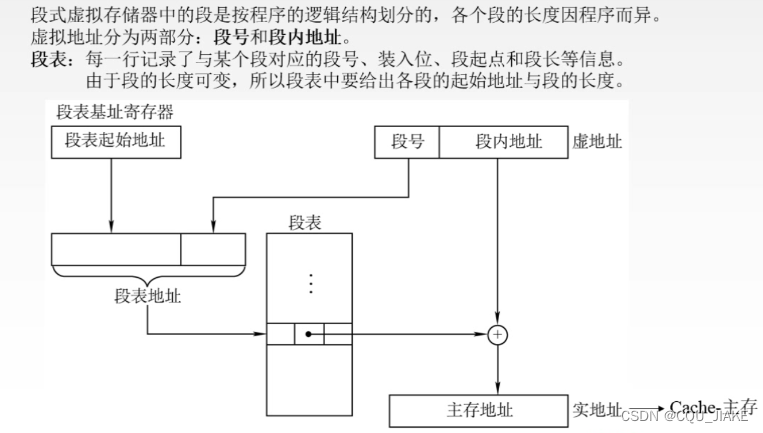

段页式虚拟存储器

把程序按逻辑结构分段,每段再划分为固定大小的页,

主存空间也划分为大小相等的页,

程序对主存的调入、调出仍以页为基本传送单位。

每个程序对应一个段表,每段对应一个页表

虚拟地址:段号+段内页号+页内地址

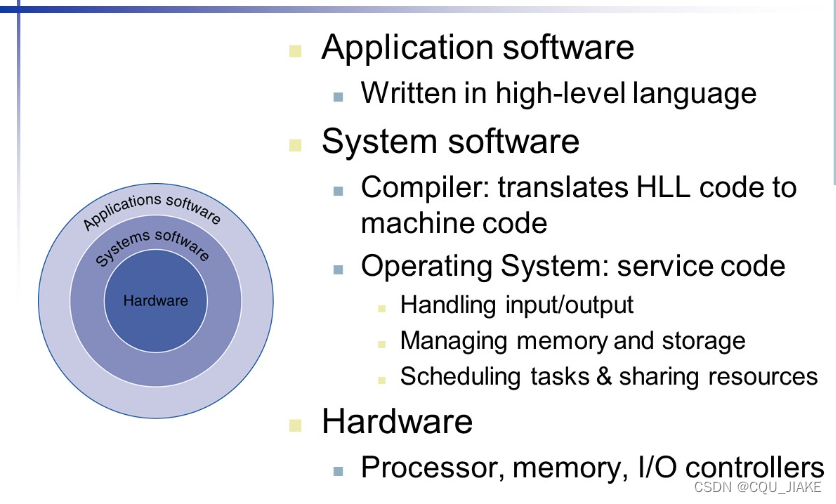

存储器的层次结构主要体现在 Cache-主存和 主存-辅存这两个存储层次上。

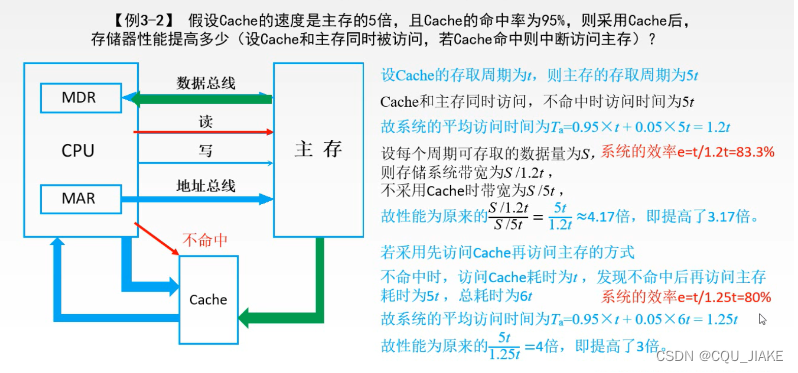

Cache-主存层次在存储系统中主要 对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于 Cache的速度,而寻址空间和位价却接近于主存。

主存-辅存层次在存储系统中主要 起扩容作用,即从程序员的角度看,他所使用的存储器的容量和位价接近于辅存,而速度接近于主存。

综合上述两个存储层次的作用,从整个存储系统来看,就达到了速度快、容量大、位价低的优化效果。

主存与 Cache之间的信息调度功能全部由硬件自动完成。而主存与辅存层次的调度目前广泛采用虚拟存储技术实现,即将主存与辅存的一部分通过软/硬结合的技术组成虚拟存储器,程序员可用这个比主存实际空间(物理地址空间)大得多的虚拟地址空间(逻辑地址空间)编程,当程序运行时,再由软/硬件自动配合完成虚拟地址空间与主存实际物理空间的转换。因此,这两个层次上的调度或转换操作对于程序员来说都是透明的。

存取周期和存取时间的主要区别是:存取时间仅为完成一次操作的时间;而存取周期不仅包含操作时间,而且包含操作后线路的恢复时间,即存取周期=存取时间+恢复时间。

页面不能设置得过大,也不能设置得过小。因为页面太小时,平均页内剩余空间较少,可节省存储空间,但会使得页表增大,而且页面太小时不能充分利用访存的空间局部性来提高命中率;页面太大时,可减少页表空间,但平均页内剩余空间较大,会浪费较多存储空间,页面太大还会使页面调入/调出的时间较长

发生取指令 Cache缺失的处理过程是什么?

1)程序计数器恢复当前指令的值。

2)对主存进行读的操作。

3)将读入的指令写入 Cache中,更改有效位和标记位。

4)重新执行当前指令。

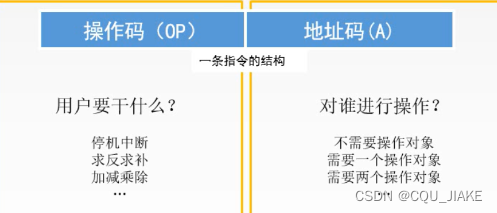

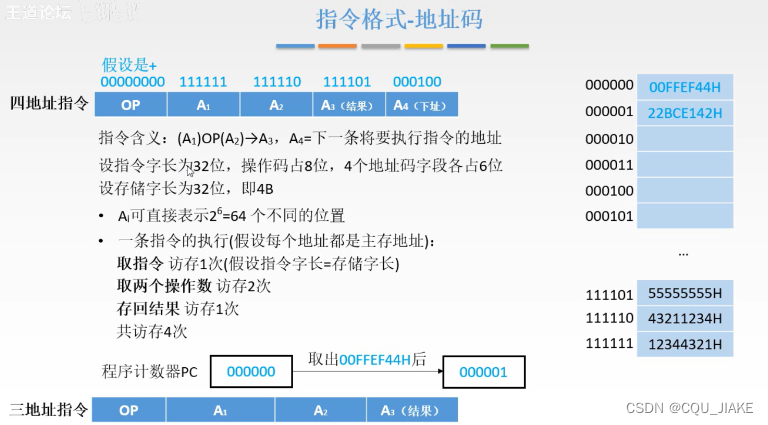

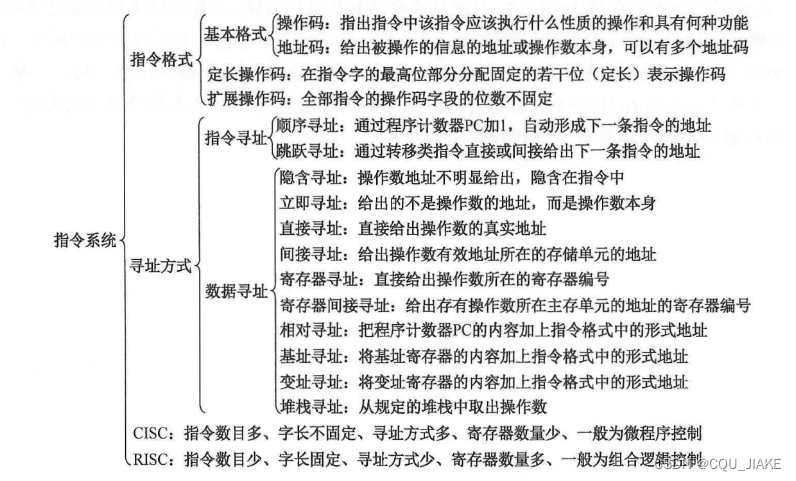

就是说A1和A2地址上的数据进行OP操作,然后存到A3位置上,A4是下一个地址

这个图就是说地址是那6位,这6位确定64个,然后每个上都有存储数据(比如00FF……)

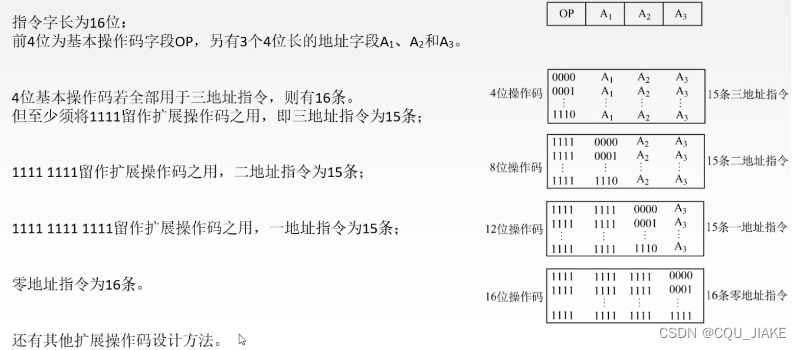

每层往下的那个1都被保留,目的就是为了进行区分,这样做的话,虽然哦操作码的位数增长了,但实际变化的操作码数量并没有发生变化,所以对于每个地址数量的操作码而言,可进行的操作数量并没有发生太大变化,增长操作码,就会减少地址码,那么就是压缩了寻址空间

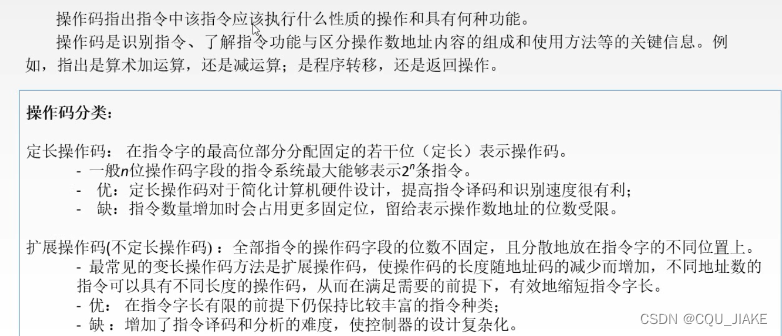

指令字长固定为16位(就是说操作码+地址码长度为16),要15条三地址指令,那么至少需要4位可变操作码。需要的操作数越多,那么需要的可变操作码数量也就越多。

若采用定长操作码的话,操作码的数量取决于最长的、需要的操作数。这样的话对于不需要那么多的操作的指令就造成了浪费

对于三地址指令,四位可变的,需要15种,那么会留出一种;对于12条二地址,至少需要4位可变的,需要4位,留出4种;对于一地址指令,62种,至少要6位,上层留出4种,则本层只需要4位,所以最后留出2种

采用扩展操作码后,就可以使寻址范围小的数据有长的操作码,最终目的以及实现效果是有效缩短指令长度

指令转移里的地址码就是指令的地址,而不是数据、操作数的地址

寻址特征就是说怎么找到操作数的位置,形式地址的目的是为了找到操作数的真实地址,

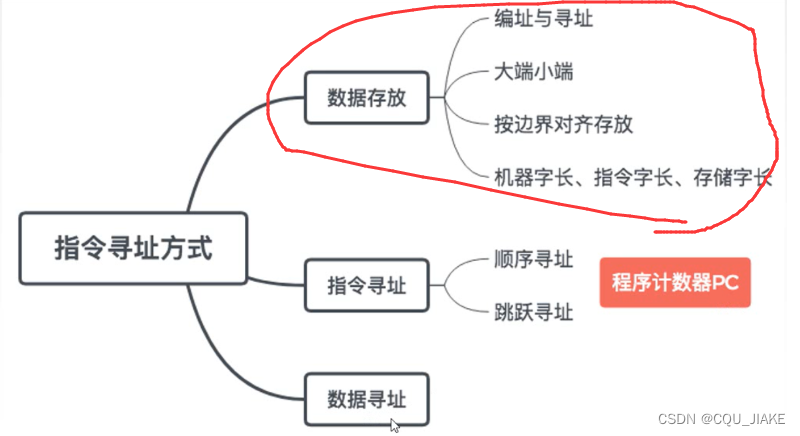

指令寻址方式(存放)

按字节编址,按字编址

虚拟存储器

什么是页表基址寄存器

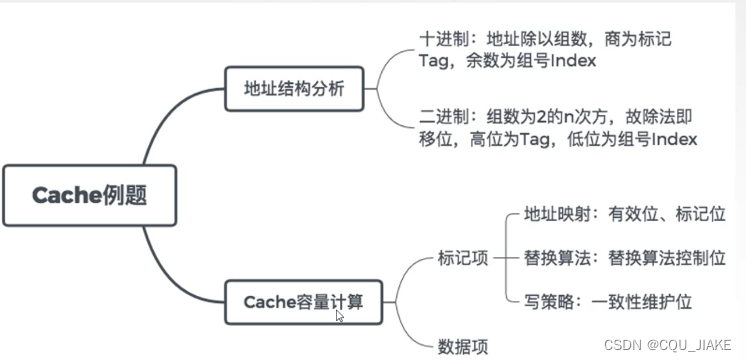

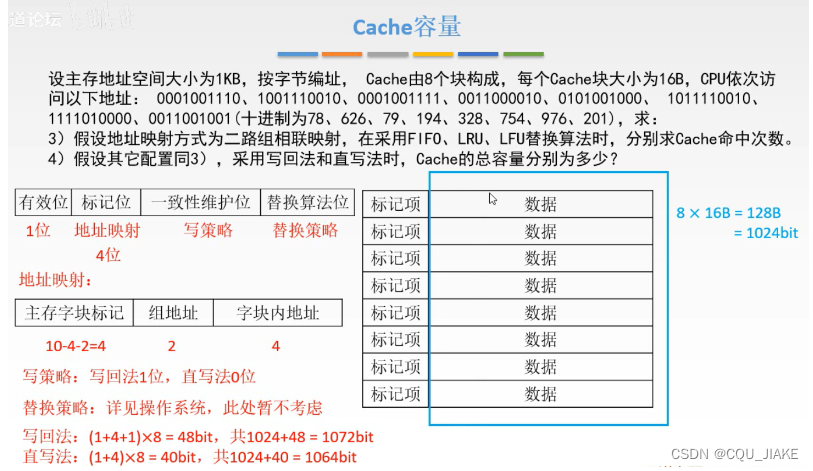

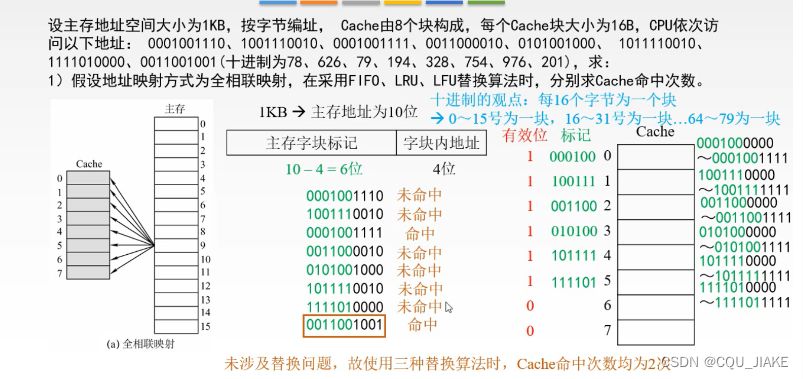

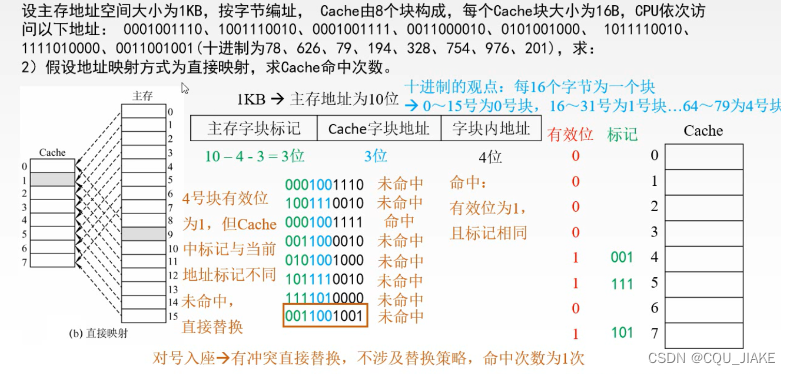

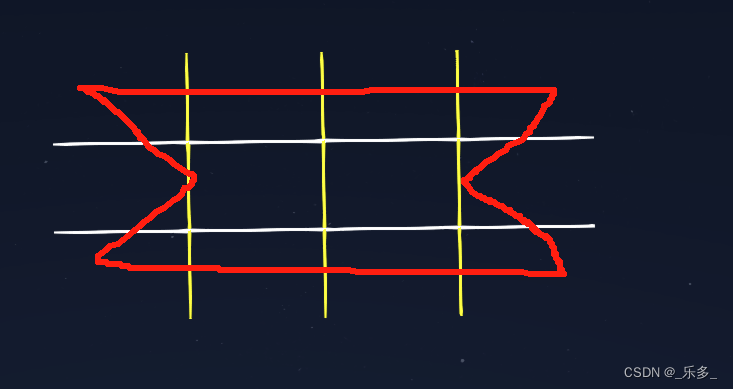

CACHE映射

![[PwnThyBytes 2019]Baby_SQL](https://img-blog.csdnimg.cn/img_convert/b95e731e2f49f08f5262001679a5bdd7.png)