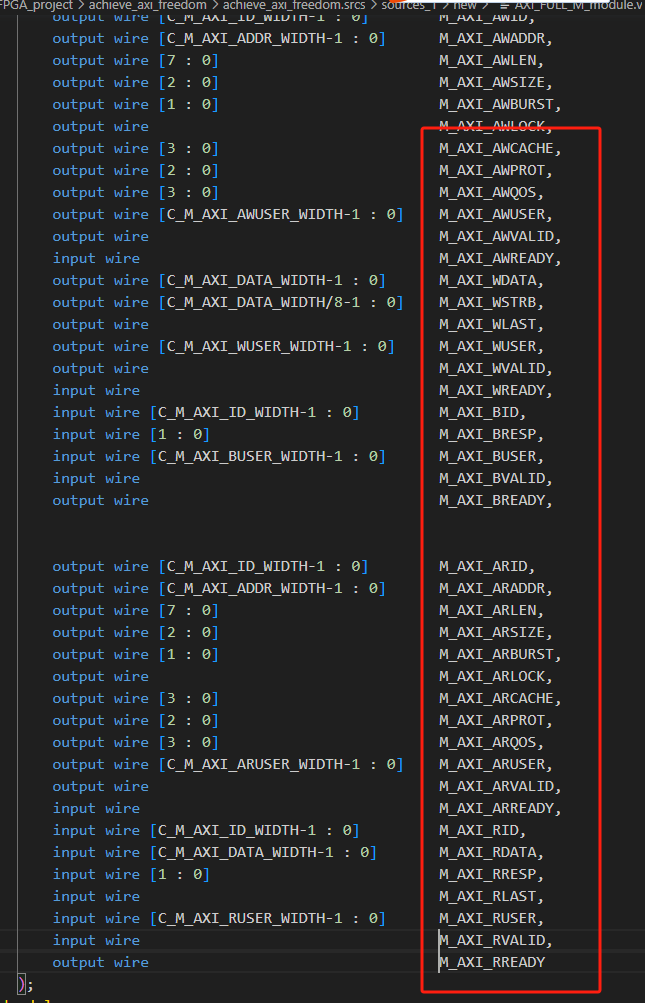

可以用来优化代码排布,让变量整齐成为一排

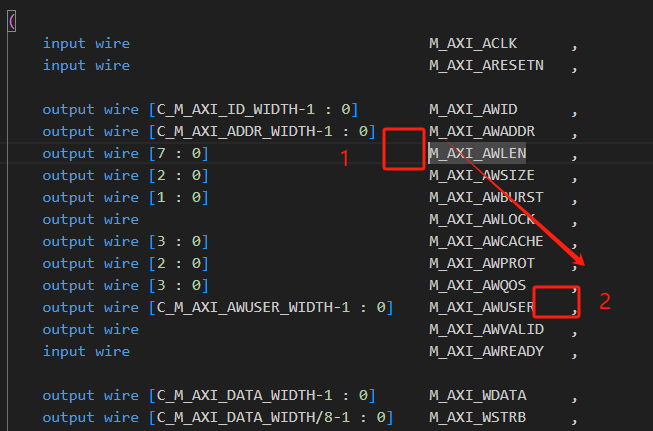

一、批量复制:

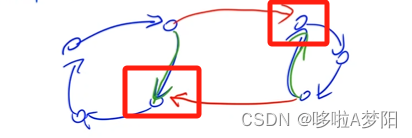

在1处左键单击,然后摁住SHIFT+ALT键的同时,左键单击2处,即可复制一整块的内容

如果所示

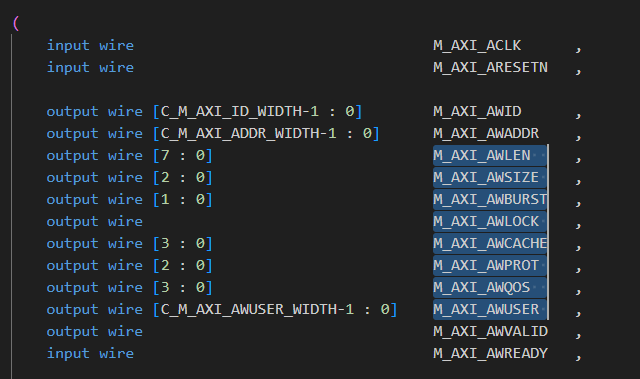

就可以复制了

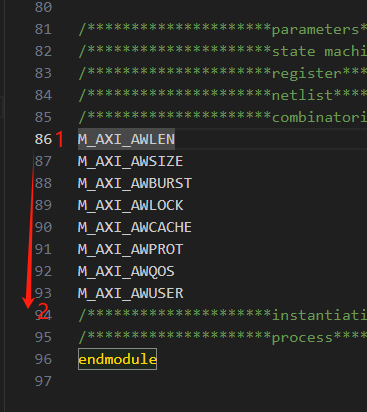

二、批量输入

在1处左键单击,然后摁住SHIFT+ALT键的同时,左键单击2处,

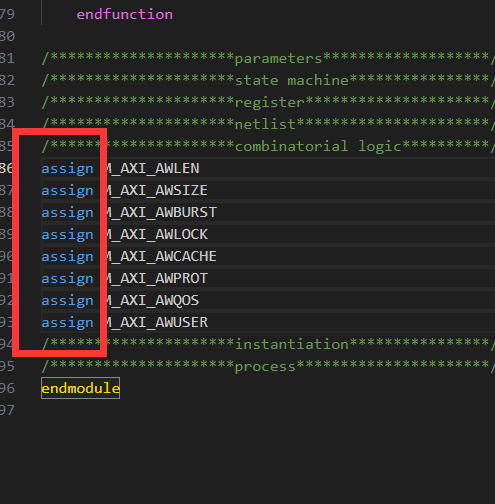

正常输入即可给所有行添加assign关键字

module AXI_FULL_M_module #

(

parameter C_M_TARGET_SLAVE_BASE_ADDR = 32'h40000000 ,

parameter integer C_M_AXI_BURST_LEN = 16 ,

parameter integer C_M_AXI_ID_WIDTH = 1 ,

parameter integer C_M_AXI_ADDR_WIDTH = 32 ,

parameter integer C_M_AXI_DATA_WIDTH = 32 ,

parameter integer C_M_AXI_AWUSER_WIDTH = 0 ,

parameter integer C_M_AXI_ARUSER_WIDTH = 0 ,

parameter integer C_M_AXI_WUSER_WIDTH = 0 ,

parameter integer C_M_AXI_RUSER_WIDTH = 0 ,

parameter integer C_M_AXI_BUSER_WIDTH = 0

)

(

input wire M_AXI_ACLK ,

input wire M_AXI_ARESETN ,

output wire [C_M_AXI_ID_WIDTH-1 : 0] M_AXI_AWID ,

output wire [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_AWADDR ,

output wire [7 : 0] M_AXI_AWLEN ,

output wire [2 : 0] M_AXI_AWSIZE ,

output wire [1 : 0] M_AXI_AWBURST ,

output wire M_AXI_AWLOCK ,

output wire [3 : 0] M_AXI_AWCACHE ,

output wire [2 : 0] M_AXI_AWPROT ,

output wire [3 : 0] M_AXI_AWQOS ,

output wire [C_M_AXI_AWUSER_WIDTH-1 : 0] M_AXI_AWUSER ,

output wire M_AXI_AWVALID ,

input wire M_AXI_AWREADY ,

output wire [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_WDATA ,

output wire [C_M_AXI_DATA_WIDTH/8-1 : 0] M_AXI_WSTRB ,

output wire M_AXI_WLAST ,

output wire [C_M_AXI_WUSER_WIDTH-1 : 0] M_AXI_WUSER ,

output wire M_AXI_WVALID ,

input wire M_AXI_WREADY ,

input wire [C_M_AXI_ID_WIDTH-1 : 0] M_AXI_BID ,

input wire [1 : 0] M_AXI_BRESP ,

input wire [C_M_AXI_BUSER_WIDTH-1 : 0] M_AXI_BUSER ,

input wire M_AXI_BVALID ,

output wire M_AXI_BREADY ,

output wire [C_M_AXI_ID_WIDTH-1 : 0] M_AXI_ARID ,

output wire [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_ARADDR ,

output wire [7 : 0] M_AXI_ARLEN ,

output wire [2 : 0] M_AXI_ARSIZE ,

output wire [1 : 0] M_AXI_ARBURST ,

output wire M_AXI_ARLOCK ,

output wire [3 : 0] M_AXI_ARCACHE ,

output wire [2 : 0] M_AXI_ARPROT ,

output wire [3 : 0] M_AXI_ARQOS ,

output wire [C_M_AXI_ARUSER_WIDTH-1 : 0] M_AXI_ARUSER ,

output wire M_AXI_ARVALID ,

input wire M_AXI_ARREADY ,

input wire [C_M_AXI_ID_WIDTH-1 : 0] M_AXI_RID ,

input wire [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_RDATA ,

input wire [1 : 0] M_AXI_RRESP ,

input wire M_AXI_RLAST ,

input wire [C_M_AXI_RUSER_WIDTH-1 : 0] M_AXI_RUSER ,

input wire M_AXI_RVALID ,

output wire M_AXI_RREADY

);

/*********************caculate data width*******************/

//example of this function

//init: number=3 or b'11 clogb2=0

//cycle 1: number=b'1 clogb2=1

//cycle 2: number=b'0 clogb2=2

//cycle 3: number=b'0 is not >0 ,abondon this cycle, return clogb2=2

//this is the addr width of number

function integer clogb2(input integer number);

begin

for(clogb2= 0; number> 0 ; clogb2= clogb2+ 1)

number= number>> 1;

end

endfunction

/*********************parameters****************************/

/*********************state machine*************************/

/*********************register******************************/

/*********************netlist*******************************/

/*********************combinatorial logic*******************/

//the length of each burst

assign M_AXI_AWLEN = C_M_AXI_BURST_LEN ;

//will decode into the width of data

assign M_AXI_AWSIZE = clogb2(C_M_AXI_DATA_WIDTH/8-1);

//type of burst FIXED,INCR,WRAP respectively correspond to code 00,01,10

assign M_AXI_AWBURST = 2'b01 ;

//normally useless. so use 0

assign M_AXI_AWLOCK = 'd0 ;

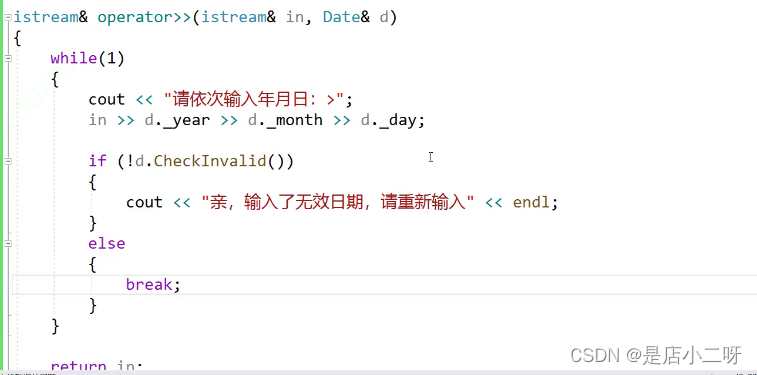

assign M_AXI_AWCACHE =

assign M_AXI_AWPROT =

assign M_AXI_AWQOS =

assign M_AXI_AWUSER =

/*********************instantiation*************************/

/*********************process*******************************/

endmodule