关于如何在Multisim导入TI提供的SPICE模型,该篇博客描述的很清楚:在Multisim导入TI提供的SPICE模型_multisim如何导入元器件的仿真模型-CSDN博客

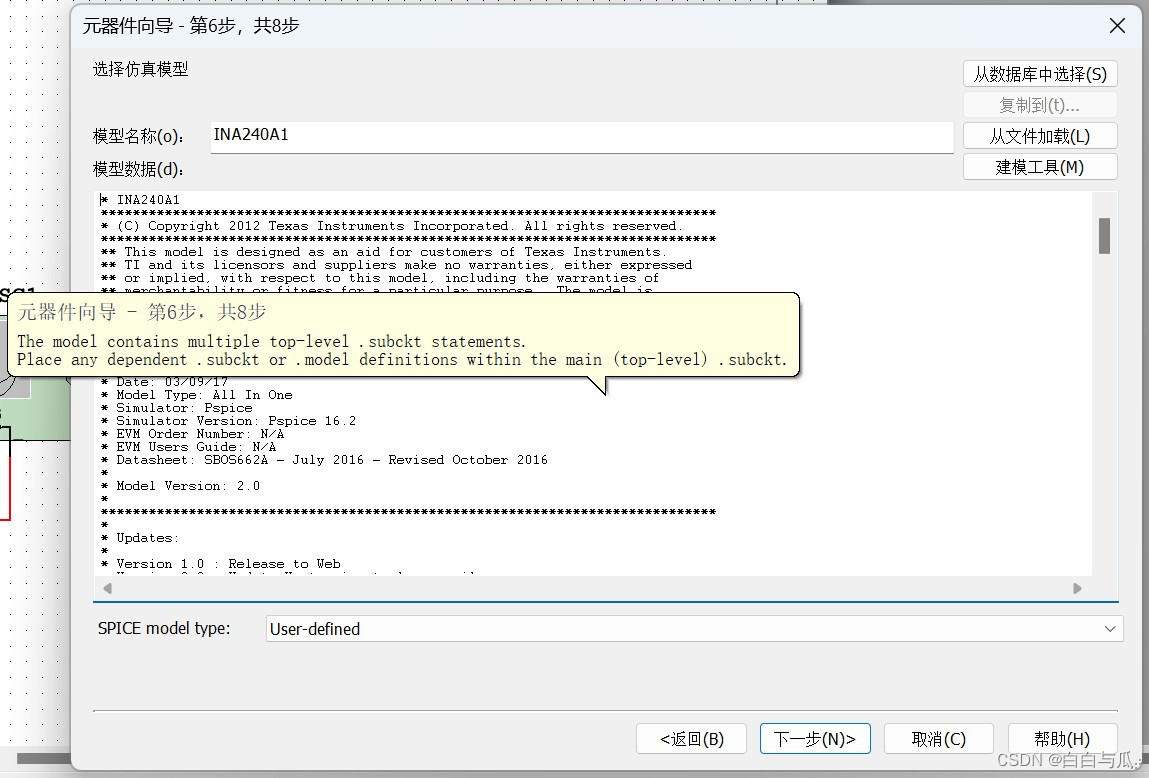

但是使用13或14版本的Multisim在操作过程中可能会遇到如下问题:

The model contains multiple top-level . subckt statements.

Place any dependent . subckt or .model definitions within the main (top-level) . subckt.翻译:模型包含多个顶层 .subckt 语句。将任何从属 .subckt 或 .model 定义放在主(顶层).subckt 中。

关于这个问题,跟着视频multisim自定义元件_哔哩哔哩_bilibili的06:10开始操作可解决。具体操作如下:

找到第一个“.ENDS”,而后将其前面加上“*”,以下面INA240A1代码为例:

* INA240A1

*****************************************************************************

* (C) Copyright 2012 Texas Instruments Incorporated. All rights reserved.

*****************************************************************************

** This model is designed as an aid for customers of Texas Instruments.

** TI and its licensors and suppliers make no warranties, either expressed

** or implied, with respect to this model, including the warranties of

** merchantability or fitness for a particular purpose. The model is

** provided solely on an "as is" basis. The entire risk as to its quality

** and performance is with the customer.

*****************************************************************************

*

** Released by: WEBENCH(R) Design Center, Texas Instruments Inc.

* Part: INA240A1

* Date: 03/09/17

* Model Type: All In One

* Simulator: Pspice

* Simulator Version: Pspice 16.2

* EVM Order Number: N/A

* EVM Users Guide: N/A

* Datasheet: SBOS662A - July 2016 - Revised October 2016

*

* Model Version: 2.0

*

*****************************************************************************

*

* Updates:

*

* Version 1.0 : Release to Web

* Version 2.0 : Update Vout swing to lower rail

* Add overdrive recovery circuit

*

*****************************************************************************

* Notes:

* The model reflects the following parameters:

* Common-mode input range, CMRR, VOS, IIB, Gain, BW, Vout versus Iout,

* slew rate, noise, power supply range, IQ.

* The model does not track device behavior over temperature

*

*****************************************************************************

*$

.SUBCKT INA240A1 OUT INP INN REF1 REF2 VCC GND

E_E2 N61051 0 GND 0 -1

E_E11 INP_BUF_OUT GND INP GND 1

X_U12 INPUT_TF INPUT_VCLAMP VCC GND EN GNDF TF_INA240A1

E_E12 INN_BUF_OUT GND N409527 GND 1

X_U31 INPUT_VIMON OUT VIMON GNDF AMETER_INA240A1

R_R19 INPUT_OUTP N348841 475k TC=0,0

X_U35 EN VICM VCC GND GNDF CONTROL_INA240A1

X_U18 INP GNDF VCC GND VICM GNDF IIBP_INA240A1

R_R11 INPUT_ZOUT INPUT_VIMON 10 TC=0,0

X_U5 VICM INP INN GNDF VICM_INA240A1

E_E13 INP_BUF_OUT INP_CMRR VICM GNDF 1

R_R16 GND INP 500k TC=0,0

X_U13 INPUTP_GBW INPUTN_GBW INPUT_TF EN VCC GND GNDF GBW_SLEW_INA240A1

E_E14 INN_BUF_OUT INN_CMRR VICM GNDF 1

V_V8 INN N409527 -7.625uVdc

X_U20 VCC GND EN VIMON GNDF IQ_INA240A1

X_U33 VCC GND INP_PSRR_IN INP_PSRR_OUT GNDF PSRR_INA240A1

X_U17 INN GNDF VCC GND VICM GNDF IIBN_INA240A1

R_R4 INN_CMRR INPUTN_GBW 25k TC=0,0

G_G1 GNDF N504417 VICM GNDF 0.25u

X_U34 VCC GND INPUT_VCLAMP INPUT_ZOUT VIMON NDUMMY GNDF VOUTvsIOUT_NROS_SHDN_INA240A1

VDUMMY NDUMMY GNDF 1V

E_E16 INP_CMRR INP_PSRR_IN N504417 GNDF 1

R_R18 OUT INPUTN_GBW 500k TC=0,0

R_R12 REF2 N348841 50k TC=0,0

R_R8 REF1 N348841 50k TC=0,0

R_R3 INP_PSRR_OUT INPUT_OUTP 25k TC=0,0

R_R20 N506257 GNDF 1 TC=0,0

X_U32 INPUT_OUTP INPUTP_GBW vnse_INA240A1

E_E3 GNDF 0 N61045 N61051 0.5

L_L1 N504417 N506257 400uH

R_R17 INN GND 500k TC=0,0

E_E1 N61045 0 VCC 0 1

.ENDS将最后一行的“.ENDS”改为“*.ENDS”:

* INA240A1

*****************************************************************************

* (C) Copyright 2012 Texas Instruments Incorporated. All rights reserved.

*****************************************************************************

** This model is designed as an aid for customers of Texas Instruments.

** TI and its licensors and suppliers make no warranties, either expressed

** or implied, with respect to this model, including the warranties of

** merchantability or fitness for a particular purpose. The model is

** provided solely on an "as is" basis. The entire risk as to its quality

** and performance is with the customer.

*****************************************************************************

*

** Released by: WEBENCH(R) Design Center, Texas Instruments Inc.

* Part: INA240A1

* Date: 03/09/17

* Model Type: All In One

* Simulator: Pspice

* Simulator Version: Pspice 16.2

* EVM Order Number: N/A

* EVM Users Guide: N/A

* Datasheet: SBOS662A - July 2016 - Revised October 2016

*

* Model Version: 2.0

*

*****************************************************************************

*

* Updates:

*

* Version 1.0 : Release to Web

* Version 2.0 : Update Vout swing to lower rail

* Add overdrive recovery circuit

*

*****************************************************************************

* Notes:

* The model reflects the following parameters:

* Common-mode input range, CMRR, VOS, IIB, Gain, BW, Vout versus Iout,

* slew rate, noise, power supply range, IQ.

* The model does not track device behavior over temperature

*

*****************************************************************************

*$

.SUBCKT INA240A1 OUT INP INN REF1 REF2 VCC GND

E_E2 N61051 0 GND 0 -1

E_E11 INP_BUF_OUT GND INP GND 1

X_U12 INPUT_TF INPUT_VCLAMP VCC GND EN GNDF TF_INA240A1

E_E12 INN_BUF_OUT GND N409527 GND 1

X_U31 INPUT_VIMON OUT VIMON GNDF AMETER_INA240A1

R_R19 INPUT_OUTP N348841 475k TC=0,0

X_U35 EN VICM VCC GND GNDF CONTROL_INA240A1

X_U18 INP GNDF VCC GND VICM GNDF IIBP_INA240A1

R_R11 INPUT_ZOUT INPUT_VIMON 10 TC=0,0

X_U5 VICM INP INN GNDF VICM_INA240A1

E_E13 INP_BUF_OUT INP_CMRR VICM GNDF 1

R_R16 GND INP 500k TC=0,0

X_U13 INPUTP_GBW INPUTN_GBW INPUT_TF EN VCC GND GNDF GBW_SLEW_INA240A1

E_E14 INN_BUF_OUT INN_CMRR VICM GNDF 1

V_V8 INN N409527 -7.625uVdc

X_U20 VCC GND EN VIMON GNDF IQ_INA240A1

X_U33 VCC GND INP_PSRR_IN INP_PSRR_OUT GNDF PSRR_INA240A1

X_U17 INN GNDF VCC GND VICM GNDF IIBN_INA240A1

R_R4 INN_CMRR INPUTN_GBW 25k TC=0,0

G_G1 GNDF N504417 VICM GNDF 0.25u

X_U34 VCC GND INPUT_VCLAMP INPUT_ZOUT VIMON NDUMMY GNDF VOUTvsIOUT_NROS_SHDN_INA240A1

VDUMMY NDUMMY GNDF 1V

E_E16 INP_CMRR INP_PSRR_IN N504417 GNDF 1

R_R18 OUT INPUTN_GBW 500k TC=0,0

R_R12 REF2 N348841 50k TC=0,0

R_R8 REF1 N348841 50k TC=0,0

R_R3 INP_PSRR_OUT INPUT_OUTP 25k TC=0,0

R_R20 N506257 GNDF 1 TC=0,0

X_U32 INPUT_OUTP INPUTP_GBW vnse_INA240A1

E_E3 GNDF 0 N61045 N61051 0.5

L_L1 N504417 N506257 400uH

R_R17 INN GND 500k TC=0,0

E_E1 N61045 0 VCC 0 1

*.ENDS而后找到文件代码最后一个“.ENDS”和“*$”:

*$

*

.SUBCKT VOUTvsIOUT_NROS_SHDN_INA240A1 VCC VEE VI VO VIMON SHDN GNDF

.PARAM ISC_POS = 0.003

.PARAM ISC_NEG = -0.0055

.PARAM IMAXLIN_POS = 0.0024

.PARAM IMAXLIN_NEG = -0.0045

.PARAM VOUTMAXLIN = 4.8

.PARAM VOUTMINLIN = 0.4

.PARAM VHR_VCC = -0.05

.PARAM VHR_VEE = 0.001

.PARAM VCC_DATASHEET = 5

.PARAM VEE_DATASHEET = 0

.PARAM VMID_DATASHEET = {(VCC_DATASHEET + VEE_DATASHEET)/2}

.PARAM VHR_MAX_LINEAR = {VOUTMAXLIN - VCC_DATASHEET}

.PARAM VHR_MIN_LINEAR = {VOUTMINLIN - VEE_DATASHEET}

ER1 NR1 GNDF VALUE = {(VOUTMAXLIN - (VCC_DATASHEET + VHR_VCC))/IMAXLIN_POS}

ER2 NR2 GNDF VALUE = {(VOUTMINLIN - (VEE_DATASHEET + VHR_VEE))/IMAXLIN_NEG}

EVOUT1pos NVOUT1_MAX GNDF VALUE = {(V(VCC,GNDF) + VHR_VCC) + V(NR1,GNDF)*V(VIMON,GNDF)}

EVOUT1neg NVOUT1_MIN GNDF VALUE = {(V(VEE,GNDF) + VHR_VEE) + V(NR2,GNDF)*V(VIMON,GNDF)}

EM1 NM1 GNDF VALUE = {(VOUTMAXLIN - VMID_DATASHEET)/(IMAXLIN_POS - ISC_POS)}

EM2 NM2 GNDF VALUE = {(VOUTMINLIN - VMID_DATASHEET)/(IMAXLIN_NEG - ISC_NEG)}

EVMID NVMID GNDF VALUE = {(V(VCC,GNDF) + V(VEE,GNDF))/2}

E1 N1 GNDF VALUE = {V(VCC,GNDF) + VHR_MAX_LINEAR}

E2 N2 GNDF VALUE = {V(VEE,GNDF) + VHR_MIN_LINEAR}

EV1 NV1 GNDF VALUE = {V(NVMID,GNDF) + (V(N1,GNDF) - V(NVMID,GNDF))/(1 - IMAXLIN_POS/ISC_POS)}

EV2 NV2 GNDF VALUE = {V(NVMID,GNDF) + (V(N2,GNDF) - V(NVMID,GNDF))/(1 - IMAXLIN_NEG/ISC_NEG)}

EVOUT2pos NVOUT2_MAX GNDF VALUE = {V(NV1,GNDF) + V(VIMON,GNDF)*V(NM1,GNDF)}

EVOUT2neg NVOUT2_MIN GNDF VALUE = {V(NV2,GNDF) + V(VIMON,GNDF)*V(NM2,GNDF)}

EHRPOS HRPOS GNDF VALUE = {MIN(V(NVOUT1_MAX,GNDF),V(NVOUT2_MAX,GNDF))}

EHRNEG HRNEG GNDF VALUE = {MAX(V(NVOUT1_MIN,GNDF),V(NVOUT2_MIN,GNDF))}

ECLAMP VO GNDF VALUE = {V(SHDN,GNDF)*MAX(MIN(V(VI,GNDF), V(HRPOS,GNDF)), V(HRNEG,GNDF))}

.ENDS

*$

*在“.ENDS”和“*$”之间再加上一个“.ENDS”:

*$

*

.SUBCKT VOUTvsIOUT_NROS_SHDN_INA240A1 VCC VEE VI VO VIMON SHDN GNDF

.PARAM ISC_POS = 0.003

.PARAM ISC_NEG = -0.0055

.PARAM IMAXLIN_POS = 0.0024

.PARAM IMAXLIN_NEG = -0.0045

.PARAM VOUTMAXLIN = 4.8

.PARAM VOUTMINLIN = 0.4

.PARAM VHR_VCC = -0.05

.PARAM VHR_VEE = 0.001

.PARAM VCC_DATASHEET = 5

.PARAM VEE_DATASHEET = 0

.PARAM VMID_DATASHEET = {(VCC_DATASHEET + VEE_DATASHEET)/2}

.PARAM VHR_MAX_LINEAR = {VOUTMAXLIN - VCC_DATASHEET}

.PARAM VHR_MIN_LINEAR = {VOUTMINLIN - VEE_DATASHEET}

ER1 NR1 GNDF VALUE = {(VOUTMAXLIN - (VCC_DATASHEET + VHR_VCC))/IMAXLIN_POS}

ER2 NR2 GNDF VALUE = {(VOUTMINLIN - (VEE_DATASHEET + VHR_VEE))/IMAXLIN_NEG}

EVOUT1pos NVOUT1_MAX GNDF VALUE = {(V(VCC,GNDF) + VHR_VCC) + V(NR1,GNDF)*V(VIMON,GNDF)}

EVOUT1neg NVOUT1_MIN GNDF VALUE = {(V(VEE,GNDF) + VHR_VEE) + V(NR2,GNDF)*V(VIMON,GNDF)}

EM1 NM1 GNDF VALUE = {(VOUTMAXLIN - VMID_DATASHEET)/(IMAXLIN_POS - ISC_POS)}

EM2 NM2 GNDF VALUE = {(VOUTMINLIN - VMID_DATASHEET)/(IMAXLIN_NEG - ISC_NEG)}

EVMID NVMID GNDF VALUE = {(V(VCC,GNDF) + V(VEE,GNDF))/2}

E1 N1 GNDF VALUE = {V(VCC,GNDF) + VHR_MAX_LINEAR}

E2 N2 GNDF VALUE = {V(VEE,GNDF) + VHR_MIN_LINEAR}

EV1 NV1 GNDF VALUE = {V(NVMID,GNDF) + (V(N1,GNDF) - V(NVMID,GNDF))/(1 - IMAXLIN_POS/ISC_POS)}

EV2 NV2 GNDF VALUE = {V(NVMID,GNDF) + (V(N2,GNDF) - V(NVMID,GNDF))/(1 - IMAXLIN_NEG/ISC_NEG)}

EVOUT2pos NVOUT2_MAX GNDF VALUE = {V(NV1,GNDF) + V(VIMON,GNDF)*V(NM1,GNDF)}

EVOUT2neg NVOUT2_MIN GNDF VALUE = {V(NV2,GNDF) + V(VIMON,GNDF)*V(NM2,GNDF)}

EHRPOS HRPOS GNDF VALUE = {MIN(V(NVOUT1_MAX,GNDF),V(NVOUT2_MAX,GNDF))}

EHRNEG HRNEG GNDF VALUE = {MAX(V(NVOUT1_MIN,GNDF),V(NVOUT2_MIN,GNDF))}

ECLAMP VO GNDF VALUE = {V(SHDN,GNDF)*MAX(MIN(V(VI,GNDF), V(HRPOS,GNDF)), V(HRNEG,GNDF))}

.ENDS

.ENDS

*$

*而后保存即可。导入.cir文件时不会再报错。

以上操作通俗地来说就是:注释掉第一个“括号”后,把“括号”后移至全文末端,让全文都能包含在顶层 .subckt 语句中,从而避免多个.subckt 语句并行而导致读取出错。