1、概述

这篇文章简单介绍一下PCIE phy的均衡原理和过程,USB phy,ethernet phy这些高速的串行serdes也有相同或者相似的结构。可以不用太关注其中的细节,等到debug的时候可以查询协议,但是需要了解这个故事讲的大概内容。整个equalization过程是controller和phy一起配合完成的,但是均衡器和均衡算法在PHY中。为什么需要equalization和equalization起什么作用不在本篇介绍范围之内。

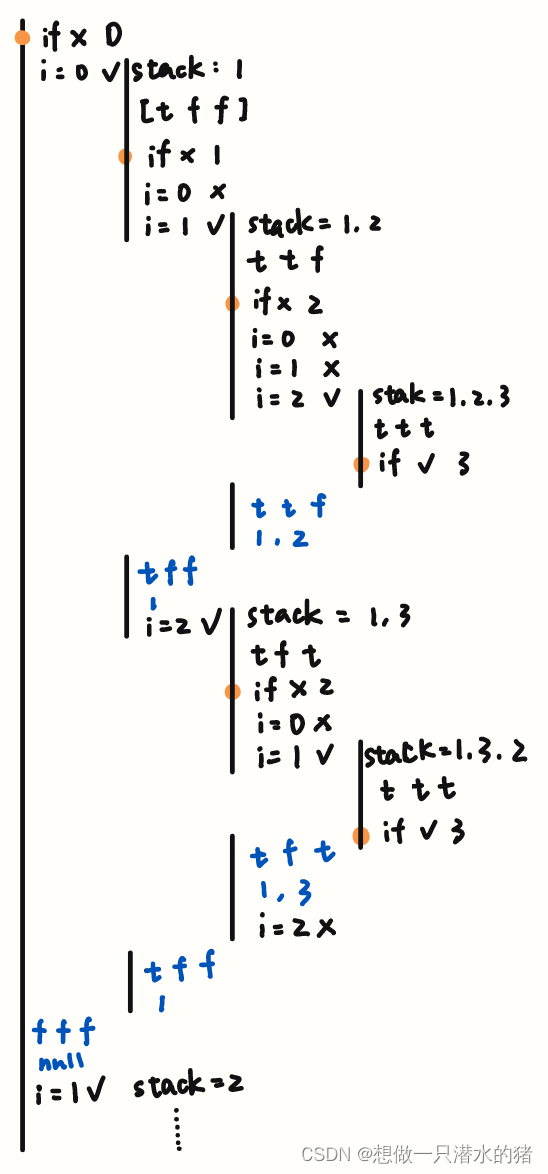

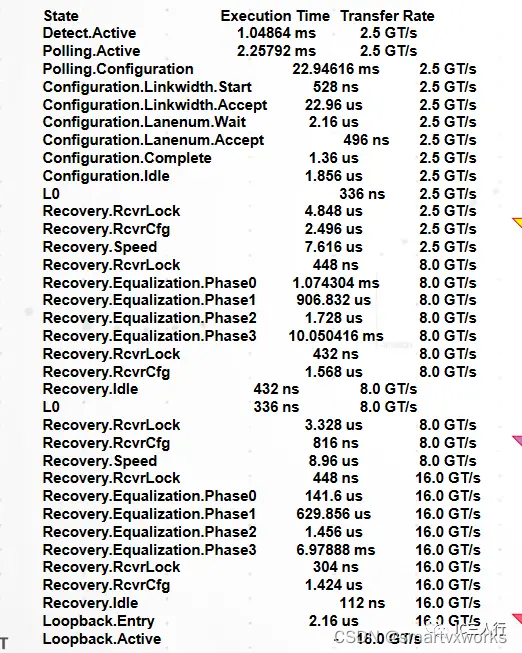

2、PCIE link training的时候状态机转

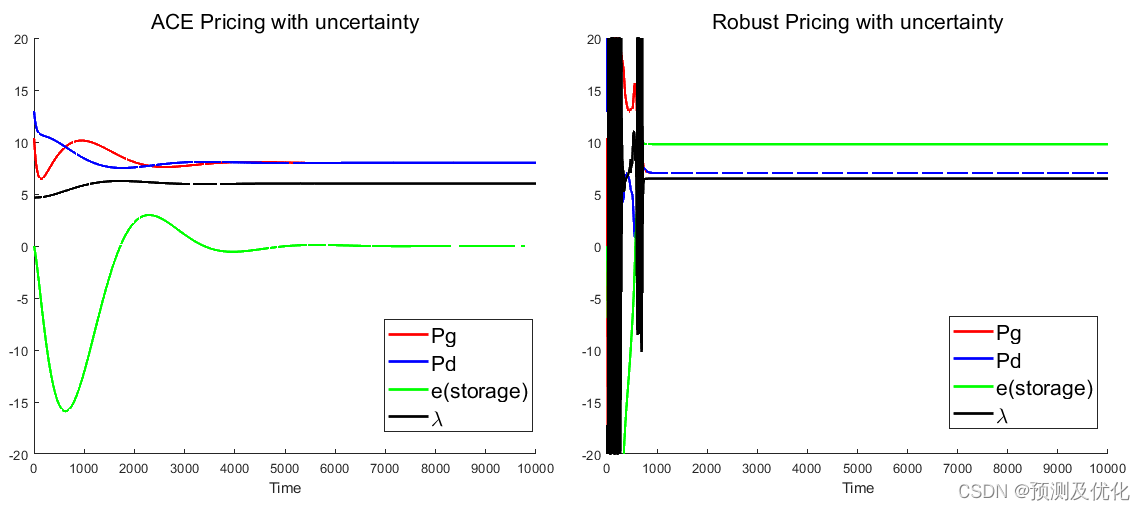

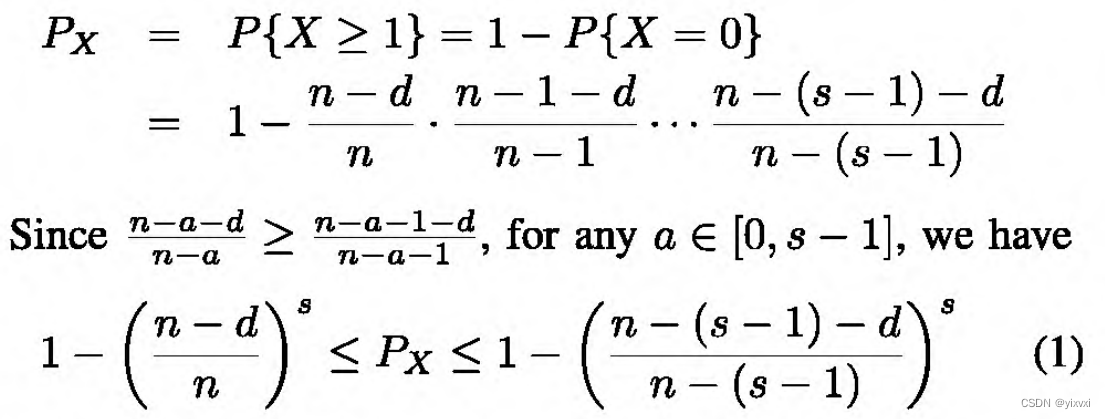

首先,下图是PCIE link training的时候状态机转换图。可以看到equalization有phase0/1/2/3,GEN3/GEN4需要equalization,GEN1/2不需要。原因是GEN3/GEN4速度提上来了,信号在PCB板上传输时更容易出现码间串扰。

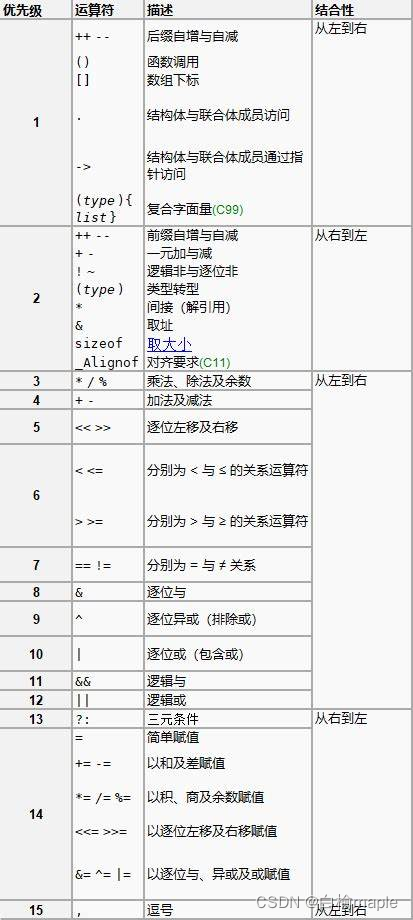

3、Equalization过程

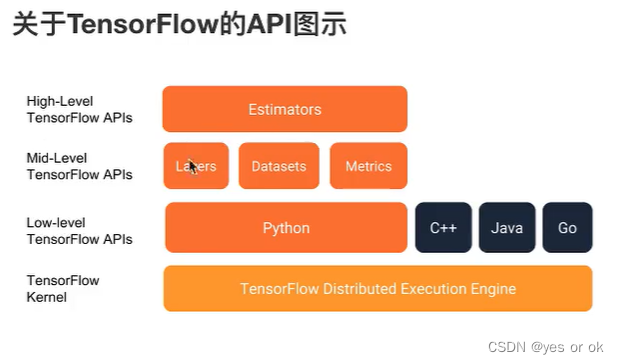

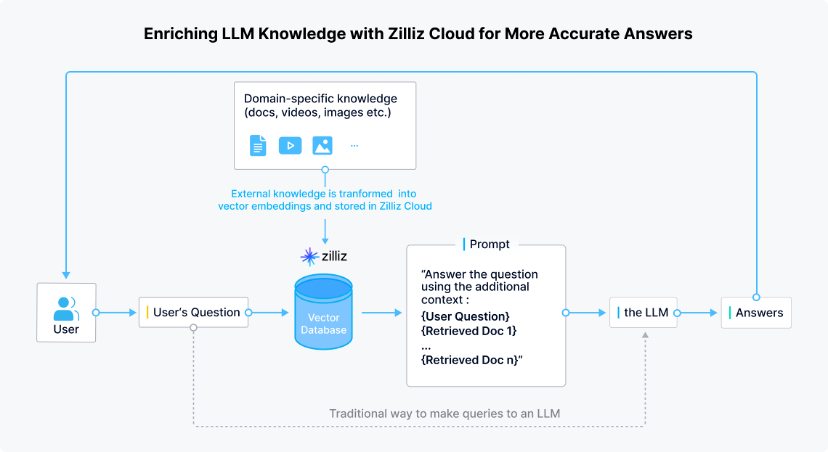

接着,整个均衡的big picture如下图所示:主要有三个均衡器:TX 3-tap FIR; RX 2 Tap DEF和1 order CTLE. Equalization大概的故事剧本是这样的:有两个设备endpoint和root complex.

(1)endpoint的LTTM状态机控制发送TS1给root complex,TS1中包含preset值,preset 值就是TX 3-tap FIR中的tap系数。

(2)root complex的rx端接收到preset值,调节自己tx 3-tap FI